Изобретение относится к вычислительной технике и автоматике и предназначено для использования ВО входных устройствах ЭЦВМ, а также в системах дистанционного управления.

Известно устройство для выравнивания уровней, содержащее элементы «И, «ИЛИ входные триггеры с раздельными входами и блоки развязки, входы которых подключены соответственно к входной шине «1, входной шине «О и шине синхронизирующих импульсов, а выходы к нулевому входу соответствующего входного триггера и к соответствующему входу элемента «ИЛИ, выход первого блока развязки подклю.чен к первому единичному входу второго входного триггера, а выход второго блока развязки - к первому единичному входу первого входного триггера. Однако, если разность между длительностями импульсов информации и иАгпульсов «СИ на входе триггера будет меньше времени срабатывания триггера, схема может потерять работоспособность, поскольку может занять произвольное состояние, и на рабочие триггеры не поступит сигнал сброса. На нормальную работу схемы оказывают влияние также и временные задержки, обусловленные паразитными реактивными параметрами связей и отдельных узлов.

Целью изобретения является повышение

надежности и увеличение быстродействия устройства. В предлагаемом устройстве это достигается тем, что оно содержит счетный триггер, два дополнительных элемента «ИЛИ и дополнительный элемент «И, входы которого соединены с единичньши выходами входных триггеров, а выход - с нулевым входом счетного триггера, счетный вход которого подключен к выходу пе,рвого дополнительного элемента «ИЛИ, а единичный выход - к первому входу второго дополнительного элемента «ИЛИ, второй вход которого подключен к шине сброса, а выход - к единичным входам входных триггеров, первый вход первого дополнительного элемента «ИЛИ связан с первым входом регистра сдвига и выходом первого элемента «И, второй вход связан со вторым входом регистра сдвига и выходом втоiporo элемента «И, первые входы первого и

второго элементов «И подключены к нулевым выходам соответствующих входных триггеров, а вторые и третьи входы объединены и подключены соответственно к выходу элемента «ИЛИ и к нулевому выходу третьего входного триггера.

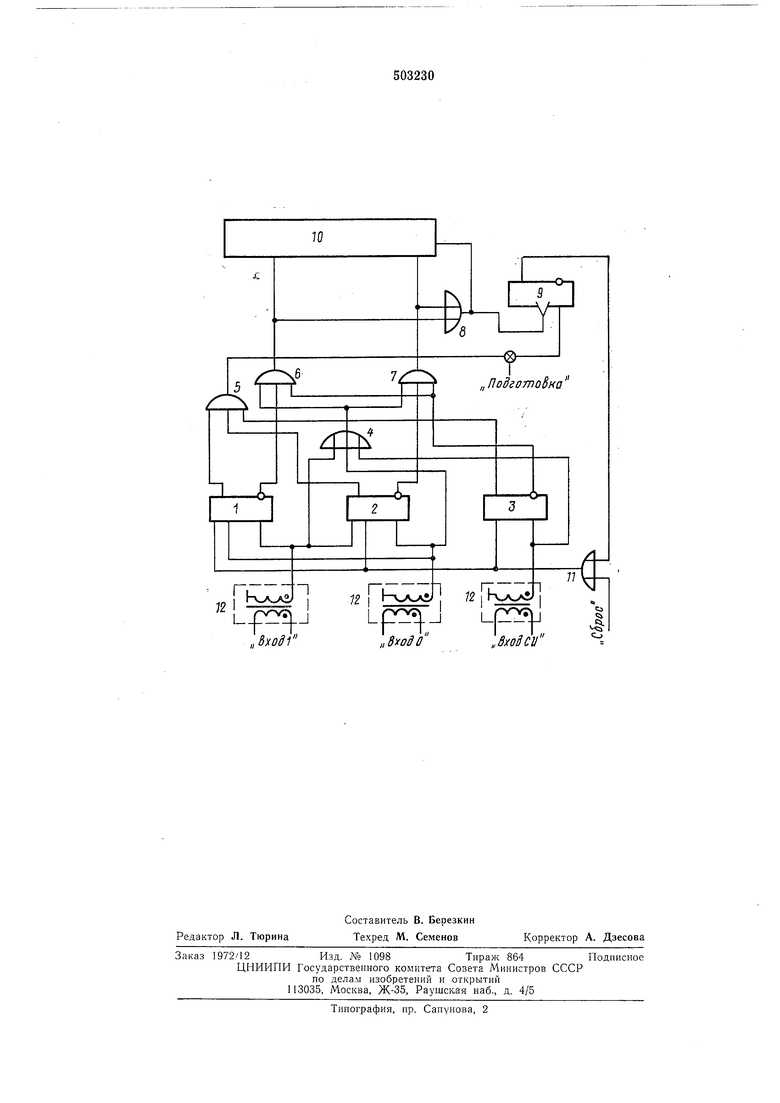

На чертелге представлена функциональная схема предлагаемого устройства.

Оно содержит входные триггеры 1, 2, 3 с раздельными входами, ячейки «ИЛИ 4,

ячейки «И 5, 6, 7 двувходовую ячейку.

«ИЛИ 8, триггер 9 со счетным входом, регистр сдвига 10, ячейку «ИЛИ II и Т рансфо,рматорные гальванические развязки 12.

Для установки схемы в исходное состояние перед началом работы на шину «Сброс подается импульсный сигнал, который поступает на иервый вход ячейки «ИЛИ 11, проходит ее и, поступив на единичные входы входных триггеров 1, 2, 3, устанавливает их в исходное состояние. На единичных выходах триггеров 1, 2, 3 появится уровень, соответствующий «1, который поступит на входы ячейки «И 5. Иа выходе ячейки «И 5 появится высокий потенциал и по шине подготовка поступит на установочный вход триггера 9, устанавливая его в исходное состояние. На нулевом выходе триггера 9 появится уровень, соответствующий «О, который поступит на вход ячейки «ИЛИ И. По окончании поданного на шину «Сброс импульса на выходе ячейки «ИЛИ 11 установится низкий потенциал.

В случае, если первым поступил импульс по шине «Вход 1 («Вход О), т. е. импульсы, поступающие по шине «Вход СИ, отстают от импульсов информации, входной триггер 1 (входной триггер 2) изменит состояние, на его нулевом выходе -появится уровень, соответствующий «1, который будет поступать на вход ячейки «И 6 («И 7). Одновременно на входе ячейки «И 5 появится низкий потенциал, поступающий с единичного выхода входного триггера 1 (входного триггера 2), изменившего состояние, закрывающий эту ячейку и снимающий сигнал начальных условий с установочного входа триггера 9. Одновременно входной импульс поступит и на вход ячейки «ИЛИ 4, а с ее выхода - на входы ячеек «И 6 и «И 7. Цри появлении импульса по шине «Вход СИ, поступающего на нулевой вход входного триггера 3, состояние входного триггера 3 изменится , и на его нулевом выходе появится уровень, соответствующий «1. Одновременно импульс с шины «Вход СИ поступает на вход ячейки «ИЛИ 4. С нулевого выхода входного триггера 3 уровень, соответствующий «1, поступит на входы ячеек «И 6, «И 7. Импульс с выхода ячейки «ИЛИ 4 пройдет через ячейку «И 6 («И 7), так как на двух других входах ячейки «И 6 («И 7) будут уровни, соответствующие «1, и поступит на вход регистра сдвига 10 и на один из входов ячейки «ИЛИ 8, с выхода которой импульс поступит на тактовый вход регистра сдвига 10 и на счетный вход триггера 9. По поступлении заднего фронта импульса на счетный вход триггера 9 изменится его состояние и на его нулевом выходе появится уровень, соответствующий «1, который через ячейку «ИЛИ 11 поступит на единичные входы триггеров 1, 2, 3 и установит их в исходное состояние, т. е. на их единичных выходах появятся уровни, соответствующие «1, которые через

ячейку «И 5 поступят на шину «Подготовка и на установочный вход триггера 9 и установят его в исходное состояние. В этом случае на нулевом выходе триггера 9 появится уровень, соответствующий «О, т. е. установочный сигнал (уровень, соответствующий «1) с единичных входов триггера 1, 2, 3 исчезает.

Устройство готово к приему следующей информации.

Если первым поступает импульс по шине «Вход СИ устройство работает аналогично.

В случае одновременного прихода импульсов по щине «Вход 1 или по шине «Вход О с импульсами, приходящими по шине «Вход

СИ аналогично описанному, произойдет подготовка триггера 9, а после окончания отработки информации триггер 9 подает сигнал по шине «Сброс на входные триггеры 1, 2, 3 задним фронтом импульсов поступающей информации.

Формула изобретения

Устройство для выравнивания логических уровней, содержащее элементы «И, «ИЛИ, входные триггеры с раздельными входами и блоки развязки, входы которых подключены соответственно к входной шине «1, входной

шине «О и шине синхронизирующих импульсов, а выходы - к нулевому входу соответствующего входного триггера и к соответствующему входу элемента «ИЛИ, выход первого блока .развязки подключен к первому единичному входу второго входного триггера, а выход второго блока .развязки - к первому единичному входу первого входного триггера, отличающееся тем, что, с целью повыщения надежности устройства и увеличения его

быстродействия, оно содержит счетный триггер, два дополнительных элемента «ИЛИ и дополнительный элемент «И, входы которого соединены с единичными выходами входных триггеров, а выход - с нулевым входом счетного триггера, счетный вход которого подключен к выходу первого дополнительного элемента «ИЛИ, а единичный выход - к первому входу второго дополнительного элемента «ИЛИ, второй вход которого подключен к шине сброса, а выход - к единичным входам входных триггеров, первый вход первого дополнительного элемента «ИЛИ связан с первы.м входом регистра сдвига и выходом первого элемента «И, второй вход связан со вторым входом регистра сдвига « выходом второго элемента «И, первые входы первого и второго элементов «И подключены к нулевым выходам соответствующих входных триггеров, а вторые и третьи входы объединены и подключены соответственно к выходу элемента «ИЛИ и к нулевому выходу третьего входного триггера.

„

tj

р-р

I

I II

„BxoiCV

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления шаговым двигателем | 1972 |

|

SU514411A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Парафазный сдвигающий регистр | 1976 |

|

SU739654A1 |

| Устройство для задержки импульсов | 1982 |

|

SU1077046A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Устройство для управления шаговым двигателем | 1983 |

|

SU1091295A1 |

| Преобразователь двоичного кода в число-импульсный код | 1977 |

|

SU734671A1 |

| Устройство для задержки импульсов | 1979 |

|

SU805483A1 |

| Устройство сдвига цифровой информации | 1977 |

|

SU656107A2 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

Авторы

Даты

1976-02-15—Публикация

1973-10-23—Подача