Изобретение относится к вычислительной технике и может найти применение в различного типа счетно-решающих устройствах, системах и приборах автоматического контроля, регулирования, а также в других системах, осуи.1ествляю дих преобразование дискретной информации.

По основному авт. сеид. № 553683 известно устройство, содержащее две группы регистров, состоящих из последовательно включенных триггеров, входы каждого из которых соединены с выходом предыдущего триггера через вентили, вторые входы которых соответственно соединены с первой и второй щинами синхроимпульсов, первые входы вентилей первых триггеров обеих групп регистров - с прямым и инверсным выходами триггера с раздельными входами, а счетный вход счетного триггера через элемент ИЛИ подключен ко входам триггера с раздельными входами, причем выходы этого триггера соединены с первыми входами элемента И, вторые входы которых подключены к счетному входу счетного триггера, а выходы - к шинам синхроилшульсов. Кроме того, устройство содержит два выходных элемента ИЛИ и по два элемента И на калчдый регистр. Первые входы каждой пары элементов И подключены к первой и второй шина.м синхроимпульсов соответственно,

5. вторые их входы - к единичному и нулевому выходам триггера последнего разряда каждого регистра, а выходы - к первым и вторым входам первого и .второго элементов ИЛИ соответственно. Выходы первого и втоQ рого элементов ИЛИ подключены соответственно к единичной и нулевой выходным щинам.

Однако такое устройство не может автоматически переходить от режима записи к режиму считывания преобразованного кода. Оно не работоспособно при одновременном приходе сигналов записи считывания, а также не может автоматически управлять количеством поступивших разрядов, и любая помеха на входе устройства в режиме

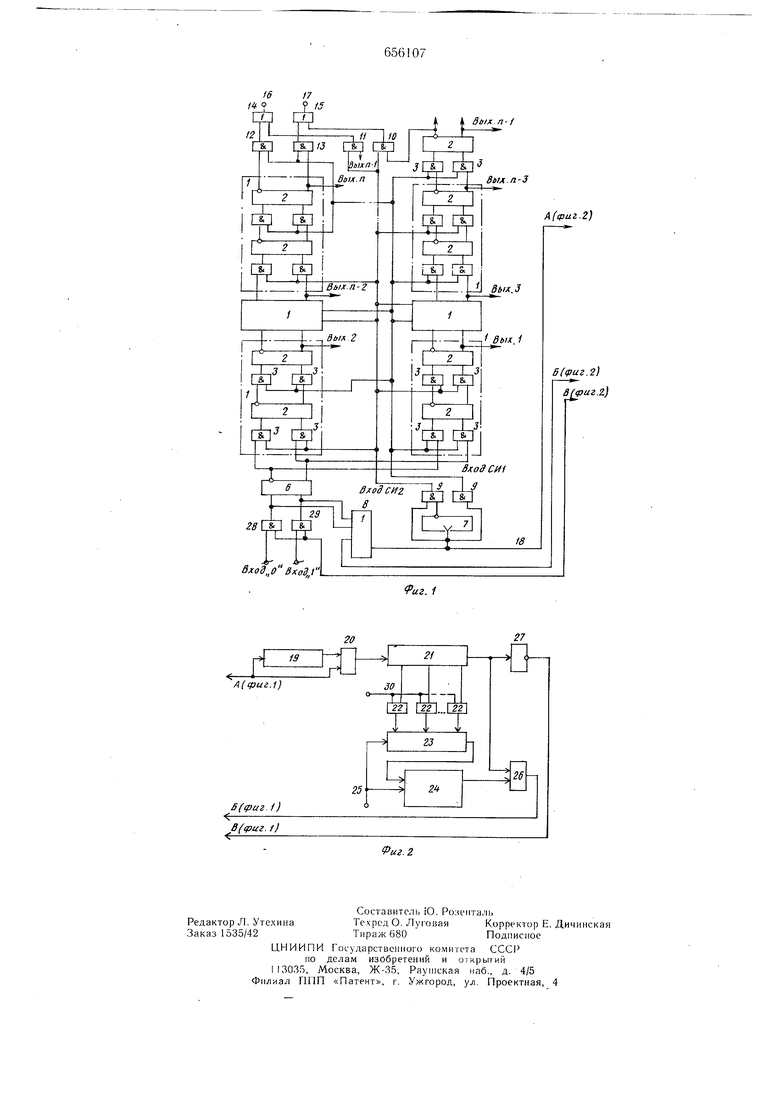

0 заниси или считывания воспринимается как основной сигнал, полностью искажающий преобразуемую устройством информацию Это снижает надежность и ограничивает функциональные возможности устройства. Мелью из(1бретения является повышение надежноети устройства сдвига цифровой информации. Поставленная цель достигается тем, что цредложеиное устройство сдвига цифровой информации содержит инвертор, счетчик адресов, блок разрешения считывания, счетчик слов, регистр слов, два элемента И и две групны элементов И, первые входы которых подключены к выходу инвертора. вход которого соединен с выходом счетчика с/мов и первым входом первого элемента И, выход которого подключен к дополнительному входу элемента ИЛИ, а второй вход первого элемента И подключен к выходу блока разрешения считывания. Первый вход блока разрешения считывания и вход сдвига регистра слов соединены с шиной считывания устройства. Выход регистра слов подсоединен ко второму входу блока разрешения считывания, а выход элемента ИЛИ подключен ко входу счетчика адресов и первому входу второго элемента И, второй вход которого подключен к выходу счетчика адресов. Выход второго элемента И подключен ко входу счетчика слов, разрядные выходы которого подключены к информационным входа.м регистра слов через элементы И первой группы, вторые входы которых подключены ко входу «запись. Выходы элементов И второй группы подключены ко входам триггера с раздельными входами, а вторые входы - к соответствующим инфор.мационпым входам устройства. На фиг. 1 и фиг. 2 приведена функциональная схема устройства. Устройство содержит два регистра сдвига, состоящие из разрядных групп 1, каждая из которых содержит последовательно включенные триггеры 2, входы каждого из которых соединены с выходом предыдущего триггера через вентили 3. Вторые входы вентилей 3 поочередно подключены к первой шине 4 синхроимпульсов (СИ1) и второй шине 5 синхроимпульсов (СИ2). Первые входы вентилей 3 первых триггеров 2 первых разрядных групп регистров соединены с прямым и инверсным выходами триггера 6 с раздельными входами. Устройство содержит также триггер 7 со счетным входом, счетный вход которого соединен со входами триггера 6 через элемент ИЛИ 8, а выходы - с первыми входами элементов И 9, вторые входы которых подключены к счетному входу триггера 7, а выходы - к шинам синхроимпульсов 4 и 5 соответственно. Шипа 4 соединена с первыми входами единичного 10 и нулевого 11 элементов И выделения импульсов выходного кода первого регистра сдвига, а шина 5 - с первыми входами единичного 12 и нулевого 13 элементов И выделения импульсов выходного кода второго регистра сдвига. Вторые входы этих элементов и соответственно соединены с единичным и нулевым выходами триггеров 2 последних разрядов групп регистров, а выходы элементов И 12, 10 и элементы 11, 13 через соответствующие выходные элементы ИЛИ 14, 15 подключены к выходным шинам 16 (выход «1) и 17 (выход «О) соответственно. Вход триггера 7 соединен с шиной выходных сопровождающие импульсов 18. В устройство введены .также счетчик адресов, 19, соединенный через первый элемент И 20 со входом счетчика 21, разрядные выходы которого подключены через элементы И первой группы 22 к информационным входам регистра 23 слов, вход сдвига которого подключен к первому входу блока 24 разрешения считывания и шине 25 считывания. Выход регистра 23 слов соединен со вторым входом блока 24 разрешения считывания, выход которого подключен через второй элемент И 26 к дополнительному входу элемента ИЛИ 8. Выход счетчика 21 соединен со вторым входом второго элемента И 26 и через инвертор 27 подключен к объединенным входам элементов И второй группы 28, 29, вторые входы которых соответственно соединены с инфор.мационными входами устройства (вход «О и вход «1). Вторые входы элементов И первой группы объединены и соединены со входом 30 «запись устройства. Устройство работает следующим образом. В начальный момент времени все элементы схемы находятся в исходном состоянии. На выходе счетчика слов присутствует нулевой уровень, который через инвертор разрешает прохождение информации через элементы И второй группы, т. е. при подаче входной информации на вход устройства первый синхроимпульс СИ1 переписывает инфор.мацию на первый триггер 2 (правого) регистра сдвига. При поступлении второго значения входной информации она переписывается далее на триггеры 2 (левого) регистра сдвига вторым синхроимпульсом СИ2, который одновременно продвигает по эле.ментам первого регистра предыдущую информацию. Следующий синхроимпульс СИ1 переписывает входную информацию в следующий разряд первого регистра, а следующий за СИ1 синхроимпульс СИ2 записывает в разряды второго регистра следующий разряд информации и продвигает информацию в разрядах первого регистра. Благодаря перекрестному соединению входов СИ1 и СИ2 и каждого из разрядов первого и второго регистров сдвига информация аналогично сдвигается в следующие ряды так, чтобы нечетные ее значения находились в первом регистре, .а четные - во втором. Сдвиг информации производится аналогично вводу. При записи парафазного кода в качестве синхроимпульсов используется входной код. Для этого собранные элементом ИЛИ 8 входные сигналы поступ-ают на вход триггера 7, который срабатывает по их заднему фронту, а выходные элементы И 9 формируют на шинах 4, 5 сигналы для сдвига и ввода входных сигналов в регистр. Входные сигналы могут иметь при повышенных требованиях к быстродействию малую длительность, т. е. до появления синхроимпульсов СИ1 и СИ2. Для исключения этого во входных триггерах 6 производится промежуточное запоминание входной информации. Одновременно счетчик адресов 19 ведет счет сигналов входной информации, и при достижении заданного значения последний импульс каждой «пачки, проходя через первый элемент И, прибавляется к содержимому счетчика 21. При заполнении этого счетчика на первый вход второго элемента И 26 подается разрешающий сигнал, после чего схема переходит в режим считывания. Переход от режима записи инфор.мации в режим считывания сопровождается переходными процессами, определяющи.мися переключением с одного режима на другой. В этом случае на шине 25 считывания появляются ненормированные сигналы помехи, KOTOpbie поступают на вход регистра 23 слов, который, запоминая их, по сигналу «Запись на входе 30 принимает по информационным входам содержимое счетчика 21 через первую группу элементов И 22 и затем определенное количество импульсов (/iiwn) считывания по шине 25, которое определяется следу юшим выражением Пимп - Лс.п Лрс.ч.с, где Лс.п-число сигналов помехи; Жр-число разрядов регистра 23; .чс-число разрядов счетчика 21 числа слов. Одновременно с достижением заданного значения на счетчике 21 на его выходе вырабатывается единичный уровень, который через инвертор 27 закрывает элементы И 28, 29, а блок 24 разрешения считывания после анализа заданного значения счетчика 21 разрешает через второй вход элемента И 26 и дополнительный вход элемента ИЛИ 8 прохождение сигналов считывания. Для обеспечения выдачи хранимой в регистрах инфор.мации в последовательном парафазном коде и других операций импульс считывания в зависимости от состояния триггеров 2 последних разрядных групп при помощи элементов И 10 и 11 выделения импульсов выходного последовательного кода через элементы ИЛИ 14 и 15 формирует на выходах устройства импульс выходного кода. Следующий импульс считывания аналогично через элементы И 12 и 13 выделения импульсов последовательного кода и соответствуюи,ий элемент ИЛИ 14 и 15 сформирует на выходе устройства второй импульс последовательного кода, соответствующий по своему значению второму импульсу кода. записанному в устройстве в предыдущем цикле ввода информации. В дальнейшем устройство работает аналогично. Предложенное устройство работоспособно при одновременном приходе сигналов записи и считывания, а наличие регистра количества слов с элемента.ми И и блока разрешения считывания исключает искажение преобразуемой информации, что повышает надежность работы устройства. Формула изобретения Устройство сдвига цифровой информации по авт. свид. 553683, отличающееся целью повышения надежности тем, что, устройства оно содержит инвертор, счетчик адресов, блок разрешения считывания, счетчик слов, регистр слов, два элемента И и две группы элементов И, первые входы которых подключены к выходу инвертора, вход которого соединен с выходом счетчика слов и первым входом первого элемента И, выход которого подключен к дополнительному входу элемента ИЛИ, а второй вход первого элемента И подключен к выходу блока разрешения считывания; первый вход блока разрешения считывания и вход сдвига регистра слов соединены с шиной считывания; выход регистра слов подсоединен ко второму входу блока разрещения считывания, а выход элемента ИЛИ подключен ко входу счетчика адресов и перво.му входу второго элемента И, второй вход которого подключен к выходу счетчика адресов; вы.ход второго элемента И подключен ко входу счетчика слов, разрядные вы.ходы которого подключены к информационным -входам регистра слов через элементы И первой группы, вторые входы которых подключены ко входу «запись, выходы элементов И второй группы подключены ко входам триггера с раздельными входами, а вторые входы элементов И второй группы соединены с соответствующими информационными входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1981 |

|

SU1015443A1 |

| Устройство сдвига цифровой информации | 1975 |

|

SU553683A1 |

| Устройство сдвига цифровой информации | 1972 |

|

SU476601A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

Авторы

Даты

1979-04-05—Публикация

1977-10-24—Подача