(54) ПАРАФАЗНЫЙ СДВИГАЮЩИЙ РЕГИСТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сдвига цифровой информации | 1977 |

|

SU656107A2 |

| Устройство для считывания графической информации | 1980 |

|

SU932517A1 |

| Устройство сдвига цифровой информации | 1975 |

|

SU553683A1 |

| Устройство для управления шаговым двигателем | 1972 |

|

SU514411A1 |

| Устройство для обнаружения потери импульса | 1989 |

|

SU1709509A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Устройство для воспроизведения информации слепым | 1983 |

|

SU1191931A1 |

| Регистр сдвига | 1975 |

|

SU666583A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Устройство для сдвига цифровой информации | 1976 |

|

SU660047A1 |

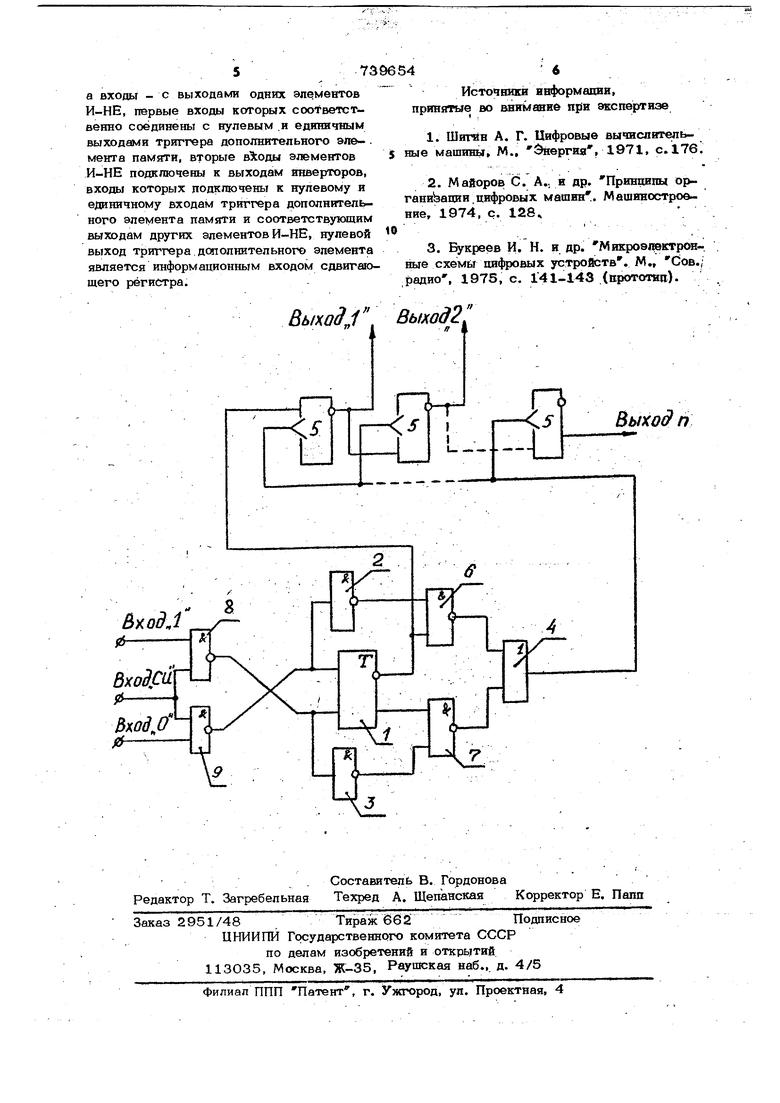

Изобретение предвазначено дпя испопь I зования в счетно-решающих устройствах, ycTjpoftcTBax автоматикии ивформациовнризмерительнрй техники, а также в различ ных устройствах приема и передачи даскретных сообщений. Известны парафазвые с/шнгаюшие реги стры, содержшаие последовательно соединенные элементы памяти ва триггерах с объединенными счетными входами, к которым подключена шнва сдвига f) и ;. Одншсо этэд устройства сложны и ненадеж ны, что вызвано большим количеством элементов и сложной структурой схемы сдвига. Наиболее близким к предложенному регистру по технической сущности являн ется пара азный сдгаггающий регистр, сор/држешгА последовательно соединенные через элементы И-НЕ элементы памяти 1иа Триггерах с. объединенным и счетными входами. Выходы элементов И-НЕ в ука.занном уст|к йстве соединены с единичными и нулевыми входами.соответствую щих триггеров, а входы - с выкоаамя триггеров, причем вторые входьт элементов И-НЕ подключены к шине тактовых импульсов з . Недостатки известного парафазного регистра заключаются в том, что он имеет большее число информационных входов, требует применения тактовых импульсов, а Также специального устррйства формирования этих импульсов с обязательной временнЬй привязкой к диаграмме поступления входного парафазного кода. Цель изофетёнйй - повышение наде ности устройства и его быстродействия. Это достигается тем, что в парафазный сдвигающий регистр, содержащий последовательно соеданенные эпементы памяти на триггерах с объединенными счетными входами и элементы И-НЕ, дополнителыго введены эле-менты памяти на триггере, и эпемевт ИТМ, выход которого соединен со счетными входами триггеров, а входа - с выходами одних элементов И-НЕ, первые входы которых соответственHO соединены с нулевым и едини5.нь1М„выходами триггера дополнительного элемент памяти, вторые входы элементов И-НЕ подкпючень к выходам инверторов, входы которых подключены к нулевому и единичному входам триггера дополнительного 9лё1«гёнта памяти .и соответствующим выхо дам. других элементов И-НЕ, при этом нулевой выход триггера дополнительного элемента цвляется информационным входом сдвигающего регистра. На чертеже представлена функциональ-. ная схема парафазного сдвигающего регисТра. . , Парафазный сдвигающий регистр с одержит дополнительный элемент 1 памяти на триггере, инверторы 2 и 3, элемент ИЛИ 4, последовательно соединенные элементы 5 памяти на триггерах с объединенными счетными входами и элементы И-НЕ 6,7, 8,9. Единичный и нулевой входы дополнительйогоэлемента 1 памяти на триггере соответственно через инверторы 2 и 3 одни из элементов И-НЕ 6,7 и элемент ИЛИ соединены со счеТными входами триг геров элементов 5 памяти и с выходами соответствугацих других элементов И-НЕ 8,9. Е торые входы одних элементов И-НЕ 6-,7 подключены к нулевому и единичному выходам триггера : дополнительного элемента 3. памяти, а нулевой выход этого триггера - к информационнбму входу сдвигающего регистра. Парафазшй сдвигающий регистр работает следующим образом. . При поступлении импульсов парафазного кода на единичный вход или нулевой вход О и вход сопровождающих импульсов (вход СИ) открывается соответствующий элемент. И-НЕ 8 или 9 и дополнительный элемент 1 памяти на триггере устаноштс я в с оотвеТствукщеё Пол{ жение О или 1. Например, при поступ лении импульса йа йхЬд I и сопровождающего импульса на вход СИ триггер дополнительного элемента 1 памяти уста нрвится в положение . В этом случае на информационный вход сдвигающего регистра будет поступать соответствующий уровень с нулевого плеча названного триггера. После установки триггера дополритепьного элемента 1 памяти в состояние разрешается прохождение сигнала через элемент И-НЕ 7, на второй вход которого через инверторов по- : ступает сигнал с единичного входа триг гера. В этом случае элемент И-Н1Е 7 формирует на своем выходе Сигнал, который, поступая на объединенные Счбт7344 ные входь триггеров последовательно со-, единенных элементов 5 памяти, запишет информацию с информационного входа на первый триггер элемента 5 памяти. Сдвигающий сигнал на выходе элемента ИЛИ 4 Возникает только после установки триггера дополнительного элемента 1 памяти в состояние и записи этой информации в первый элемент 5 памяти. Это, а также то, что сдвиг информации происходит задним фронтом инпульса, соверщенно исключает влияние разбросов временных характеристик элементов схемы на ее нормальную работу. Аналогично при поступлении нулевого значения парафазного кода на вход О и сопровождшощего синхроимпульса на вход СИ триггер дополнительного элемента 1 памяти через элемент И-НЕ 9 установится в состояние 0 , и на информационной щине установится соответствующий уровень. Как и в первом случае только после установки триггера дополнительного элемента 1 памяти в состояние О при помощи инвертора на выходе элемента И-НЕ 6 будет .формироваться сигнал, который через элемент ИЛИ 4 запнщет нулевую информацию в первый, элеме.нт 5 памяти, сдвинув прежде записанную в нем информацию во второй разряд (элемент 5 памяти) регистра. , :: , Далее работа устройства проибходиТ аналогично Описанному до полного заполнения всех последовательно соединенных элементов 5 пшяти. Запоминание информации на триггере дополнительного элемента 1 памяти позв оляет при малых длительностях входных сигналов значительно повысить быстродействие и надежность схемы, а совместное включение этого триггера с инверторами 2,3, элеме ггами И-НЕ 6,7 и ИЛИ 4 позволяет принять параф азный код на обычный однофазный сдвигающий регистр, Входные элементы И-НЕ 8,9 в совокупности с указанными элементами осуществляют защиту- устройства от помех, возникающих во входнь1х линиях связи, формула изобретения Парафазный сдвигающий регистр, содержащий последовательно соединенные эле- менты памяти на триггерах с объединенными счетными входами и элементы И-НЕ, от л и ч ающ и и с я тем, что, с цёпыо эвыщения .надежности устройства и его быстродействия, он содержит дополнител1зный элемент памяти на триггере, инверторы и йлёмент ИЛИ, выход которого соединен со счетными входами триггеров.

а входы - с выходами одних элементов , первые входы которых соответственно соединены с нулевым ,и единичным выходами триггера дополнительного эле- . мента памяти, вторые элементов И-НЕ подключены к выходам инверторов, входы которых подключены к нулевому и единичному входам триггера дополнительного элемента памяти и соответствующим выходам других элементов И-НЕ, нулевой выход триггера дополнительного элемента является информационным входом сдвигающего регистра.

Выкод„1 Выход2 В(оВЛ Bxoicd ,

Источники информации, принятые во внимание экспертизе

Авторы

Даты

1980-06-05—Публикация

1976-01-09—Подача