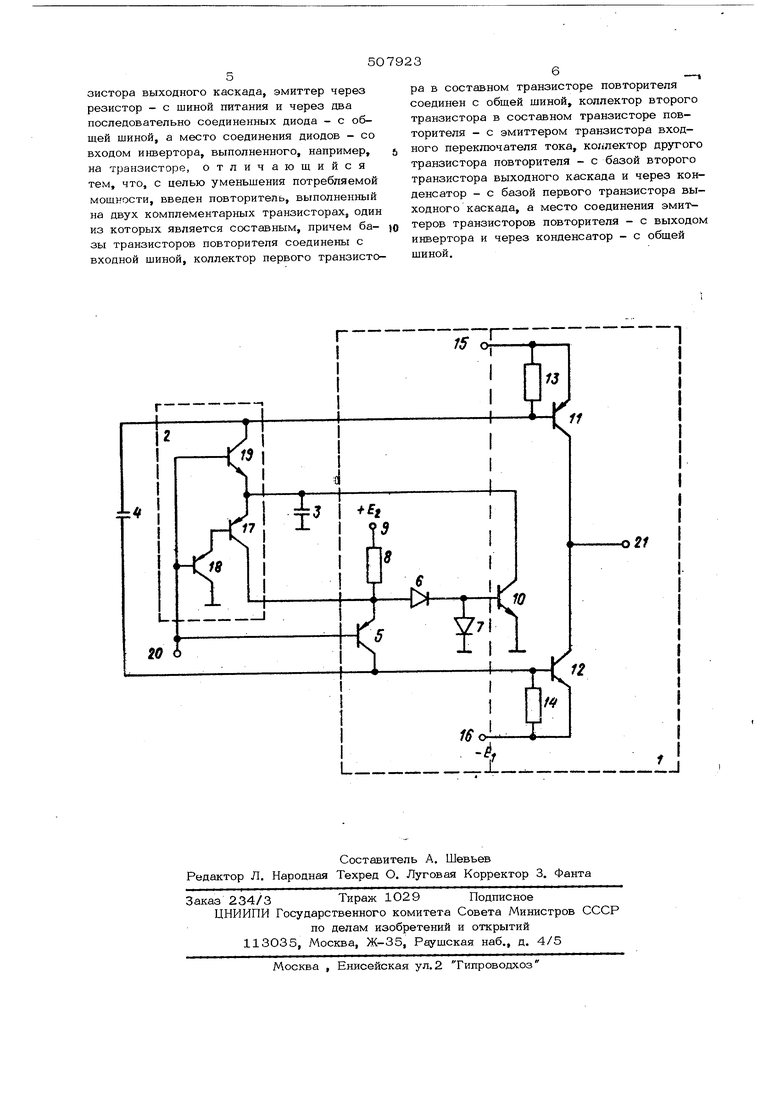

:54) ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКИХ УРОВНЕЙ выходом повторителя 2, является форсирующим, а конденсатор 4 - разделительным. Входной переключатель тока выполнен на транзисторе 5, диодах G, 7 и резисторе 8, который соединяет эмиттер транзистора 5 с шиной питания 9. Место соединения диодов О и 7 присоединено ко входу инвертора, выполненного па транзисторе I О. Выходной каскад блока формирования уров ней 1 содержит комплементарные транзисторы 11, 12 и резисторы 13, 1-1. Эмиттер транзистора 11. соединен с шиной питаш-гя 1 5, а эмиттер транзистора 1 2 - с шиной питания 16. Повторитель 2 содержит транзисторы 17 и 18, включенные по схеме составного зистора, и транзистор 19. Базы транзисторров 5, 18 и 19 соединены с входной шиной 20, а выходная шина 21 - с местом соединения транзисторов 11 и 12. Преобразователь логических уровней работает следующим образом. При низком уров не сигнала (О-О,3 в) на входной шине 20 преобразователя логических уровней в проводящем состоянии находится транзистор 5 переключателя тока. Ток коллектора транзистора 5, определяемый резистором 8, открывает транзистор 12 выходного каскада и на выходной шине 21 преобразователя устанавливается напряжение, почти равное на- лряжению на шине питания 16. Все остальные транзисторы закрыты. Если уровень сигнала на входной шине2О преобразователя высокий ( 2 в), то транзистор 5 переключателя тока закрыт, ток через резистор 8 течет в диоды 6 и 7. При этом ток инвертора 10 через транзистор 19 повторителя 2 поступает в базу транзистора 1 1 выходного каскада 1 и включает его. Напряжение на выходе преобразователя будет близким к напряжению на шине питания 15. Во время действия фронтов входного сигнала перезаряжается форсирующий конденсатор 3. Для положительного фронта конденсатор 3 заряжается током эмиттера транзистора 1 9 повторителя 2. Следовательно, его коллекторный ток и ток базы транзистора 11 выходного каскада во время положительного фронта входного сигнала значительно превышает эти точки в установившемся состоянии. Этим обеспечивается форсированное переклю-55

чение транзистора 11 из закрытого состояния в открытое и приводит к резкому увеличению крутизны положительного фронта выходного сигнала преобразователя логических уровней.

торы которых соединены с выходной шиной, а эмиттеры - с шинами питания, и диодный переключатель тока, выполненный на транзисторе, база которого соединена с входной шиной, коллектор - с базой первого тракДля отрицательного фронта, до тех пор, пока входной сигнал не достигает порога срабатывания, конденсатор 3 заряжается током эмиттера транзистора 17 и одновременно током инвертора 1О, поскольку ток коллектора транзистора 17 поступает в диоды в и 7 переключателя тока преобразователя. Транзистор 5 переключателя тока закрыт до тех лор, пока напряжение на входной шине 20 преобразователя логических уровней не станет равным порогу срабатывания схемы - напряжению на диодах 6 и 7. При дальнейшем уменьшении напряжения на входной шине 20 ток разряда конденсатора 3 и, следовательно, коллекторный ток транзистора 17 переключается втранзистор 5, а транзистор 12 (юрсцронанно включается. Транзистор 18 не допускает насыщения транзистора 17 составного повторителя 2, обеспечивает максимальную скорость передачи его эмиттерного тока и в то же время снижает требование к нагрузочной способности каскада управления преобразователем логическим уровней. Особенностью режима форс ирования является то, что форсирование является нелинейным. Форсирование на положительном фронте происходит лищь после того, как откроется транзистор 19 составного повторителя 2. Форсирование на отрицательном фронте происходит только в том случае, когда сигнал на входе достигнет порогового напряжения. Таким образом, форсирование переключения преобразователя логических уровней не ухудшает помехоустойчивости схемы и в то же время позволяет выбрать токозадающий резистор 8 достаточно высокоомным для сокращения потребляемой мощности в исходном состоянии схемы. Конденсатор 4, включенный между базаи выходных транзисторов 11 и 12, слуит для передачи крутых фронтов сигналов баз открывающихся транзисторов на базы акрывающихся транзисторов, что сокращает ремя включения тока закрывающихся транисторов. Формула изобретения Преобразователь логических уровней, соержащий выходной каскад, выполненный на двух комплементарных транзисторах, коллекзистора выходного каскада, эмиттер через резистор - с шиной питания и через два последовательно соединенных диода - с общей шиной, а место соединения диодов - со входом инвертора, выполненного, например, на транзисторе, отличающийся тем, что, с целью уменьщения потребляемой мощности, введен повторитель, выполненный на двух комплементарных транзисторах, один из которых является составным, причем базы транзисторов повторителя соединены с входной шиной, коллектор первого транзистора в составном транзисторе повторителя соединен с общей шиной, коллектор второго транзистора в составном транзисторе повторителя - с эмиттером транзистора входного переключателя тока, коллектор другого транзистора повторителя - с базой второго транзистора выходного каскада и через конденсатор - с базой первого транзистора выходного каскада, а место соединения эмиттеров транзисторов повторителя - с выходом инвертора и через конденсатор - с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь логических уровней | 1987 |

|

SU1466004A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| ФОРМИРОВАТЕЛЬ РАЗНОПОЛЯРНЫХ ПАЧЕК ИМПУЛЬСОВ | 2005 |

|

RU2287894C1 |

| Стабилизированный источник питания | 1974 |

|

SU530406A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ | 1990 |

|

RU1748611C |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

| Преобразователь логического уровня | 1979 |

|

SU786006A1 |

| Согласующее устройство | 1976 |

|

SU736376A1 |

| Ячейка временной задержки импульсов | 1980 |

|

SU945967A1 |

Авторы

Даты

1976-03-25—Публикация

1974-12-12—Подача