Изобретение относится к устройствам импульсной и цифровой техники, в частности к интегральным логическим элементам БИС и ЭВМ.

Фундаментальной проблемой разработки элементной базы БИС и ЭВМ является увеличение уровня интеграции, снижение мощности потребления логических элементов (ЛЭ), увеличение их нагрузочной способности (на обоих фронтах переключающего сигнала), достижения высокого системного быстродействия в компоновочном пространстве БИС с учетом достаточно длинных линий связи. Переход к субмикронным и глубокосубмикронным технологиям позволяет резко снизить размеры и рабочие площади ЛЭ, увеличить их внутреннее, "технологическое" быстродействие, однако проблема увеличения системного быстродействия при дальнейшем снижении статической мощности потребления остается критической для перспективных ЛЭ биполярных ультраБИС (УБИС).

Главным ограничением биполярного направления развития биполярных СБИС и УБИС на наиболее быстродействующих элементах ЭСЛ и непороговой логики на эмиттерных повторителях (ЭПЛ) было значительное потребление статической мощности, балластный характер которой в отличие от КМОП элементов проявлялся в режиме покоя или непереключения ЛЭ. Эта балластная статическая мощность сильно нивелировала возможности достижения высокого быстродействия на масштабированных биполярных транзисторах с разными типами проводимости (комплементарными: n-p-n и p-n-p) с предельно сжатыми вертикальными и горизонтальными размерами: 1) максимальное технологическое (внутреннее, в режиме кольцевого генератора) быстродействие приборов и элементов с минимальными задержками около 10 пс; 2) максимально высокая нагрузочная способность выходных элементов со схемотехникой эмиттерных повторителей по одному фронту и аналогичных комплементарных двухтактных схем по обоим фронтам, характеризующихся, однако, высокой статической мощностью потребления.

Известно, что есть ряд цифровых устройств, которые можно выполнить только с использованием логик И, ИЛИ, И-ИЛИ или с доминирующим преобладанием данной логики с минимальным количеством инверсных элементов НЕ. При этом возможен значительный выигрыш в быстродействии, потребляемой мощности и других технических характеристиках для данного класса схем по сравнению с реализациями на стандартных ЛЭ И-НЕ, ИЛИ-НЕ. Следовательно, актуальность разработки высококачественных неинвертирующих ЛЭ не потеряла своего значения, использование ограниченного количества инверторов на выходе или входе сможет только значительно расширить функциональные возможности более гибких ЛЭ.

Имеется ряд схемотехнических решений многовходовых ЛЭ без инверсий, реализующих функции И, ИЛИ, содержащих параллельно включенные входные однородные эмиттерные повторители (на транзисторах одного типа проводимости) и выходные пороговые схемы [1]. Известно также, что эмиттерные повторители обеспечивают максимально высокое быстродействие по активному фронту для малых и значительных емкостных нагрузок среди всевозможных биполярных схемотехник. Однако в таком ЛЭ возникает необходимость в использовании специальной схемы - непорогового восстановителя уровня на дополнительных (комплементарных) повторителях, а также, возможно, пороговой схемы-транслятора и восстановителя логических уровней (в свою очередь потребляющей дополнительную статическую мощность). Более того, из-за значительных токов в эмиттерных повторителях, особенно на пассивном фронте, для обеспечения приемлемого системного быстродействия потребляется значительная балластная статическая мощность, что делает невозможным использование таких ЛЭ в УБИС при воздушном охлаждении.

В ЭПЛ элементах (изделия фирм TRW, Hitachi и др.) на неоднородных входных и выходных эмиттерных повторителях на транзисторах разного типа проводимости [2] , хотя и сохраняется выполнение логик И, ИЛИ, но из-за потери логического сигнала в длинных цепочках также необходимо ставить восстановители-формирователи логических уровней, что приводит к избыточным балластным потреблениям статических мощностей. При этом не реализуется возможность получения высокой нагрузочной способности в динамике по обоим фронтам и возникают значительные потери системного быстродействия в интегральных системах со значительными емкостными нагрузками для достаточно длинных линий связи.

Наиболее близок к предлагаемому техническому решению фрагмент непорогового ЛЭ И (И-ИЛИ) [3], содержащий входные эмиттерные повторители на транзисторах первого типа проводимости, согласующие повторители на транзисторах второго типа проводимости, формирующий переключатель тока и выходной многоэмиттерный повторитель на транзисторах первого типа проводимости, причем у входных транзисторов первого типа проводимости коллекторы соединены с шиной первого питания (или общей шиной), базы - с соответствующими входами, а эмиттер - с базой согласующего транзистора второго типа проводимости и коллектором транзистора первого типа проводимости первого генератора тока, эмиттер согласующего транзистора соединен со вторым транзисторным генератором тока.

В качестве относительных недостатков данного комплементарного ЛЭ отметим следующие. Использование дополнительной формирующей схемы переключателя тока приводит к дополнительным потерям быстродействия и возрастанию мощности потребления. Даже использование выходного эмиттерного повторителя позволяет получить высокую нагрузочную ЛЭ только на активном фронте переключения, на пассивном же необходимо увеличивать мощность потребления при работе на значительные емкостные нагрузки. Проблема малокомпонентного синтеза логического элемента И (ИЛИ) из комплементарных повторителей без формирующего и выходного каскадов при работе на значительные емкостные нагрузки представляется первоочередной и будет решена и проанализирована в рамках заявляемого объекта устройства.

Для повышения степени интеграции и быстродействия перспективных биполярных ЛЭ УБИС, конкурентных КМОП элементам, требуются схемотехнические решения двухтактных ЛЭ на масштабированных в область глубокого субмикрона и даже наноразмеров биполярных структурах с минимальными геометрическими размерами без балластных площадей, увеличивающих внутренние барьерные емкости и работающих при малых статических токах (а также при малых напряжениях питания. А именно, требуются двухтактные комплементарные биполярные ЛЭ на эмиттерных повторителях, обеспечивающие высокую нагрузочную способность на обоих фронтах переключающего сигнала при малой потребляемой мощности низковольтовых микромощных быстродействующих ЛЭ.

Задачей изобретения является создание сверхмикромощных малокомпонентных логических элементов И, ИЛИ, формирователя- повторителя, работающих на значительные емкостные нагрузки на комплементарных транзисторах различного типа проводимости, обеспечивающих: 1) низковольтный логический перепад в субполувольтовом диапазоне вплоть до 0.2 В при высочайшей нагрузочной способности по обоим фронтам, 2) приемлемые формирующие свойства работы непорогового ЛЭ, 3) высокое технологическое и системное быстродействие элемента, 4) малокомпонентность ЛЭ для плотно упакованных УБИС. Дополнительными целями, ставящими достижение сверхмикромощности и сверхбыстродействия УБИС на заявляемых биполярных ЛЭ, является: создание двухтактной схемы ЛЭ на комплементарных эмиттерных повторителях, позволяющей помимо увеличения системного быстродействия не только компенсировать эффект увеличения выходной постоянной времени Tвых= RвыхCн с ростом суммарной емкости нагрузки, состоящей из емкости линии связи Cлс и эффективной емкости входных ЛЭ, Cлэ, но и за счет схемотехники токовой форсировки на выходе ЛЭ получить снижение Tвых с ростом Cлс на отрицательном фронте (в некотором диапазоне емкостей УБИС). Другая дополнительная цель ставит необходимость увеличения функциональных возможностей неинвертирующих комплементарных элементов ЭПЛ с их эффективным согласованием с входными и выходными инверторами (при обеспечении приемлемого системного быстродействия, минимальной мощности потребления, обеспечении требуемой помехоустойчивости). К глобальной цели изобретения следует отнести достижение значительно более конкурентоспособного заявляемого биполярного логического элемента И, ИЛИ, "повторитель-формирователь" аналогичным решениям не только в биполярном базисе, но также в МОП/КМОП базисе.

Указанная задача достигается тем, что 1) микромощный логический элемент с высокой нагрузочной способностью содержит входные транзисторы первого типа проводимости, коллекторы которых соединены с первой шиной питания, базы - с соответствующими входами, а эмиттер - с базой согласующего транзистора второго типа проводимости и коллектором транзистора первого типа проводимости первого генератора тока, эмиттер согласующего транзистора соединен со вторым транзисторным генератором тока, коллектор согласующего транзистора соединен с базой транзистора первого типа проводимости первого генератора тока и базой и коллектором транзистора первого типа проводимости в диодном включении, эмиттер которого соединен с эмиттером транзистора первого генератора тока и второй шиной питания, эмиттер согласующего транзистора соединен с выходом элемента и эмиттером транзистора первого типа проводимости второго генератора тока, коллектор которого соединен с базой и коллектором транзистора второго типа проводимости в диодном включении и базой первого дополнительного транзистора второго типа проводимости, эмиттер которого соединен с эмиттером транзистора второго типа проводимости в диодном включении и с первой шиной, а коллектор - с базой транзистора первого типа проводимости и эмиттером второго дополнительного транзистора второго типа проводимости, коллектор которого соединен со второй шиной питания, а база соединена с эмиттером третьего дополнительного транзистора второго типа проводимости и с коллектором четвертого дополнительного транзистора второго типа проводимости, эмиттер которого соединен с первой шиной питания, а база - с третьей шиной питания, причем база третьего дополнительного транзистора соединена с базой согласующего транзистора, а коллектор соединен со второй шиной питания.

2) Элемент по п.1, в котором согласующий и третий дополнительный транзисторы выполнены в виде двухэмиттерного транзистора второго типа проводимости, коллектор которого соединен с базой и коллектором транзистора первого типа проводимости в диодном включении, первый эмиттер соединен с выходом, а второй эмиттер - с базой второго дополнительного транзистора.

3) Элемент по п.1 с одним входом, в котором база входного транзистора первого типа проводимости соединена с базой второго дополнительного транзистора второго типа проводимости, а третий и четвертый дополнительные транзисторы не подключены.

4) Элемент по п.1, в котором к эмиттеру согласующего транзистора подключена дополнительная ускоряющая емкость параллельно второму транзисторному генератору тока, и помимо первого выхода элемента с эмиттера согласующего транзистора используется второй быстродействующий выход с его базы.

5) Элемент по п.1, в котором к выходу элемента подключена выходная двухтактная комплементарная пара, содержащая транзистор Шоттки первого типа проводимости, эмиттер которого соединен с шиной отрицательного питания, коллектор - с выходом и коллектором транзистора Шоттки второго типа проводимости, эмиттер которого соединен с шиной положительного питания, а база - с базой транзистора Шоттки первого типа проводимости и со входом через параллельно соединенные резистор и конденсатор.

6) Элемент по п.1, в котором к каждому входу элемента подключены входные двухтактные комплементарные пары, содержащие транзистор Шоттки первого типа проводимости, эмиттер которого соединен с шиной отрицательного питания, коллектор - с выходом и коллектором транзистора Шоттки второго типа проводимости, эмиттер которого соединен с шиной положительного питания, а база - с базой транзистора Шоттки первого типа проводимости и с соответственным входом элемента через параллельно соединенные резистор и конденсатор.

Сущность изобретения и его отличительные от прототипа признаки заключаются в возможности обеспечения сверхбыстродействия биполярных комплементарных двухтактных (пуш-пульных) ЛЭ (И, ИЛИ повторителя-формирователя) в микромощном режиме сверхнизких статических токов эмиттерных повторителей (десятые доли мкА) и субполувольтовых напряжений логического перепада вплоть до 0.2 В при использовании схемотехники токовых зеркал генераторов тока с форсировкой выходных токов эмиттерных повторителей на активном и пассивном фронтах работы ЛЭ. Сущность заявляемого изобретения при синтезе более гибких многофункциональных многовходовых ЛЭ И, ИЛИ в микрорежиме заключается в обеспечении параллельного соединения эмиттерных повторителей на транзисторах одного типа проводимости и управляемых двухтактно (пуш-пульно) комплементарной транзисторной пары, не потребляющих практически статическую мощность, находясь в состояниях "1" или "0". Малая статическая мощность потребления ЛЭ достигается без ограничения и ухудшения скорости переключения при значительных емкостных нагрузках, причем скорость зарядки нагрузочных емкостей будет зависеть от уровня форсировки выходных динамических токов выходных комплементарных пар, обеспечивающих минимальное выходное сопротивление на обоих фронтах (причем на отрицательных или пассивных фронтах системное быстродействие ЛЭ даже будет улучшаться с ростом нагрузочной емкости).

Принципиально важно для выделения сущности изобретения - это эффективное взаимодействие комплементарных эмиттерных повторителей с учетом положительной обратной связи по току: когда на отрицательном (пассивном фронте) переключающего сигнала в результате открывания согласующего транзистора второго типа проводимости происходит увеличение его коллекторного тока, соответственно увеличивается ток транзистора в диодном включении диода токового зеркала, что приводит к увеличению падения напряжения на эффективном диоде с соответствующим форсированным, практически экспоненциальным увеличением тока в эмиттерном узле входных эмиттерных повторителей. Нарастание базового тока транзистора генератора тока приводит к возникновению в В раз большего эмиттерного тока согласующего транзистора, перезаряжающего нагрузочную емкость по пассивному фронту. В итоге инерция заряда на выходной нагрузочной емкости в начальный момент времени приводит к лавинообразному увеличению токов в соответствующих цепях, перезаряжающих данную емкость. Поскольку производная по времени от переключающего тока достаточно быстро увеличивается с ростом нагрузочной емкости (хотя время ее перезарядки, конечно, пропорционально Cн, RвыхCн, то в результате противодействия указанных факторов возможна ситуация, когда в достаточно широком диапазоне нагрузочных емкостей суммарное время задержки может либо не зависеть от величины Cн, либо с увеличением Cн время задержки даже может уменьшаться, что позволяет говорить о "парадоксальном эффекте изобретения. В то же время при дальнейшем увеличении Cн и доминировании постоянной времени RвыхCн задержки ЛЭ будут прямо пропорционально увеличиваться с ростом Cн.

Расширение функциональных возможностей ЛЭ за счет включения дополнительных инверторов достигается использованием на входе и выходе комплементарных ЭПЛ элементов двухтактных комплементарная пар-инверторов на транзисторах Шоттки, общая база которых соединена с входом пары через параллельно соединенные резистор и конденсатор, причем ненасыщенный режим данной пары обеспечивает высокое быстродействие при малых мощностях потребления и приемлемую помехоустойчивость. Расширение функциональных и режимных возможностей собственно неинвертирующих ЛЭ может быть достигнуто за счет использования дополнительной ускоряющей емкости (реализующей указанный эффект увеличения системного быстродействия на отрицательном фронте) и дополнительного выхода, обеспечивающего быструю зарядку и разрядку нагрузочных внешних емкостей по обоим фронтам.

Рассмотрим перечень фигур графического изображения и примеры конкретного выполнения заявленного ЛЭ для иллюстрации соответствующих пунктов формулы изобретения.

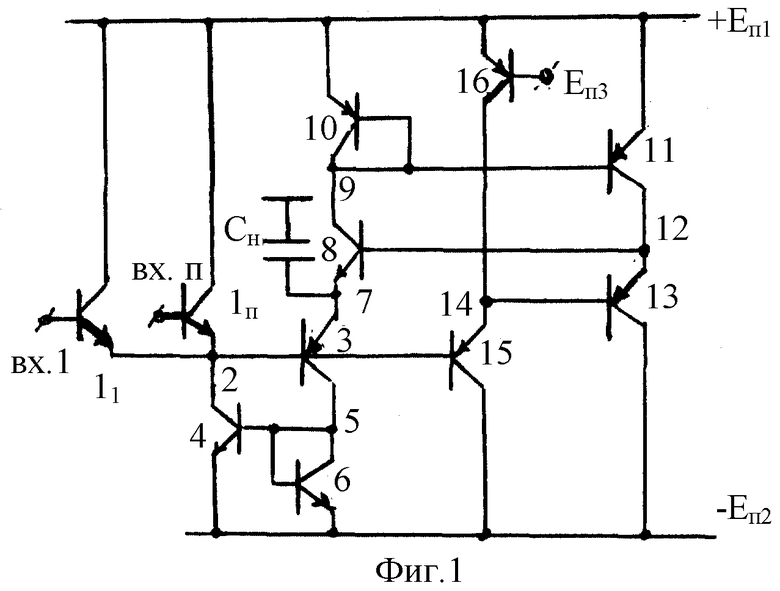

Микромощный логический элемент ИЛИ, изображенный на фиг. 1, содержит входные транзисторы первого типа проводимости 11, 1п (в рассматриваемом случае n-p-n типа), коллекторы которых соединены с шиной первого питания Eп1 (либо с общей шиной). Базы входных транзисторов подключены к соответствующим входам вх1, вхп, а их общий эмиттер 2 соединен с базой согласующего транзистора второго типа проводимости (p-n-p) 3 и коллектором транзистора первого типа проводимости (n-p-n) 4 первого генератора тока. Эмиттер согласующего транзистора 3 соединен со вторым транзисторным генератором тока. Коллектор согласующего транзистора 3 соединен с базой транзистора первого типа проводимости 4 первого генератора тока и базой и коллектором транзистора первого типа проводимости в диодном включении 6. Его эмиттер соединен с эмиттером транзистора 4 первого генератора тока и второй шиной питания Eп2. Эмиттер согласующего транзистора 3 соединен с выходом элемента 7, нагруженным на емкость Cн, и эмиттером транзистора первого типа проводимости (n-p-n) 8 второго генератора тока. Коллектор 9 транзистора 8 соединен с базой и коллектором транзистора второго типа проводимости (p-n-p) в диодном включении 10 и базой первого дополнительного транзистора второго типа проводимости (p-n-p) 11. Его эмиттер соединен с эмиттером транзистора 10 и с первой шиной Eп1, а коллектор 12 - с базой согласующего транзистора 8 и эмиттером второго дополнительного транзистора второго типа проводимости (p-n-p) 13. Его коллектор соединен со второй шиной питания, а база 14 соединена с эмиттером третьего дополнительного транзистора второго типа проводимости (p-n-p) 15 и с коллектором четвертого дополнительного транзистора второго типа проводимости (p-n-p) 16. Его эмиттер соединен с первой шиной питания Eп1, а база - с третьей шиной питания Eп3. База третьего дополнительного транзистора 15 соединена с базой согласующего транзистора 3, а коллектор соединен со второй шиной питания.

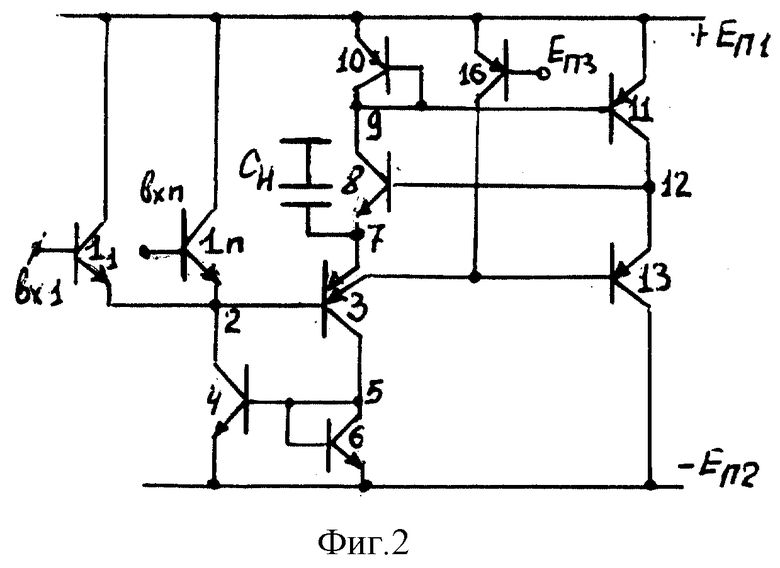

На фиг. 2 приведен модифицированный элемент, в котором согласующий 3 и третий дополнительный транзистор 15 на фиг. 1 выполнены в виде двухэмиттерного транзистора второго типа проводимости 3, коллектор которого соединен с базой и коллектором 5 транзистора первого типа проводимости в диодном включении, первый эмиттер соединен с выходом 7, а второй эмиттер - с базой второго дополнительного транзистора 13.

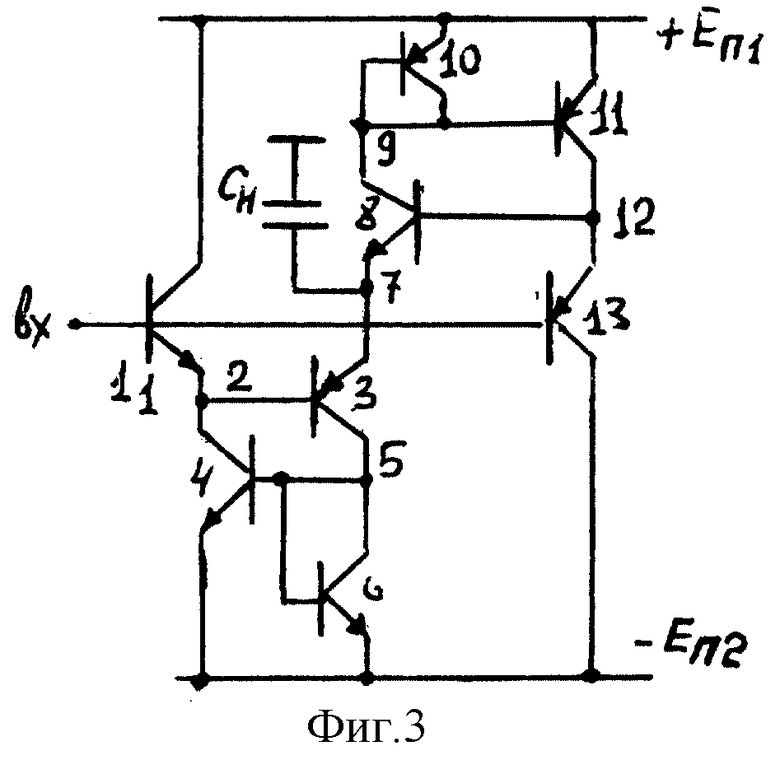

На фиг. 3 приведен одновходовый элемент, повторитель-формирователь, содержащий n-p-n входной транзистор 1, р-п-р входной транзистор 13, согласующий p-n-p транзистор 3, n-p-p транзистор первого генератора тока 4, n-p-n транзистор в диодном включении 6. База входного транзистора первого типа проводимости 1 соединена со входом 11, базой второго дополнительного транзистора второго типа проводимости 13.

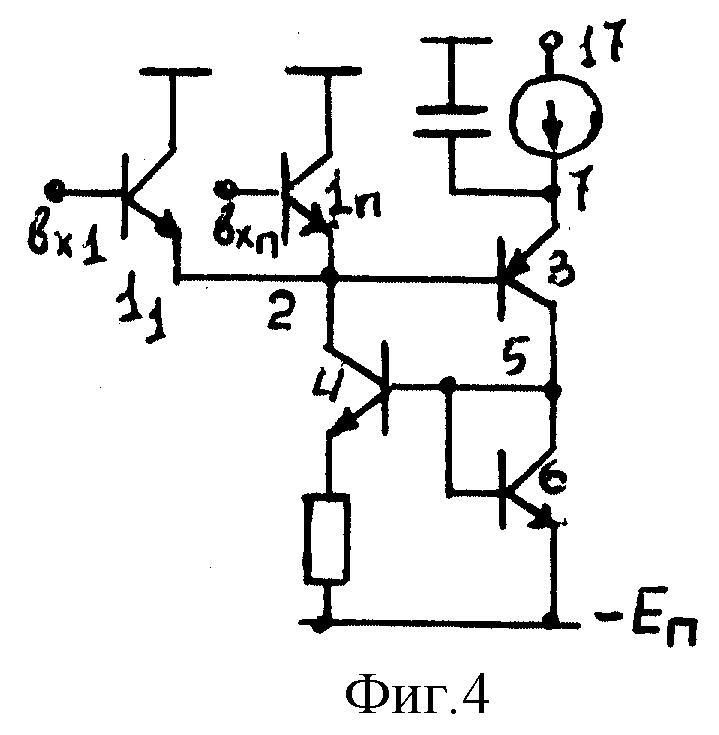

На фиг. 4 приведен фрагмент устройства для пояснения сущности предлагаемого устройства, где показан автономный второй генератор тока 17. В данном элементе к эмиттеру 7 согласующего транзистора 3 подключена дополнительная ускоряющая емкость С0 параллельно второму транзисторному генератору тока 17. Помимо первого выхода 7 элемента с эмиттера согласующего транзистора 3 используется второй быстродействующий выход 2 с его базы и эмиттеров входных транзисторов. Данный элемент эффективно работает с выхода 7 на значительную емкостную нагрузку только по активному фронту. Хотя эмиттерный выход 2 не обеспечивает согласования логических уровней, однако дает быструю зарядку нагрузочной емкости, подсоединенную к эмиттерам входных транзисторов на обоих фронтах переключающего сигнала. Данный эффект может быть использован в ряде схемотехнических приложений

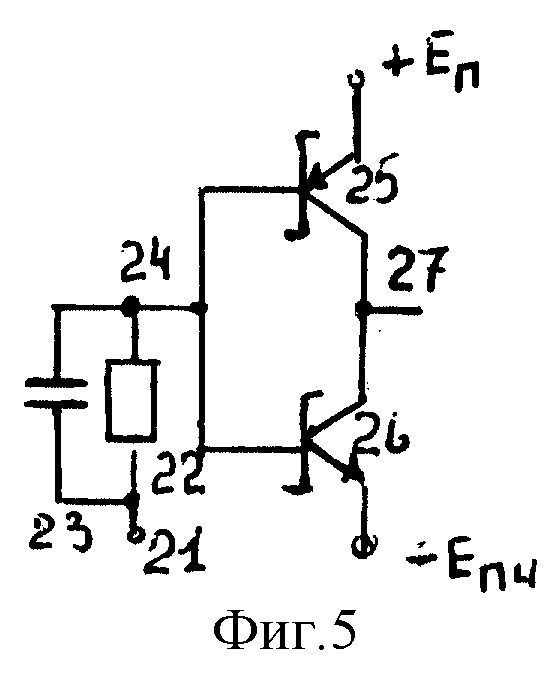

На фиг. 5 изображена двухтактная комплементарная пара с входом 21 и выходом 27, содержащая транзистор Шоттки первого типа проводимости 26, эмиттер которого соединен с шиной отрицательного питания -Eп, коллектор - с выходом и коллектором транзистора Шоттки второго типа проводимости 25. Его эмиттер соединен с шиной положительного питания Eп, а база - с базой 24 транзистора Шоттки первого типа проводимости 26 и со входом 21 через параллельно соединенные высокоомный резистор 22 и конденсатор 23.

Расширение функциональных возможностей ЛЭ при добавлении инвертора (фиг. 5) к выходу неинвертирующего комплементарного ЛЭ (фиг. 1-3) достигается следующим образом. К выходу элемента 12 подключена выходная двухтактная комплементарная пара транзисторов Шоттки, на их коллекторном выходе 27 реализуется функция НЕ для ЛЭ (фиг. 3 и фиг. 5) и функция ИЛИ-НЕ (для ЛЭ на фиг. 1, 2 и 5). Если входными транзисторами становятся транзисторы второго типа проводимости (р-п-р типа) с соответствующей заменой типа проводимости в транзисторах на фиг. 1,2, то сочетание ЭПЛ элементов на фиг. 1,2 и двухтактного инвертора Шоттки (фиг. 5) позволяет реализовать логику И-НЕ.

Более того, использование более гибких схемотехнических приемов объединения выходов соответствующих согласующих эмиттерных повторителей позволяет реализовать сложные функции И-ИЛИ, ИЛИ-И, а при использовании выходных инверторов (фиг. 5) реализовать И-ИЛИ-НЕ, а также ИЛИ-И-НЕ.

Однако в ряде случаев для работы на значительные емкостные нагрузки целесообразно использовать инверторы (фиг. 5) на входах ЭПЛ элементов. Тогда по правилу Моргана при логической сумме инверсных переменных реализуется функция И-НЕ, а при логическом умножении инверсных переменных реализуется функция ИЛИ-НЕ. Аналогично рассмотренному выше просто реализуются функции И-ИЛИ-НЕ, ИЛИ-И-НЕ. При обеспечении высокой помехоустойчивости по каждому входу на выходе реализуется высокое системное быстродействие по обоим фронтам, что позволяет значительно увеличить качество разработки элементов УБИС в компоновочном пространстве кристалла.

Рассмотрим принцип действия и главный эффект компенсации потерь системного быстродействия в ЛЭ, изображенных на фиг. 1-3. Предлагаемое устройство работает следующим образом. В положительной логике, когда транзисторы первого типа проводимости относятся к n-p-n, а транзисторы второго типа проводимости относятся к p-n-p, на выходе 7 реализуется логика ИЛИ при соответствующих полярностях напряжения на шинах питания. Когда транзисторы первого типа проводимости относятся к p-n-p, а транзисторы второго типа проводимости относятся к n-p-n, на выходе 7 реализуется логика И при соответствующих полярностях напряжения на шинах питания.

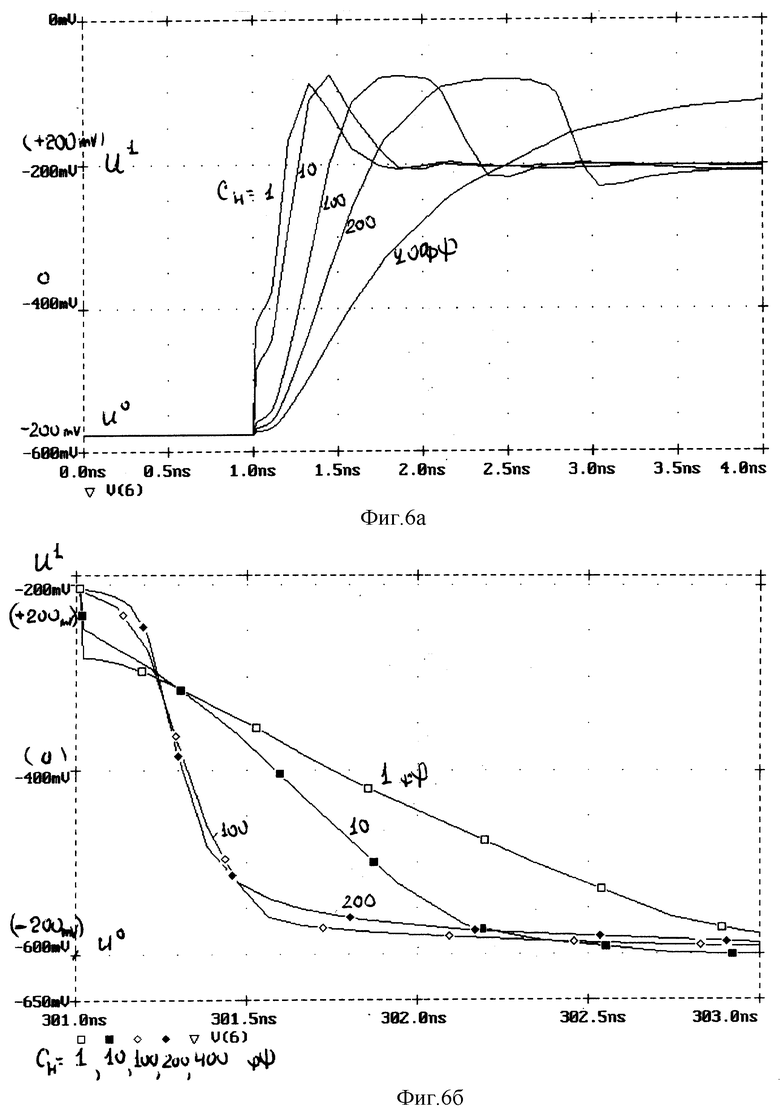

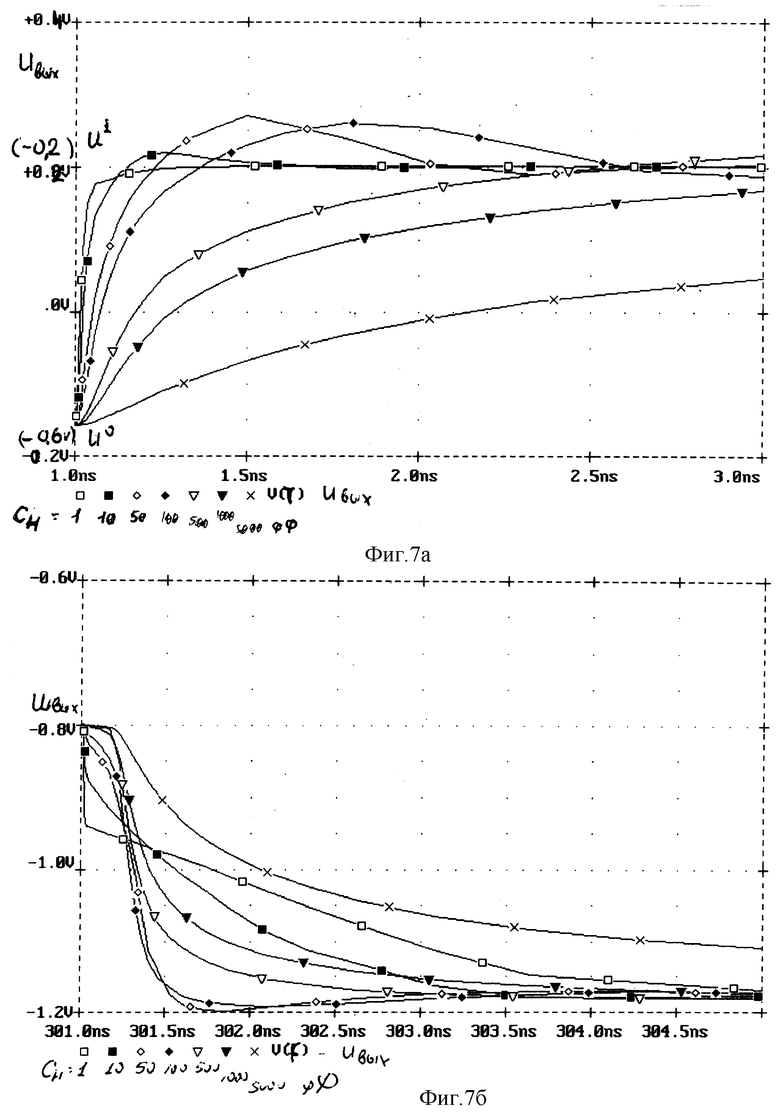

В состав рассматриваемых комплементарных эмиттерных повторителей, изображенных на фиг. 1-4, включены специально разработанные форсирующие (ускоряющие) переходные процессы схемы управляемых генераторов тока на транзисторах 4 и 11,8 в конфигурации токовых зеркал (с соответствующими транзисторами в диодном включении 6 и 10), а также дополнительные согласующие (сдвигающие) цепи. Это позволяет практически устранить недостатки схемотехники эмиттерных повторителей на пассивном фронте переключения: большая задержка на спадающем фронте сигнала при "подзапирании" переключающего транзистора, что приводит к балластной мощности потребления при требовании компенсировать потери системного быстродействия при значительных емкостных нагрузках. Рассмотрим принцип действия для симметричных логических уровней U1= 0,2 В, U0 = -0,2 В, Eп1= 1,1 В, Eп1 = -1,1 В. Уровни просто трансформируются при использовании общей шины вместо отрицательной Eп2, и Eп2 = 2,2 В, тогда U1 = - 0,2 В, U0 = -0,6 В (что отражено в расчетах на фиг. 6 и 7).

Пусть вначале Uвх1 = Uвх2 = 0,2 В и входной сигнал переключается в положение логического нуля Uвх1 = Uвх2 = U1 =- 0,2 В. В начальный момент времени нагрузочная емкость Cн заряжена до определенного значения потенциала, соответствующего уровню U1 на выходе схемы. Инерция перезарядки Cн приводит к нарастанию падения напряжения между выходом 7 и эмиттерным узлом входных транзисторов 2: U7 -U2. В статике до переключения величина U7-U2 равна постоянной величине, а именно падению напряжения на открытом эмиттерном переходе согласующего транзистора 3. Условие переключения U7 > U2 на отрицательном (пассивном) фронте переключающего сигнала приводит к сильному форсированному открыванию согласующего транзистора 3, соответственно происходит увеличение его коллекторного тока, соответственно увеличивается ток транзистора в диодном включении токового зеркала, что приводит к увеличению падения напряжения на эффективном диоде 6 с соответствующим форсированным, практически экспоненциальным увеличением тока в эмиттерном узле 3 входных эмиттерных повторителей.

Нарастание базового тока транзистора 4 первого генератора тока приводит к возникновению в В раз большего эмиттерного тока согласующего транзистора, перезаряжающего нагрузочную емкость. В конечном итоге, инерция заряда на выходной нагрузочной емкости Cн в начальный момент времени и действие положительной обратной связи в соответствующих указанных комплементарных транзисторах приводит к лавинообразному увеличению токов в соответствующих цепях, перезаряжающих данную емкость Cн. Производная по времени от переключающего тока достаточно быстро увеличивается с ростом нагрузочной емкости, хотя время ее перезарядки, конечно, пропорционально Cн, RвыхCн. Таким образом, в результате противодействия рассмотренных факторов роста производной тока и учета выходной постоянной времени возможна ситуация, когда в достаточно широком диапазоне нагрузочных емкостей суммарное время задержки может либо не зависеть от величины Cн, либо с увеличением Cн время задержки даже может уменьшаться. Все это позволяет говорить о "парадоксальном эффекте изобретения" - улучшении нагрузочной способности ЛЭ на пассивном фронте. В то же время при дальнейшем увеличении Cн и доминировании постоянной времени RвыхCн задержки ЛЭ будут прямо пропорционально увеличиваться с ростом Cн. Отметим, что на активном фронте наблюдается также улучшение нагрузочной способности в динамике переключения, однако "парадоксального эффекта" уменьшения задержки с ростом Cн не наблюдается.

Сочетание двухэмиттерного согласующего транзистора 3, изображенного на фиг. 2, с соответствующими нормальному, рассмотренному выше функционированию ЛЭ (фиг. 1), позволяет сократить количество компонентов и площадь элемента на кристалле.

Фиг. 3 иллюстрирует эффективный повторитель-формирователь уровней, характеризующийся не только повышенным системным быстродействием, но и принципиальным уменьшением количества приборов в схеме, малокомпонентностью. Данный элемент будет характеризоваться максимальным системным быстродействием как для малых, так и для больших нагрузочных емкостей.

Элемент на фиг. 4 имеет самостоятельную значимость и ценность в случае, когда не столь важно обеспечение сверхвысокого быстродействия на отрицательном (пассивном) фронте в микрорежиме статических токов ЛЭ. Данный ЛЭ может быть весьма эффективно использован в СБИС вследствие его малокомпонентности и малых потребляемых мощностей. Очень важной спецификой работы этого элемента является предельно низкая инерционность узла 2, что может быть использовано в ряде схемотехнических решений и специальных применений, хотя и со смещением логических входных уровней на напряжение открытого p-n перехода. Использование резистора в эмиттерной цепи транзистора 4 генератора тока между эмиттером и шиной питания позволяет увеличить форсировку переключения на пассивном фронте сигнала и повысить системное быстродействие ЛЭ в микрорежиме статических токов.

Выбор электрических параметров инвертора на комплементарной паре транзистора Шоттки реализуется из обеспечения сверхвысокого пикосекундного быстродействия и форсированного включения по входу при обеспечении минимальной статической мощности потребления в десятые доли нановатт. При этом напряжения Eп выбираются около 0,45 В, R = 0,3-1 МОм, C = 20-100 фФ.

На фиг. 6 и 7 представлены результаты моделирования ЛЭ (фиг. 1), иллюстрирующие эффективную работу в микрорежиме, при P= 0,5 мкВт с высочайшей нагрузочной способностью на обоих фронтах (с обнаружением описанного выше качественно парадоксального эффекта уменьшения задержки при увеличении емкости нагрузки, что крайне актуально в логических неоднородных СБИС с длинными линиями связи). При моделировании по SPICE программе были использованы параметры n-p-n и p-n-p транзисторов, соответствующие уровню 0,18 мкм комплементарной технологии.

Анализ моделируемых переходных процессов в микромощном ЭПЛ элементе показывает, что для нагрузочных емкостей 50-300 фФ, где достигается максимальный эффект максимально быстрого переключения, время задержки по отрицательному фронту не превышает 300 пс (для параметров транзистора 0,18 мкм технологии); для этих же емкостей время задержки по положительному фронту также не превышает 300 пс. При статической мощности потребления двухвходового ЛЭ (фиг. 1) P = 1,1 мкВт и средней максимальной задержке 300 пс системный фактор Ptз(Cн = 300 фФ) = 0,33 фемтаДжоуль, что на несколько порядков превышает лучшие результаты, достигнутые в классе биполярных и КМОП схем при сравнимых емкостных нагрузках. При огромной емкости 5 пФ среднее время задержки по двум фронтам составляет 2 нс, при этом фактор Ptз (5 пФ)= 2,2 фДж, что лучше аналогичных показателей для биполярных и КМОП ЛЭ на два-три порядка. Впечатляющий эффект предложенной схемотехники говорит о высоком скоростном и мощностном потенциале. По фактору действия D=P(tз)2, позволяющему оптимизировать быстродействие и выбирать оптимальный электрический режим функционирования, отрыв от конкурентных традиционных схемотехнических направлений КМОП и ЭСЛ будет еще более значительным.

Таким образом, на основе комплементарных ЭПЛ элементов и двухтактных инверторов можно синтезировать различные конструктивные варианты быстродействующих, микромощных, помехоустойчивых ЛЭ, занимающих малую площадь на кристалле, причем уникальная возможность использования нагрузочных (и специальных, вводимых) емкостей для получения позитивного эффекта увеличения системного быстродействия позволяют создавать очень экономичные высокопроизводительные интегральные системы УБИС с максимальной плотностью упаковки элементов.

Технико-экономический эффект изобретения заключается в значительном увеличении системного быстродействия цифровых логических схем, а также возможности работы с сигналами с малыми логическими перепадами и напряжениями питания при приемлемой помехоустойчивости, в микромощном режиме минимально возможных статических, динамических и полных мощностей, в резком увеличении уровня интеграции УБИС, как для технологий в области глубокого субмикрона, что важно при построении сверхскоростных УБИС - элементно-технологической базы перспективных микропроцессорных, суперЭВМ высших поколений, работающих с тактовыми частотами в единицы-десятки ГГЦ для наземного и космического использования.

Технико-экономический эффект изобретения заключается в общем увеличении системного быстродействия принципиально неоднородных систем с произвольными и очень длинными линиями связи на кристаллах больших размеров, где можно разместить собственно весь суперкомпьютер, что весьма важно и актуально при построении сверхскоростных УБИС - элементно-технологической базы перспективных суперкомпьютеров высших поколений с производительностью в несколько десятков-сотен Гфлоп на процессор в кристалле.

Источники информации

1. Electronics, 1967, v.40, N 6, p.194.

2. Электроника, 1983, т. 56, N 23, с. 55-61.

3. AC 1166296 А: "Логический элемент", автор А.Н.Бубенников (прототип). Бюл. 25, 07.07.1985.

Данное изобретение относится к устройствам импульсной и цифровой техники, в частности к интегральным логическим элементам БИС, ЭВМ. Техническим результатом является создание микромощных малокомпонентных логических элементов И, ИЛИ, формирователя-повторителя, обеспечивающих низковольтный логический перепад в субполувольтовом диапазоне вплоть до 0.2 В при высочайшей нагрузочной способности по обоим фронтам, высокие функциональные возможности, малокомпонентность для УБИС. Указанный результат достигается тем, что микромощный логический элемент с высокой нагрузочной способностью содержит входные транзисторы первого типа проводимости, коллекторы которых соединены с первой шиной питания, базы - с соответствующими входами, а эмиттер - с базой согласующего транзистора второго типа проводимости и коллектором транзистора первого типа проводимости первого генератора тока, эмиттер согласующего транзистора соединен со вторым транзисторным генератором тока, коллектор согласующего транзистора соединен с базой транзистора первого типа проводимости первого генератора тока и базой и коллектором транзистора первого типа проводимости в диодном включении, эмиттер которого соединен с эмиттером транзистора первого генератора тока и второй шиной питания, эмиттер согласующего транзистора соединен с выходом элемента и эмиттером транзистора первого типа проводимости второго генератора тока, коллектор которого соединен с базой и коллектором транзистора второго типа проводимости в диодном включении и базой первого дополнительного транзистора второго типа проводимости, эмиттер которого соединен с эмиттером транзистора второго типа проводимости в диодном включении и с первой шиной, а коллектор - с базой транзистора первого типа проводимости и эмиттером второго дополнительного транзистора второго типа проводимости, коллектор которого соединен со второй шиной питания, а база соединена с эмиттером третьего дополнительного транзистора второго типа проводимости и с коллектором четвертого дополнительного транзистора второго типа проводимости, эмиттер которого соединен с первой шиной питания, а база - с третьей шиной питания, причем база третьего дополнительного транзистора соединена с базой согласующего транзистора, а коллектор соединен со второй шиной питания. 2 с. и 3 з.п.ф-лы, 7 ил.

| Логический элемент | 1983 |

|

SU1166296A1 |

| Многопороговый логический элемент | 1983 |

|

SU1166297A1 |

| Электроника | |||

| Институт | |||

| - М., 1983, т.56, № 23, с.55-61 | |||

| EP 0357815 А1, 14.03.1990. | |||

Авторы

Даты

2001-08-10—Публикация

1999-11-04—Подача