искажения. Первый выход схемы сравнения подключен ,к первому входу блока итеративного вычисления суммы и через блок подсчета количества единиц IK первому входу блока вычитания и лервому входу первой дополнительной схемы сравнения, выход блока определения вычета - к вторым входам блока вычитания и первой дополнительной схемы сравнения, к входу блока определения начала пакета ошибок, к первым входам коммутатора и второй дополнительной схемы сравнения и через третью дополнительную схему сравнения -к четвертому -входу блока определения вида искажения, пятый и шестой входы которого связаны с выходами первой дополнительной схемы сравнения. Первый выход блока определения .вида искажения соединен с третьим входом блока выделения информационной части сообщения, второй выход блока определения вида искажения - с вторыми входами блока итеративного вычисления суммы, блока коррекции и «оммутатора, третий вход которого подсоединен к выходу блока .вычитания, а четвертый и пятый входы - к выходам блока олределения начала пакета ошибок. Второй вход и первый и второй выходы второй дополнительной схемы сравнения нодключены соответственно к первому выходу и третьему и четвертому входам блока итеративного вычисления суммы, второй выход которого соединен с первым входом элемента «И, третий выход второй дополнительной схемы сравнения - к второму входу элемента «И, выход которого соединен с шестым входом коммутатора, а выход коммутатора - к третьему входу блока коррекции, выход которого соединен с выходом устройства.

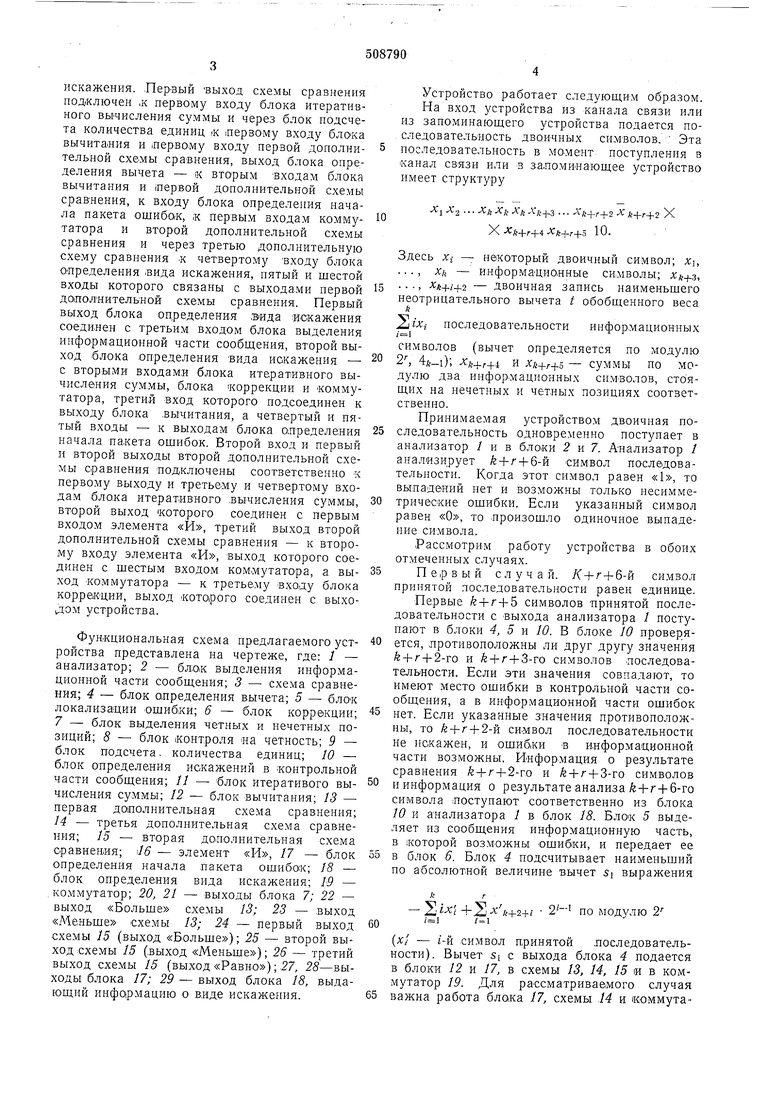

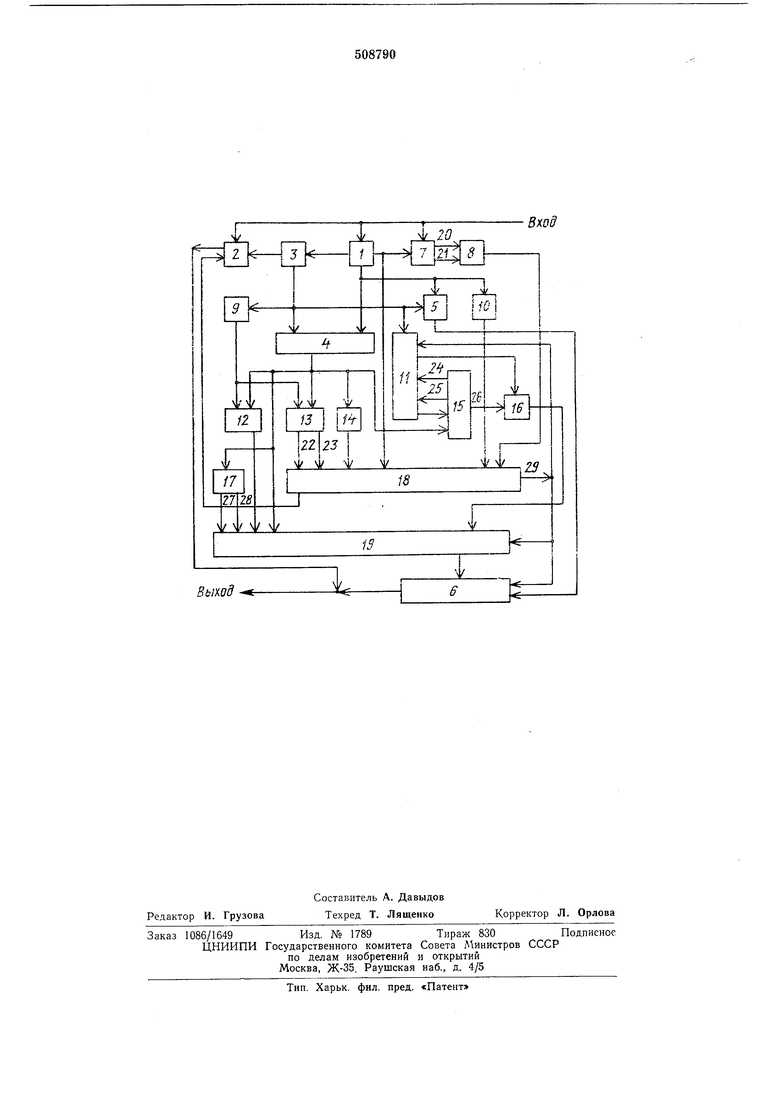

Функциональная схема предлагаемого устройства представлена на чертеже, где: / - анализатор; 2 - блок выделения информационной части сообщения; 3 - схема сравнения; 4 - блок олределения вычета; 5 - блок локализации ошибки; 6 - блок коррекции; 7 - блок выделения четных и нечетных позиций; 8 - блок контроля «а четность; 9 - блок подсчета- количества единиц; 10 - блок определения искажений в контрольной части сообщения; // - блок итеративого вычисления суммы; 12 - блок вычитания; 13 - первая дополнительная схема сравнения; 4 - третья дополнительная схема сравнения; 15 - вторая дололнительная схема сравнения; il6 - элемент «И, 17 - блок определения начала .пакета ошибок; /5 - блок определения вида искажения; 19 - .коммутатор; 20, 21 - выходы блока 7; 22 - выход «Больше схемы 13; 23 - выход «Меньше схемы 13; 24 - первый выход схемы 15 (выход «Больше); 25 - второй выход схемы 15 (выход «Меньше); 26 - третий выход схемы 15 (выход «Равно); 57, 28-выходы блока 17; 29 - выход блока 18, выдающий информацию о в.иде искажения.

Устройство работает следующим образом.

На вход устройства из канала связи или из запоминающего устройства подается последовательность двоичных СИ.МВОЛОВ. ; Эта последовательность в момент поступления в «анал связи или в заломи-нающее устройство имеет структуру

... Х/1 Хг; Aft Л/г-|-3 Aft-f.r+2 ft-fr-f-2 X У Х/г+г+5 Ю.

Здесь Х{ - некоторый двоичный символ; Xi, ... , Xh - информационные символы; , ..., x, - двоичная запись наименьшего

неотрицательного вычета t обобщенного веса k

iXi последовательности инфор.мационных

символов (вычет определяется по модулю 2 ); ft+,+4 и Xk+r+- - суммы по модулю два инфор.мационных символов, стоящих на нечетных и четных позициях соответственно.

Принимаемая устройством двоичная последовательность одновременно поступает в анализатор /ив блоки 2 к 7. Анализатор / анализирует k + r + Q-vi символ последовательности. Когда этот символ равен «1, то выладений нет и возможны только несимметрические ощибки. Если указаиный символ равен «О, то лроизощло одиночное выпадение символа.

Рассмотрим работу устройства в обоих отмеченных случаях.

Первый случай. /C+r-f 6-й символ принятой последовательности равен единице.

Первые k + r + 5 символов лринятой последовательности с выхода анализатора / поступают в блоки 4, 5 и 10. В блоке 10 проверяется, лротивоположны ли друг другу значения k + r + 2-го и k + r+3-го символов .последовательности. Если эти значения совпадают, то имеют место ошибки в контрольной части сообщения, а в информационной части ошибок нет. Если указанные значения противоположны, то k + r + 2-fi си.мвол последовательности не искажен, и ошибки в информационной части возможны. Информация о результате сравнения k + r + 2-го и k + r + 3-го символов и информация о результате анализа + г+6-го символа лоступают соответственно из блока 10 и анализатора / в блок 18. Блок 5 выделяет из сообщения информационную часть, в которой возможны ошибки, и лередает ее в блок 6. Блок 4 подсчитывает наименьший по абсолютной величине вычет Si выражения

- ixi +2А-/г-ь2+г 2- по модулю 2 (

(xi - 1-й символ пр.инятой лоследовательности). Вычет Si с выхода блока 4 подается в блоки 12 и 17, в схемы 13, 14, 15 и в коммутатор 19. Для рассматриваемого случая важна работа блока 17, схемы 14 и коммутатора 19. Схема 14 вычет Si сравнивает с ну-лем, и информация о результате сравнения поступает из схемы 14 в блок 8. В блоке /7

I S I - 1 вычисляются две величины: j 5j j .

Эти величины соответственно с выходов 27 и 28 блока 17 поступают в коммутатор 19. Блок 7, получив из анализатора / информацию о результате анализа fe + r-f 6-го символа, выделяют среди первых k символов принимаемой последовательности символы, стоящие на четных и .нечетных .позициях. Четные символы поладают на выход 20, нечетные символы - на выход 21. Кроме того, на .выход -20 проходит k + r+5-н символ принимаемой последовательности, а на выход 21 й + г+4-й символ. Блок 8 вычисляет две суммы по модулю два: S2 и 5з, причем «2 - сумма двоичных символов, появившихся на выходе 20 блошка 7, SB - сумма двоичных символов, появившихся на выходе 21 блока 7. Значения S2 и s передаются -из блока 8 в блок 18. В блоке 18 на основе информации, поступающей из блоков 8 и 10, из анализатора / и схемы 14, определяется вид искажения. При этом логические бло.ки, входящие в состав блока 18, реализуют следующий алгорИТм.

Поскольку k + r+6-и символ .принятой последовательности равен единице, то выпадений нет. Вычисляется сумма s S2 + S3. Ошибок в информационной части нет, если выполняется любое из условий: значения k + r+2-го И + r-f3-ro символов принятой последовательности совпадают; s Si 0; Si 0, siv О, s 0.

Сигнал об отсутствии ошибок в информационной части поступает из блока 18 в блок 2, который выделяя первые k символов принятой последовательности, выдает их на выход устройства. На этом процесс декодирования заканчивается.

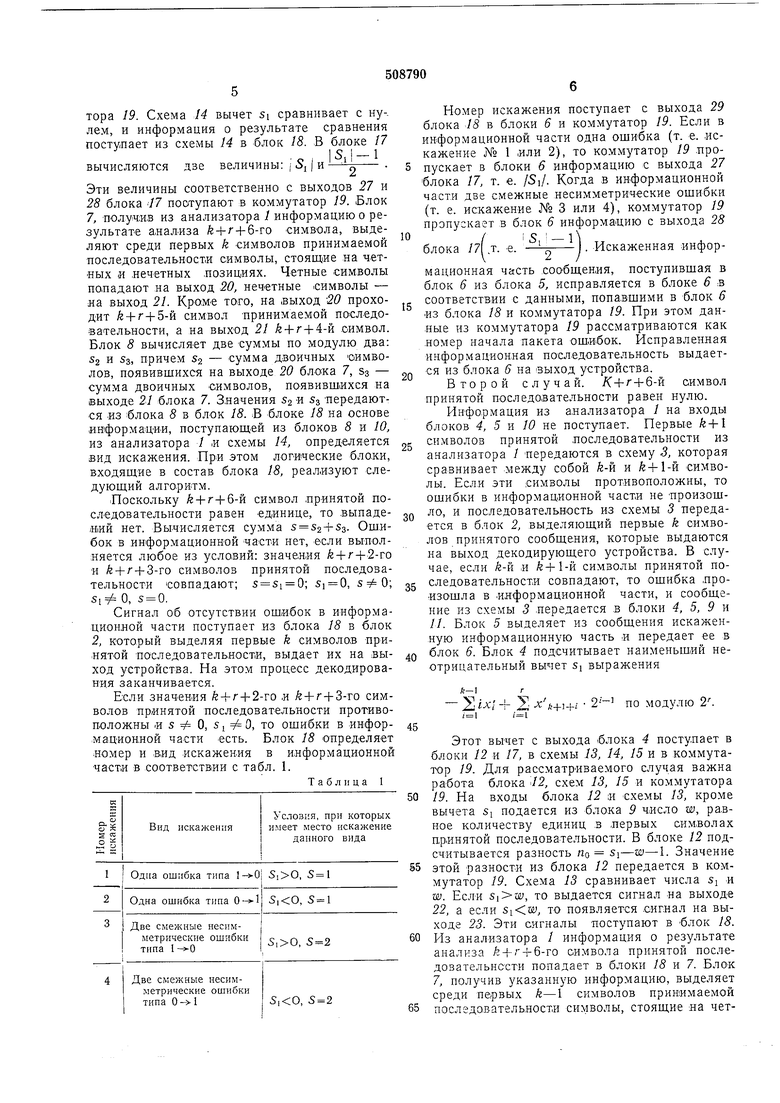

Если значения k + r + 2-то и k + r+3-то символов принятой последовательности противоположны и S О, Si 0, то ошибки в информационной части есть. Блок 18 определяет номер и вид искажения в информационной части в соответствии с табл. 1.

Таблица I

1 Одна ошибка типа ,

метрические ошибки

5,0, типа 1

Две смежные иесимметрические ошибки

5,0, тииа О- 1

Номер искажения поступает с выхода 29 блока 18 в блоки 6 и коммутатор 19. Если в информационной части одна ошибка (т. е. искажение № 1 или 2), то коммутатор 19 .пропускает в блоки 6 информацию с выхода 27 блока 17, т. е. /Si/. Когда в информационной части две смежные несимметрические ошибки (т. е. искажение № 3 или 4), коммутатор 19 пропускает в блок 6 информацию с выхода 28

/I 5 : -1

блока /7 т. е. .Искаженная информационная часть сообщения, поступившая в блок 6 из блока 5, исправляется в блоке 6 s соответствии с данными, попа.вщими в блок 6 «3 блока 18 и коммутатора 19. При этом данные из коммутатора 19 рассматриваются как номер начала пакета ошибок. Исправленная информационная последовательность выдается из блока 6 на выход устройства.

Второй случай. /С+г + б-й символ принятой последовательности равен нулю.

Информация из анализатора 1 на входы блоков 4, 5 и 10 не поступает. Первые k + l

символов принятой .последовательности из анализатора 1 передаются в схему 3, которая сравнивает между собой fe-й и k + 1-и символы. Если эти символы противоположны, то ошибки в информационной части не произошло, и последовательность из схемы 3 передается в блок 2, выделяющий первые k символов принятого сообщения, которые выдаются на выход декодирующего устройства. В случае, если й-й и k+1-к символы принятой последовательности совпадают, то ошибка .произошла в .информационной части, и сообщение из схемы 3 .передается в блоки 4, 5, 9 и //. Блок 5 выделяет из сообшения искаженную информационную часть и передает ее в

блок 6. Блок 4 подсчитывает наименьший неотрицательный вычет Si выражения

-1г

- ixi-r 2 - k+i+i по модулю 2.

;

Этот вычет с выхода блока 4 поступает в блоки 12 и 17, в схемы 13, 14, 75 и в коммутатор 19. Для рассматриваемого случая важна работа блока 12, схем 13, 15 и коммутатора

19. На входы блока 12 и схемы 13, кроме вычета Sj подается из блока 9 число w, равное количеству единиц в первых символах принятой последовательности. В блоке 12 подсчитывается разность По Si-w-1. Значение

этой разности из блока 12 передается в коммутатор 19. Схема 13 сравнивает числа Sj и W. Если , то выдается сигнал на выходе 22, а если , то появляется сигнал на выходе 23. Эти сигналы поступают в блок 18.

Из анализатора / информация о результате анализа k + r + Q-ro символа принятой последовательнссти попадает в блоки 18 и 7. Блок 7, получив указанную информацию, выделяет среди первых k-1 символов принимаемой

последо.вательности символы, стоящие на четных и .нечетных лозициях. Четные символы поступают на выход 20, нечетные символы - на выход 2У. Кроме того, на выход 20 проходит й + г + З-й символ принимаемой последовательности, а на выход 21 - + г-ь4-й символ. Блок 8, как и в предыдущем случае, вычисляет две суммы по модулю два: Sj и 5з - и передает значения этих сумм в блок 18. В блоке 18 на основе .информации, поступившей из блока 8, анализатора 1 и схемы 13, определяется вид искажения. При этом логические блоки, входящие .в состав блока /8, реализуют следующий алгоритм.

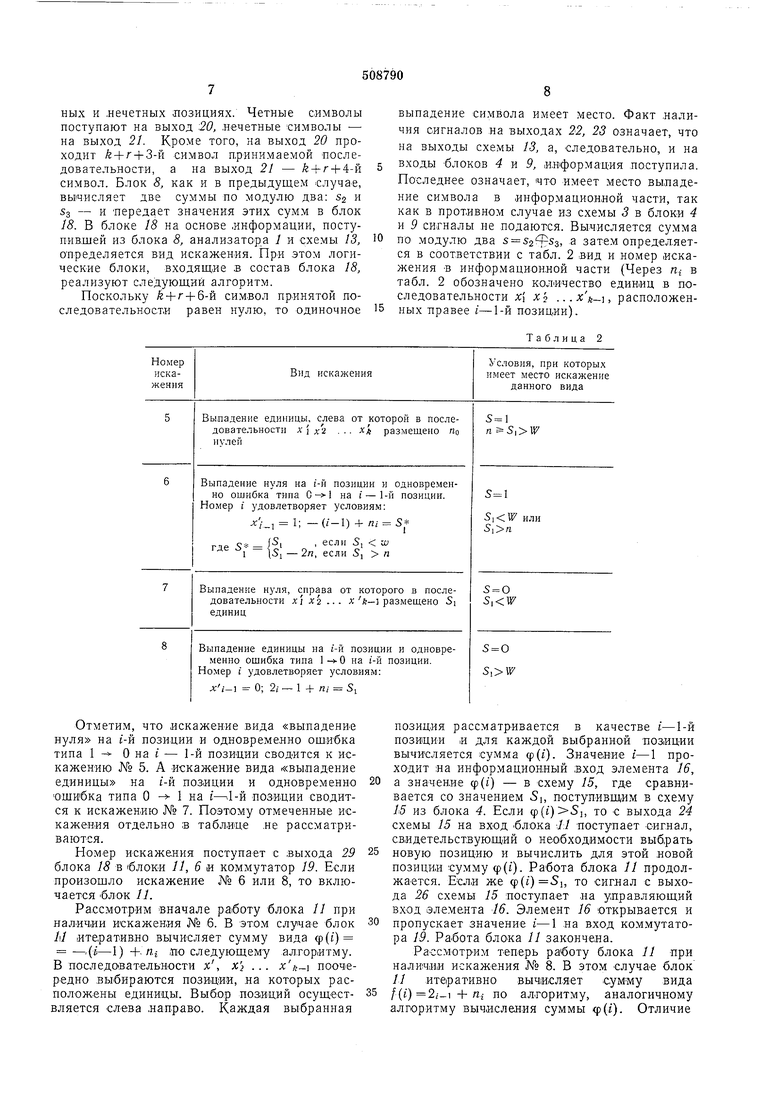

Поскольку -fr-f6-E символ принятой последовательности равен нулю, то одиночное

Номер

Вид искажения искажения

Выпадение единицы, слева от которой в последовательности .V 1 д;2 . .. к/1 размещено «о иулей

Выпадение нуля на -й иознцни и одновременно ошибка типа О 1 на i-1-й позиции. Номер I удовлетворяет условиям:

-«/ 1; -(/-) + /;; 5

Р„е

1 tSi - 2/7, если 5j п

Выпадение нуля, справа от которого в последовательности xix2... хft-1 размещеио Si единиц

Выпадение единицы на г-й позиции и одновременно ошибка типа 1 - О на i-й позиции. Номер I удовлетворяет условиям:

xi- 0; 2,- - 1 + щ Si

Отметим, что искажение вида «выпаденце нуля на t-й позиции и одновременно ощибка типа 1 - О на i - 1-й позиции сводится к искажению № 5. А искажение вида «выпадение единицы на г-й позиции и одновременно ошибка типа О - 1 на i-.1-й позиции сводится к искажению № 7. Поэтому отмеченные искажения отдельно в таблице .не рассматриваются.

Номер искажения поступает с выхода 29 блока 18 в блоки 11, 6 и коммутатор 19. Если произощло искажение № 6 или 8, то включается блок 11.

Ра.ссмот.рим вначале pai6oTy блока 11 при наличии искажения № 6. В этом случае блок 111 итеративно вычисл.яет сумму вида ф(г) -,(i-1) -f. Wj .йо следующему алгоритму. В последовательности х , х ... x/t-t поочередно выбираются позиции, .на которых расположены единицы. Выбор позиций осуществляется слева направо. Каждая выбранная

выпадение символа имеет место. Факт наличия сигналов .на выходах 22, 23 означает, что на выходы схемы 13, а, следовательно, и на входы блоков 4 VI 9, информация .поступила. Последнее означает, что имеет место вьшадение символа в информационной части, так как в противном случае из схемы 3 в блоки 4 и 9 сигналы не подаются. Вычисляется сумма по модулю два 5 , а затем определяется в соответствии с табл. 2 вид и номер искажения в инфор.мационной части (Через «j в табл. 2 обозначено количество единиц в последовательности Х ;c:j ...xk-,, расположенных правее i-1-й позиции).

Таблица 2

Условия, при которых

имеет место искажение

данного вида

S

S,«7 или

S 0 S,U7

S 0

S,VF

позиция рассматривается в качестве i--1-й позиции и для каждой выбранной позиции вычисляется сумма ф(0- Значение i-1 проходит на информационный вход элемента 16,

а значение (f(i} - в схему 15, где сравнивается со значением 5i, поступивщим в схему /5 из блока 4. Если (p(i)Si, то с выхода 24 схемы 15 на вход .блока .// поступает сигнал, свидетельствующий о необходимости выбрать

новую позицию и вычислить для этой .новой ПОЗИЦИ.И Сумму ф(1). Работа блока 11 продолжается. ЕСЛ.И же f(i)S, то сигнал с выхода 26 схемы 15 поступает на управляющий вход элемента 16. Элемент 16 открывается и

пропускает .значение i-1 на вход коммутатора 19. Ра.бота блока 11 закончена.

Рассмотрим теперь работу блока 11 при наличии искажения № 8. В этом случае блок 11 итеративно вычисляет сумму вида

/(г) по алгоритму, аналогичному алгоритму выч.ислен.ия суммы p(0- Отличие в том, что в качестве позиции выбираются позиции с символом «О, а -сигналом для Продолжения работы блока 11 и выбора новой позиции является сигнал с выхода 25 схемы /5. Выбор позиций при вычислении суммы f(i) также осуществляется слева направо, а значение i-1 через элемент 16 также лостулает в коммутатор 19. Коммутатор 19, получив из блока 18 информацию о виде искажения, пропускает в блок 6 либо число По (в Случае искажения № 5), либо число i-1 (при искажениях № 6, 8), либо число Sj (если искажение № 7). Блок 6, приияв от коммутатора указаниые числа л получив из блока 18 номер искажения, осуществляет коррекцию искаженной информационной части сообщения, поступившей в блок 6 из блока 5. Коррекция проводится в соответствии с табл. 2. Исправленная информационная последовательность выдается из блока 6 на выход устройства. Формула изобретения Устройство для декодирования кодов, содержащее анализатор, вход которого соединен с входом устройства, а первый выход- с входом схемы сравнения, первый выход схемы сравнения соединен с первым входом блока определения вычета и с первым входом блока локализации ощибки, выход которого соединен с первым входом блока коррекции, второй выход схемы сравнения соединен с первым входом блока выделения информационной части сообщения, выход которого соединен с выходом блока коррекции, отличающееся тем, что, с целью повышения исправляющей способности устройства, в него дополнительно введены блок выделения четных и нечетных позиций, блок контроля на четность, -блок определения искажений в контрольной части сообщения, коммутатор, элемент «И, три схемы сравнения, блок итеративного вычисления суммы, блок подсчета количества единиц, блок .вычитания, блок определения начала пакета- ошибок и блок определения вида искажения, причем вход устройства соединен с первым входом блока выделения четных и нечетных позиций и с вторьш входом блока выделения информационной части сообщения, второй выход анализатора соединен с первым входом блока определения вида искажения и с вторым входом блока выделения четных и нечетных позиций, оба выхода которого через блок контроля иа четность соединены с вторым входом блока определения вида искажения, третий выход анализатора соединен со вторыми ,входами блока определения вычета и блока локализации ошибки и через блок определения искажений в контрольной части сообщения с третьим входом блока определения вида искажения, первый выход схемы сравнения соединен с первым входом блока итеративиого вычисления суммы и через блок подсчета количества единиц с первым входом блока вычитания и с первым входом первой дополнительной схемы сравнения, выход блока определения вычета соединен с вторыми входами блока вычитания и первой дополнительной схемы сравнения, со входом блока определения начала пакета ошибок, с первыми входами коммутатора и второй дополнительной схемы сравнения и через третью дополнительную схему сравнения с четвертым входом блока определения вида искажений, пятый и шестой входы которого соединены с выходами первой дополнительной схемы сравнения, первый выход блока определения вида искажения соединен с третьим входом блока выделения информационной части сообщения, второй выход блока определения вида искажения соединен с вторыми входами блока итеративного вычисления суммы, блока .коррекции и коммутатора, тр.етий вход которого соединен с выходом блока вычитания, а четвертый и пятый входы соединены с выходами блока определения .нача.ла пакета ошибок второй вход и первый и второй выходы второй дополнительной схемы сравнения соединены соответственно с первым выходом и третьим и четвертым входами блока итеративного вычисления суммы, второй выход ко-, торого соединен с первым входом элемента «И, третий выход второй до.полнитель.ной схемы сравнения соединен с вторым входом элемента «И, выход которого соединен с шестым входом коммутатора, выход коммутатора соединен с третьим входом блока коррекции, выход которого соединен с выходом устройства.

Ч/

Вход

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования кода | 1974 |

|

SU537450A1 |

| Устройство для кодирования | 1974 |

|

SU488211A1 |

| Устройство для формирования кода | 1974 |

|

SU526883A1 |

| СПОСОБ И УСТРОЙСТВО ОБЕСПЕЧЕНИЯ ПОМЕХОУСТОЙЧИВОСТИ ОБРАБОТКИ ДАННЫХ НА ОСНОВЕ КРИПТОКОДОВЫХ КОНСТРУКЦИЙ В КОМПЛЕКСНОЙ ПЛОСКОСТИ | 2022 |

|

RU2787941C1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Способ передачи данных в системе цифровой радиосвязи на основе кодов с низкой плотностью проверок на четность и способ перемежения кодовых символов | 2018 |

|

RU2700398C1 |

| Устройство для кодирования | 1974 |

|

SU529566A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство передачи данных на основе кодов с низкой плотностью проверок на четность | 2019 |

|

RU2713573C1 |

f

Bbiwd -«

Авторы

Даты

1976-03-30—Публикация

1974-02-12—Подача