Область техники, к которой относится изобретение

Предлагаемое изобретение относится к области радио- и электросвязи, а именно к области способов и устройств криптографической защиты информации, передаваемой по открытым каналам связи либо хранящейся на носителях информации.

Уровень техники

а) Описание аналогов

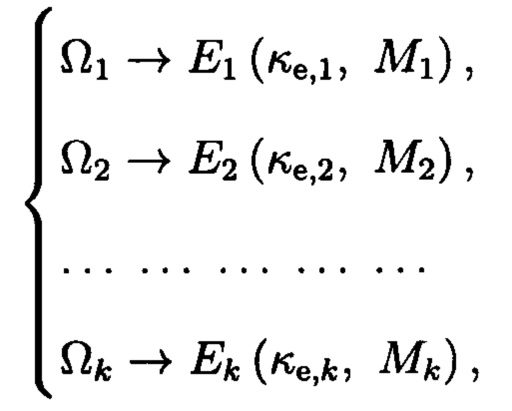

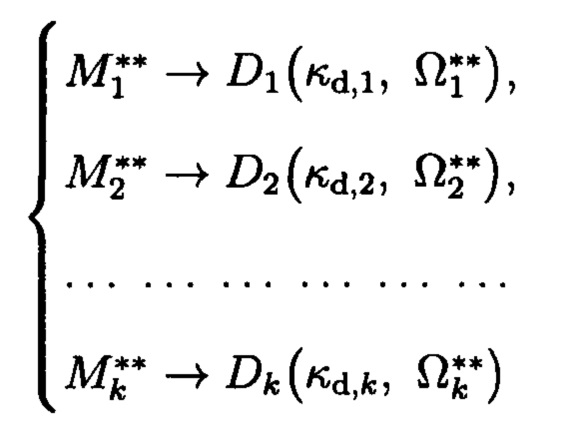

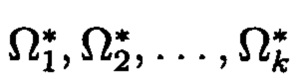

Известны способы криптографической защиты информации, которые основаны на блочных шифрах (DES, AES, Serpent, Twofish, Кузнечик, Магма) [Ferguson N., Schneier В., T. Kohno Cryptography Engineering. Design Principles and Practical Applications, Second Edition, New York, John Wiley & Sons, Inc., 2010; ГОСТ P 34.12-2015 Информационная технология. Криптографическая защита информации. Блочные шифры], включающие в себя следующие этапы: зашифрование открытого и при необходимости дополненного текста М, представленного в виде блоков фиксированной длины М={М1||М2||…Mk} где || - операция конкатенации, k - количество блоков открытого текста М, генерация ключа зашифрования κе, получение блоков шифртекста Ω1, Ω2, …, Ωk по следующему правилу:

извлечение открытого текста М из последовательности блоков шифртекста Ω1, Ω2, …, Ωk с помощью ключа расшифрования κd:

Mi → D(κd, Ωi),

выполнение обратной процедуры дополнения, где i=1, 2, …, k. Таким образом, обеспечивается защита информации, содержащейся в открытом тексте М, при передаче по открытым каналам связи. Для защиты от навязывания ложной информации, подмены передаваемой информации или изменения хранимых данных в указанных способах предусмотрены следующие режимы работы:

- режим гаммирования с обратной связью по выходу (Output Feedback, OFB);

- режим простой замены с: зацеплением (Cipher Block Chaining, СВС);

- режим гаммирования с обратной связью по шифртексту (Cipher Feedback, CFB);

- режим выработки имитовставки, хэш-кода (Message Authentication Code algorithm).

Недостатками таких способов являются:

- отсутствие возможности исправления искажений в блоках шифртекста, обусловленных преднамеренными воздействиями злоумышленника или влиянием случайных помех при передаче по открытым каналам связи;

- возможность размножения ошибок, когда один (несколько) ошибочный бит в одном блоке шифртекста оказывает влияние на расшифрование последующих блоков открытого текста;

- отсутствие возможности восстановления достоверной информации при использовании в системах передачи информации без обратной связи.

Известны способы защиты информации, основанные на теории алгебраического кодирования (криптосистема Мак-Элиса. схема Нидеррайтера, криптосистема Рао-Нама и их модификации) [McEliece R.J. A public-key cryptosystem based on algebraic coding theory, DSN Progress Report 42-44, Jet Prop. Lab., Calif. Inst. Technol. 1978. - pp. 114-116; Niederreiter H. Knapsack-Type Cryptosystem and Algebraic Coding Theory, Probl. Control and Inform. Theory. 1986. - pp. 19-34; Rao T.R.N., Nam K.H. Private-key algebraic-coded cryptosystem. Advances in Cryptology - CRYPTO 86, New-York. - NY: Springer. 1986. - pp. 35-48]. Реализация данных схем основана на сложности декодирования полных линейных кодов (кодов общего положения).

Недостатками таких способов являются:

- отсутствие возможности гарантированного обеспечения криптографической стойкости защищаемой информации (например, атака Сидельникова В.М. и Шестакова С.О. на систему Мак-Элиса);

- сложность в реализации, обусловленная высокими размерностями системы;

- длина блока шифртекста значительно превышает длину открытого текста;

- достаточно высокая чувствительность блоков шифртекста к искажениям, возникающим в канале связи.

Известен способ защищенной передачи зашифрованной информации по каналам связи [Патент РФ №2620730 публ. 29.05.2017], в котором для выполнения процедуры зашифрования блоков открытого текста M1(z), M2(z), …, Mk(z) по соответствующему ключу κе(z) применяется k процедур зашифрования, блоки шифртекста Ω1(z), Ω2(z), …, Ωk(z) интерпретируются как наименьшие вычеты по сгенерированным, упорядоченным по величине степеней, взаимно простым основаниям полиномам mi(z) (i=1, 2, …, k), образующие информационный суперблок модулярного кода из последовательности блоков шифртекста Ω1(z), Ω2(z), …, Ωk(z), после операции расширения формируются избыточные блоки данных ωk+1(z), ωk+2(z), …, ωk+r(z), полученная совокупность блоков шифртекста и избыточных блоков данных Ω1(z), …, Ωk(z), ωk+1(z), …, ωk+r(z) образует кодовый вектор модулярного кода, передаваемый получателю сообщения по k+r из А каналов передачи информации, который на приемной стороне обеспечивает обнаружение (преднамеренных и непреднамеренных) воздействий злоумышленника на защищаемую информацию и, при необходимости, восстановление достоверных данных, передаваемых по каналам связи.

К недостатку способа следует отнести отсутствие возможности защиты информации от имитирующих воздействий злоумышленника, обусловленной наличием «одного» правила кодирования, соответствующего модулярному полиномиальному коду, вследствие чего, злоумышленнику с целью навязывания ложных сообщений необходимо перехватить информационный суперблок модулярного кода для вычисления избыточных блоков данных.

б) Описание ближайшего аналога (прототипа)

Наиболее близким по своей технической сущности к заявленному техническому решению и принятым за прототип является способ, описанный в [Патент РФ №2764960 публ. 24.01.2022].

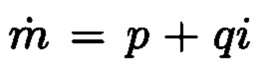

В рассматриваемом способе-прототипе защита информации осуществляется представлением сообщения М в виде блоков фиксированной длины М={M1||M2|| … ||Mk}, применением k процедур зашифрования к блокам открытого текста M1, М2, …, Mk по соответствующему ключу κе,i (i = 1, 2, …, k), вычислением от полученных блоков шифртекста Ω1, Ω2, …, Ωk имитовставки Н по соответствующему ключу  , представлением полученных блоков шифртекста и имитовставки Ω1, Ω2, …, Ωk, Н в виде наименьших неотрицательных вычетов по сгенерированным, упорядоченным по величине, взаимно простым модулям mi (i = 1, 2, …, k), формированием информационного суперблока модулярного кода Ω1, Ω2, …, Ωk, Н, выполнением операции расширения информационного суперблока модулярного кода и получением избыточного блока данных ωk+1, представлением полученных имитовставки Н и избыточного блока данных ωk+1 в виде псевдокомплексного числа ωk+1 + Hi, реализацией процедуры овеществления с получением из псевдокомплексного числа ωk+1 + Hi целого вещественного вычета h по соответствующему модулю

, представлением полученных блоков шифртекста и имитовставки Ω1, Ω2, …, Ωk, Н в виде наименьших неотрицательных вычетов по сгенерированным, упорядоченным по величине, взаимно простым модулям mi (i = 1, 2, …, k), формированием информационного суперблока модулярного кода Ω1, Ω2, …, Ωk, Н, выполнением операции расширения информационного суперблока модулярного кода и получением избыточного блока данных ωk+1, представлением полученных имитовставки Н и избыточного блока данных ωk+1 в виде псевдокомплексного числа ωk+1 + Hi, реализацией процедуры овеществления с получением из псевдокомплексного числа ωk+1 + Hi целого вещественного вычета h по соответствующему модулю  и формированием криптокодовых конструкций - имитоустойчивой последовательности шифрованного текста, обеспечивающей контроль имитирующих воздействий злоумышленника и достоверное восстановление блоков шифртекста.

и формированием криптокодовых конструкций - имитоустойчивой последовательности шифрованного текста, обеспечивающей контроль имитирующих воздействий злоумышленника и достоверное восстановление блоков шифртекста.

Недостатками данного способа являются:

- сложность реализации процедуры контроля и коррекции ошибок, обусловленной необходимостью вычисления синдрома ошибки на основе базисного представления числа Ω;

- низкий уровень помехоустойчивости передачи аутентифицированных сообщений при возникновении искажений в сообщении и (или) имитовставке;

- ограниченная возможность установления конкретного места изменения в блоках шифртекста (локализация ошибки) при отклонении имитовставки от требуемого вида.

Из уровня техники широко известно устройство защищенной обработки информации. Так, в [Massey J.L. An introduction to contemporary cryptology. Proc. IEEE. 1988. - pp. 533-549] предложено устройство, содержащее на передающей стороне источник сообщений, порождающий открытый текст, рандомизатор, шифратор, а также генератор ключевой гаммы, выход источника сообщений подключен к первому входу шифратора, ко второму входа которого подключен выход рандомизатора, соответственно к третьему входу шифратора подключен выход генератора ключевой гаммы, причем выход шифратора через «открытую» линию связи на приемной стороне подключен к первому входу дешифратора, ко второму входу которого через защищенную линию связи подключен выход блока ключевой гаммы, при этом выход дешифратора подключен к входу источника сообщений.

Недостатком устройства является низкая помехозащищенность.

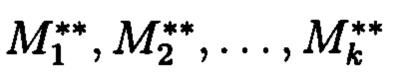

Наиболее близким по технической сущности является устройство формирования криптокодовых конструкций дня имитоустойчивой передачи данных по каналам связи [Патент РФ №2764960 публ. 24.01.2022], содержащее на передающей стороне криптокодовый преобразователь информации (фиг. 1), состоящий из буфера ввода открытого текста, блока хранения управляющих параметров, процессора, реализующего функции, представленные в виде функциональных блоков: препроцессора открытого текста, блока шифрования, блока выработки имитовставки блока шифрования, генератора простых чисел, блока расширения модулярного кода, процессора ключей шифрования, буфера вывода имитовставки, блока овеществления, счетчика блоков текста; буфера вывода шифртекста, блок (таблицы) кодовых символов, буфера вывода избыточных блоков данных, коммутатора объединения, при этом буфер ввода открытого текста, вход которого является входом криптокодового преобразователя информации, на который поступает открытый текст, выход которого подключен к первому входу препроцессора открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, при этом к третьему входу препроцессора открытого текста подключен первый выход блока хранения управляющих параметров (N), выход препроцессора открытого текста подключен к первому входу блока шифрования, ко второму входу которого подключен второй выход блока хранения управляющих параметров (κе,i,  - итерационные ключи зашифрования и формирования имитовставки, выработанные на основании секретного ключа (

- итерационные ключи зашифрования и формирования имитовставки, выработанные на основании секретного ключа ( )), при этом первый выход блока шифрования подключен к входу буфера вывода блоков шифртекста, второй выход блока шифрования подключен к первой группе (первому входу) входов блока расширения модулярного кода, ко второй группе (второй, третий входы) входов которого подключен первый и второй выходы генератора простых чисел (информационных и избыточных), к входу которого подключен третий выход блока хранения управляющих параметров (N); выход блока расширения модулярного кода подключен к первому входу блока овеществления, ко второму входу которого подключен выход буфера вывода имитовставки, вход которого подключен к выхода блока выработки имитовставки блока шифрования; при этом к третьей группе (третий, четвертый входы) входов блока овеществления подключены третий и четвертый выходы генератора простых чисел; к четвертой группе (пятый и шестой входы) входов блока овеществления подключена группа (четвертый и пятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры р и q); при этом к третьей группе (четвертый, пятый, шестой входы) входов блока расширения модулярного кода подключена группа (шестой, седьмой, восьмой выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mk+1); выход буфера вывода блоков шифртекста и выход буфера вывода избыточных данных подключены к первому и второму входам коммутатора объединения, выход которого является выходом криптокодового преобразователя информации, с выхода которого сформированные криптокодовые конструкции (имитоустойчивая последовательность шифрованного текста) поступают в канал связи; счетчик блоков текста отслеживает номер обрабатываемого блока, а на приемной стороне - криптокодовый преобразователь информации, состоящий из коммутатора разделения, буфера ввода избыточных данных, блока хранения управляющих параметров, буфера ввода шифртекста, процессора, реализующего функции, представленные в виде функциональных блоков: препроцессора избыточных данных, генератора простых чисел, процессора ключей шифрования, препроцессора шифртекста, блока комплексификации, блока обнаружения и коррекции искажений, блока расшифрования, блока выработки имитовставки блока расшифрования, счетчика блоков текста; буфера вывода открытого текста, блока (таблицы) кодовых символов, при этом первый выход коммутатора разделения подключен к входа буфера ввода избыточных данных, выход которого подключен к первому входу препроцессора избыточных данных, ко второму входу которого подключен первый выход блока хранения управляющих параметров (N), при этом выход препроцессора избыточных данных подключен к первому входу блока комплексификации, ко второй группе (второй, третий входы) входов которого подключен второй и третий выходы блока хранения управляющих параметров (р, q); к третьей группе (четвертый, пятый входы) входов блока комплексификации подключен первый и второй выходы генератора простых чисел, при этом первый выход блока комплексификации подключен к первому входу блока выработки имитовставки блока расшифрования шифртекста, выход которого подключен к первому входу блока обнаружения и коррекции искажений, ко второму входа которого подключен второй выход блока комплексификации; к третьей группе (третий, четвертый входы) входов блока обнаружения и коррекции искажений подключен третий и четвертый выходы генератора простых чисел (информационных и избыточных), к входу которого подключен четвертый выход блока хранения управляющих параметров (N); при этом второй выход коммутатора разделения подключен к входу буфера ввода блоков шифртекста, выход которого подключен к первому входу препроцессора шифртекста, ко второму входу которого подключен пятый выход блока хранения управляющих параметров (N); первый выход препроцессора шифртекста подключен ко второму входу блока выработки имитовставки блока расшифрования шифртекста, при этом второй выход препроцессора шифртекста подключен к четвертой группе (пятому входу) входов блока обнаружения и коррекции искажений, соответствующий выход которого подключен к первому входу блока расшифрования, ко второму входу которого подключен шестой выход блока хранения управляющих параметров (κd,i,

)), при этом первый выход блока шифрования подключен к входу буфера вывода блоков шифртекста, второй выход блока шифрования подключен к первой группе (первому входу) входов блока расширения модулярного кода, ко второй группе (второй, третий входы) входов которого подключен первый и второй выходы генератора простых чисел (информационных и избыточных), к входу которого подключен третий выход блока хранения управляющих параметров (N); выход блока расширения модулярного кода подключен к первому входу блока овеществления, ко второму входу которого подключен выход буфера вывода имитовставки, вход которого подключен к выхода блока выработки имитовставки блока шифрования; при этом к третьей группе (третий, четвертый входы) входов блока овеществления подключены третий и четвертый выходы генератора простых чисел; к четвертой группе (пятый и шестой входы) входов блока овеществления подключена группа (четвертый и пятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры р и q); при этом к третьей группе (четвертый, пятый, шестой входы) входов блока расширения модулярного кода подключена группа (шестой, седьмой, восьмой выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mk+1); выход буфера вывода блоков шифртекста и выход буфера вывода избыточных данных подключены к первому и второму входам коммутатора объединения, выход которого является выходом криптокодового преобразователя информации, с выхода которого сформированные криптокодовые конструкции (имитоустойчивая последовательность шифрованного текста) поступают в канал связи; счетчик блоков текста отслеживает номер обрабатываемого блока, а на приемной стороне - криптокодовый преобразователь информации, состоящий из коммутатора разделения, буфера ввода избыточных данных, блока хранения управляющих параметров, буфера ввода шифртекста, процессора, реализующего функции, представленные в виде функциональных блоков: препроцессора избыточных данных, генератора простых чисел, процессора ключей шифрования, препроцессора шифртекста, блока комплексификации, блока обнаружения и коррекции искажений, блока расшифрования, блока выработки имитовставки блока расшифрования, счетчика блоков текста; буфера вывода открытого текста, блока (таблицы) кодовых символов, при этом первый выход коммутатора разделения подключен к входа буфера ввода избыточных данных, выход которого подключен к первому входу препроцессора избыточных данных, ко второму входу которого подключен первый выход блока хранения управляющих параметров (N), при этом выход препроцессора избыточных данных подключен к первому входу блока комплексификации, ко второй группе (второй, третий входы) входов которого подключен второй и третий выходы блока хранения управляющих параметров (р, q); к третьей группе (четвертый, пятый входы) входов блока комплексификации подключен первый и второй выходы генератора простых чисел, при этом первый выход блока комплексификации подключен к первому входу блока выработки имитовставки блока расшифрования шифртекста, выход которого подключен к первому входу блока обнаружения и коррекции искажений, ко второму входа которого подключен второй выход блока комплексификации; к третьей группе (третий, четвертый входы) входов блока обнаружения и коррекции искажений подключен третий и четвертый выходы генератора простых чисел (информационных и избыточных), к входу которого подключен четвертый выход блока хранения управляющих параметров (N); при этом второй выход коммутатора разделения подключен к входу буфера ввода блоков шифртекста, выход которого подключен к первому входу препроцессора шифртекста, ко второму входу которого подключен пятый выход блока хранения управляющих параметров (N); первый выход препроцессора шифртекста подключен ко второму входу блока выработки имитовставки блока расшифрования шифртекста, при этом второй выход препроцессора шифртекста подключен к четвертой группе (пятому входу) входов блока обнаружения и коррекции искажений, соответствующий выход которого подключен к первому входу блока расшифрования, ко второму входу которого подключен шестой выход блока хранения управляющих параметров (κd,i,  ), к первому входу которого подключен процессор ключей шифрования, на вход которого поступает секретный ключ (

), к первому входу которого подключен процессор ключей шифрования, на вход которого поступает секретный ключ ( )), при этом выход блока расшифрования подключен к первому входу буфера вывода блоков открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, выход которого является выходом криптокодового преобразователя информации, с выхода которого поступает открытый текст; при этом к пятой группе (шестой, седьмой, восьмой входы) входов блока обнаружения и коррекции искажений подключена группа (седьмой, восьмой, девятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mi+r); счетчик блоков текста отслеживает номер обрабатываемого блока.

)), при этом выход блока расшифрования подключен к первому входу буфера вывода блоков открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, выход которого является выходом криптокодового преобразователя информации, с выхода которого поступает открытый текст; при этом к пятой группе (шестой, седьмой, восьмой входы) входов блока обнаружения и коррекции искажений подключена группа (седьмой, восьмой, девятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mi+r); счетчик блоков текста отслеживает номер обрабатываемого блока.

К основному недостатку устройства-прототипа следует отнести ограниченную возможность установления конкретного места изменения в блоках шифртекста (локализация ошибки) при отклонении имитовставки от требуемого вида.

Раскрытие изобретения

а) Технический результат, на достижение которого направлено изобретение

Целью заявляемого технического решения является повышение помехоустойчивости способа и устройства обработки шифрованной информации к деструктивным воздействиям.

б) Совокупность существенных признаков

Технический результат изобретения достигается тем, что:

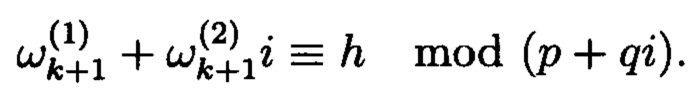

1. В известном способе имитоустойчивой передачи информации по каналам связи защита информации осуществляется представлением сообщения М в виде блоков фиксированной длины М={M1||M2|| … ||Mk}, применением k процедур зашифрования к блокам открытого текста M1, M2, …, Mk по соответствующему ключу κе,i (i=1, 2, …, k), вычислением от полученных блоков шифртекста Ω1, Ω2, …, Ωk имитовставки Н по соответствующему ключу  , представлением полученных блоков шифртекста и имитовставки Ω1, Ω2, …, Ωk, Н в виде наименьших неотрицательных вычетов по сгенерированным, упорядоченным по величине, взаимно простым модулям mi (i = 1, 2, …, k), формированием информационного суперблока модулярного кода Ω1, Ω2, …, Ωk, Н, выполнением операции расширения информационного суперблока модулярного кода и получением избыточного блока данных ωk+1, представлением полученных имитовставки Н и избыточного блока данных ωk+1 в виде псевдокомплексного числа ωk+1 + Hi, реализацией процедуры овеществления с получением из псевдокомплексного числа ωk+1 + Hi целого вещественного вычета h по соответствующему модулю

, представлением полученных блоков шифртекста и имитовставки Ω1, Ω2, …, Ωk, Н в виде наименьших неотрицательных вычетов по сгенерированным, упорядоченным по величине, взаимно простым модулям mi (i = 1, 2, …, k), формированием информационного суперблока модулярного кода Ω1, Ω2, …, Ωk, Н, выполнением операции расширения информационного суперблока модулярного кода и получением избыточного блока данных ωk+1, представлением полученных имитовставки Н и избыточного блока данных ωk+1 в виде псевдокомплексного числа ωk+1 + Hi, реализацией процедуры овеществления с получением из псевдокомплексного числа ωk+1 + Hi целого вещественного вычета h по соответствующему модулю  и формированием криптокодовых конструкций - имитоустойчивой последовательности шифрованного текста, обеспечивающей контроль имитирующих воздействий злоумышленника и достоверное восстановление блоков шифртекста. Новым является то, что для выполнения операции расширения - вычисления 1-го и 2-го избыточных блоков данных

и формированием криптокодовых конструкций - имитоустойчивой последовательности шифрованного текста, обеспечивающей контроль имитирующих воздействий злоумышленника и достоверное восстановление блоков шифртекста. Новым является то, что для выполнения операции расширения - вычисления 1-го и 2-го избыточных блоков данных  (j=1, 2) используется последовательность блоков шифртекста Ω1, Ω2, …, Ωk (k ∈

(j=1, 2) используется последовательность блоков шифртекста Ω1, Ω2, …, Ωk (k ∈  : k≥2) или ее фрагменты в зависимости от установленных параметров. Новым является то, что для получения 1-го и 2-го избыточных блоков данных

: k≥2) или ее фрагменты в зависимости от установленных параметров. Новым является то, что для получения 1-го и 2-го избыточных блоков данных  (j=1, 2) осуществляется подбор коэффициентов

(j=1, 2) осуществляется подбор коэффициентов  (j=1, 2) линейной формы в совокупности с процедурой формирования оснований

(j=1, 2) линейной формы в совокупности с процедурой формирования оснований  (j=1, 2). Новым является также и то, что 1-ый и 2-ой избыточные блоки данных

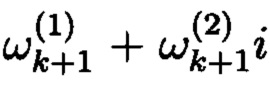

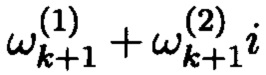

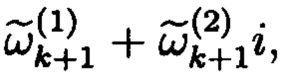

(j=1, 2). Новым является также и то, что 1-ый и 2-ой избыточные блоки данных  (j=1, 2) представляются как псевдокомплексное число

(j=1, 2) представляются как псевдокомплексное число  , которое подвергается процедуре овеществления с получением вещественного вычета h по соответствующему модулю

, которое подвергается процедуре овеществления с получением вещественного вычета h по соответствующему модулю  и последующим формированием криптокодовых конструкций - помехоустойчивой последовательности шифрованного текста. Новым является то, что на приемной стороне принятый вещественный вычет h* преобразуется в псевдокомплексное число

и последующим формированием криптокодовых конструкций - помехоустойчивой последовательности шифрованного текста. Новым является то, что на приемной стороне принятый вещественный вычет h* преобразуется в псевдокомплексное число  , а от принятой последовательности блоков шифртекста

, а от принятой последовательности блоков шифртекста  (k ∈

(k ∈  : k≥2) или ее фрагментов вырабатываются 1-ый и 2-ой избыточные блоки данных

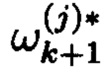

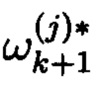

: k≥2) или ее фрагментов вырабатываются 1-ый и 2-ой избыточные блоки данных  (j=1, 2). Новым является также и то, что от принятых

(j=1, 2). Новым является также и то, что от принятых  и выработанных

и выработанных  (j=1, 2) (i=1, 2) избыточных блоков данных на приемной стороне образуется разность и формируются синдромы ошибок δ(j) (j=1, 2). Новым является то, что по заданным основаниям

(j=1, 2) (i=1, 2) избыточных блоков данных на приемной стороне образуется разность и формируются синдромы ошибок δ(j) (j=1, 2). Новым является то, что по заданным основаниям  (j=1, 2) строятся таблицы допустимых ошибок, по которым с помощью синдромов ошибок δ(j) (j=1, 2) осуществляется поиск, локализация и исправление искаженных блоков данных в принятой последовательности

(j=1, 2) строятся таблицы допустимых ошибок, по которым с помощью синдромов ошибок δ(j) (j=1, 2) осуществляется поиск, локализация и исправление искаженных блоков данных в принятой последовательности  по соответствующим основаниям

по соответствующим основаниям  (j=1, 2). Новым является то, что при превышении корректирующих способностей криптокодовых конструкций формируется запрос на повторную передачу искаженных блоков шифртекста, локализованных синдромами ошибок.

(j=1, 2). Новым является то, что при превышении корректирующих способностей криптокодовых конструкций формируется запрос на повторную передачу искаженных блоков шифртекста, локализованных синдромами ошибок.

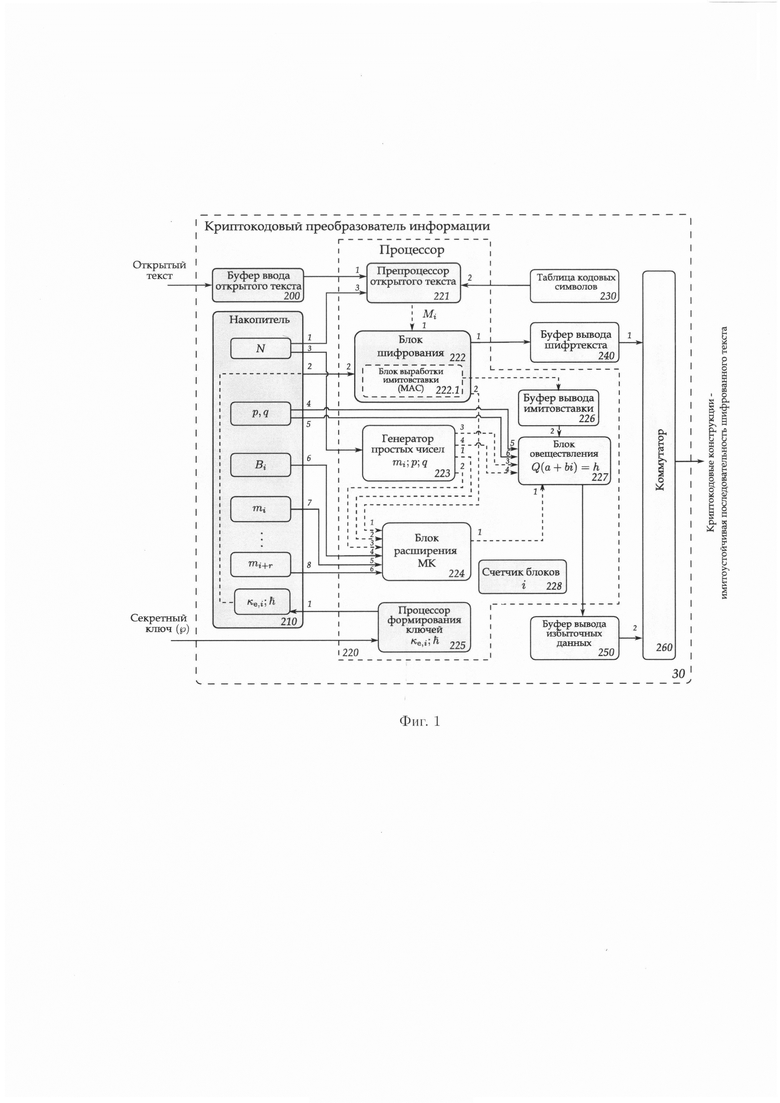

2. Устройство формирования криптокодовых конструкций для имитоустойчивой передачи данных по канатам связи [Патент РФ №2764960 публ. 24.01.2022], содержащее па передающей стороне криптокодовый преобразователь информации (фиг. 1), состоящий из буфера ввода открытого текста, блока хранения управляющих параметров, процессора, реализующего функции, представленные в виде функциональных блоков: препроцессора открытого текста, блока шифрования, блока выработки имитовставки блока шифрования, генератора простых чисел, блока расширения модулярного кода, процессора ключей шифрования, буфера вывода имитовставки, блока овеществления, счетчика блоков текста; буфера вывода шифртекста, блок (таблицы) кодовых символов, буфера вывода избыточных блоков данных, коммутатора объединения, при этом буфер ввода открытого текста, вход которого является входом криптокодового преобразователя информации, на который поступает открытый текст, выход которого подключен к первому входу препроцессора открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, при этом к третьему входу препроцессора открытого текста подключен первый выход блока хранения управляющих параметров (N), выход препроцессора открытого текста подключен к первому входу блока шифрования, ко второму входу которого подключен второй выход блока хранения управляющих параметров (κе,i,  - итерационные ключи зашифрования и формирования имитовставки, выработанные на основании секретного ключа (

- итерационные ключи зашифрования и формирования имитовставки, выработанные на основании секретного ключа ( )), при этом первый выход блока шифрования подключен к входу буфера вывода блоков шифртекста, второй выход блока шифрования подключен к первой группе (первому входу) входов блока расширения модулярного кода, ко второй группе (второй, третий входы) входов которого подключен первый и второй выходы генератора простых чисел (информационных и избыточных), к входу которого подключен третий выход блока хранения управляющих параметров (N); выход блока расширения модулярного кода подключен к первому входу блока овеществления, ко второму входу которого подключен выход буфера вывода имитовставки, вход которого подключен к выходу блока выработки имитовставки блока шифрования; при этом к третьей группе (третий, четвертый входы) входов блока овеществления подключены третий и четвертый выходы генератора простых чисел; к четвертой группе (пятый и шестой входы) входов блока овеществления подключена группа (четвертый и пятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры р и q); при этом к третьей группе (четвертый, пятый, шестой входы) входов блока расширения модулярного кода подключена группа (шестой, седьмой, восьмой выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mk+1); выход буфера вывода блоков шифртекста и выход буфера вывода избыточных данных подключены к первому и второму входам коммутатора объединения, выход которого является выходом криптокодового преобразователя информации, с выхода которого сформированные криптокодовые конструкции (имитоустойчивая последовательность шифрованного текста) поступают в канал связи; счетчик блоков текста отслеживает номер обрабатываемого блока, а на приемной стороне - криптокодовый преобразователь информации, состоящий из коммутатора разделения, буфера ввода избыточных данных, блока хранения управляющих параметров, буфера ввода шифртекста, процессора, реализующего функции, представленные в виде функциональных блоков: препроцессора избыточных данных, генератора простых чисел, процессора ключей шифрования, препроцессора шифртекста, блока комплексификации, блока обнаружения и коррекции искажений, блока расшифрования, блока выработки имитовставки блока расшифрования, счетчика блоков текста; буфера вывода открытого текста, блока (таблицы) кодовых символов, при этом первый выход коммутатора разделения подключен к входу буфера ввода избыточных данных, выход которого подключен к первому входу препроцессора избыточных данных, ко второму входу которого подключен первый выход блока хранения управляющих параметров (N), при этом выход препроцессора избыточных данных подключен к первому входу блока комплексификации, ко второй группе (второй, третий входы) входов которого подключен второй и третий выходы блока хранения управляющих параметров (р, q); к третьей группе (четвертый, пятый входы) входов блока комплексификации подключен первый и второй выходы генератора простых чисел, при этом первый выход блока комплексификации подключен к первому входу блока выработки имитовставки блока расшифрования шифртекста, выход которого подключен к первому входу блока обнаружения и коррекции искажений, ко второму входу которого подключен второй выход блока комплексификации; к третьей группе (третий, четвертый входы) входов блока обнаружения и коррекции искажений подключен третий и четвертый выходы генератора простых чисел (информационных и избыточных), к входу которого подключен четвертый выход блока хранения управляющих параметров (N); при этом второй выход коммутатора разделения подключен к входу буфера ввода блоков шифртекста, выход которого подключен к первому входу препроцессора шифртекста, ко второму входу которого подключен пятый выход блока хранения управляющих параметров (N); первый выход препроцессора шифртекста подключен ко второму входу блока выработки имитовставки блока расшифрования шифртекста, при этом второй выход препроцессора шифртекста подключен к четвертой группе (пятому входу) входов блока обнаружения и коррекции искажений, соответствующий выход которого подключен к первому входу блока расшифрования, ко второму входу которого подключен шестой выход блока хранения управляющих параметров (κd,i,

)), при этом первый выход блока шифрования подключен к входу буфера вывода блоков шифртекста, второй выход блока шифрования подключен к первой группе (первому входу) входов блока расширения модулярного кода, ко второй группе (второй, третий входы) входов которого подключен первый и второй выходы генератора простых чисел (информационных и избыточных), к входу которого подключен третий выход блока хранения управляющих параметров (N); выход блока расширения модулярного кода подключен к первому входу блока овеществления, ко второму входу которого подключен выход буфера вывода имитовставки, вход которого подключен к выходу блока выработки имитовставки блока шифрования; при этом к третьей группе (третий, четвертый входы) входов блока овеществления подключены третий и четвертый выходы генератора простых чисел; к четвертой группе (пятый и шестой входы) входов блока овеществления подключена группа (четвертый и пятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры р и q); при этом к третьей группе (четвертый, пятый, шестой входы) входов блока расширения модулярного кода подключена группа (шестой, седьмой, восьмой выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mk+1); выход буфера вывода блоков шифртекста и выход буфера вывода избыточных данных подключены к первому и второму входам коммутатора объединения, выход которого является выходом криптокодового преобразователя информации, с выхода которого сформированные криптокодовые конструкции (имитоустойчивая последовательность шифрованного текста) поступают в канал связи; счетчик блоков текста отслеживает номер обрабатываемого блока, а на приемной стороне - криптокодовый преобразователь информации, состоящий из коммутатора разделения, буфера ввода избыточных данных, блока хранения управляющих параметров, буфера ввода шифртекста, процессора, реализующего функции, представленные в виде функциональных блоков: препроцессора избыточных данных, генератора простых чисел, процессора ключей шифрования, препроцессора шифртекста, блока комплексификации, блока обнаружения и коррекции искажений, блока расшифрования, блока выработки имитовставки блока расшифрования, счетчика блоков текста; буфера вывода открытого текста, блока (таблицы) кодовых символов, при этом первый выход коммутатора разделения подключен к входу буфера ввода избыточных данных, выход которого подключен к первому входу препроцессора избыточных данных, ко второму входу которого подключен первый выход блока хранения управляющих параметров (N), при этом выход препроцессора избыточных данных подключен к первому входу блока комплексификации, ко второй группе (второй, третий входы) входов которого подключен второй и третий выходы блока хранения управляющих параметров (р, q); к третьей группе (четвертый, пятый входы) входов блока комплексификации подключен первый и второй выходы генератора простых чисел, при этом первый выход блока комплексификации подключен к первому входу блока выработки имитовставки блока расшифрования шифртекста, выход которого подключен к первому входу блока обнаружения и коррекции искажений, ко второму входу которого подключен второй выход блока комплексификации; к третьей группе (третий, четвертый входы) входов блока обнаружения и коррекции искажений подключен третий и четвертый выходы генератора простых чисел (информационных и избыточных), к входу которого подключен четвертый выход блока хранения управляющих параметров (N); при этом второй выход коммутатора разделения подключен к входу буфера ввода блоков шифртекста, выход которого подключен к первому входу препроцессора шифртекста, ко второму входу которого подключен пятый выход блока хранения управляющих параметров (N); первый выход препроцессора шифртекста подключен ко второму входу блока выработки имитовставки блока расшифрования шифртекста, при этом второй выход препроцессора шифртекста подключен к четвертой группе (пятому входу) входов блока обнаружения и коррекции искажений, соответствующий выход которого подключен к первому входу блока расшифрования, ко второму входу которого подключен шестой выход блока хранения управляющих параметров (κd,i,  ), к первому входу которого подключен процессор ключей шифрования, на вход которого поступает секретный ключ (

), к первому входу которого подключен процессор ключей шифрования, на вход которого поступает секретный ключ ( )), при этом выход блока расшифрования подключен к первому входу буфера вывода блоков открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, выход которого является выходом криптокодового преобразователя информации, с выхода которого поступает открытый текст; при этом к пятой группе (шестой, седьмой, восьмой входы) входов блока обнаружения и коррекции искажений подключена группа (седьмой, восьмой, девятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mi+r); счетчик блоков текста отслеживает номер обрабатываемого блока, на передающей стороне введены блок параметров буфера, переключатель, функциональные блоки процессора: блок формирования оснований

)), при этом выход блока расшифрования подключен к первому входу буфера вывода блоков открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, выход которого является выходом криптокодового преобразователя информации, с выхода которого поступает открытый текст; при этом к пятой группе (шестой, седьмой, восьмой входы) входов блока обнаружения и коррекции искажений подключена группа (седьмой, восьмой, девятый выходы) выходов блока хранения управляющих параметров (предвычисленные параметры Bi, mi, mi+r); счетчик блоков текста отслеживает номер обрабатываемого блока, на передающей стороне введены блок параметров буфера, переключатель, функциональные блоки процессора: блок формирования оснований  , блок вычисления коэффициентов

, блок вычисления коэффициентов  , блок формирования оснований

, блок формирования оснований  , блок вычисления коэффициентов

, блок вычисления коэффициентов  , промежуточный буфер, блок расширения

, промежуточный буфер, блок расширения  , блок расширения

, блок расширения  , при этом буфер ввода открытого текста, вход которого является входом криптокодового преобразователя информации, на который поступает открытый текст, выход которого подключен к первому входу препроцессора открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, при этом к третьему входу препроцессора открытого текста подключен первый выход блока хранения управляющих параметров (N), выход препроцессора открытого текста подключен к первому входу блока шифрования, ко второму входу которого подключен выход процессора ключей шифрования (κе,i - итерационные ключи зашифрования, выработанные на основании секретного ключа (

, при этом буфер ввода открытого текста, вход которого является входом криптокодового преобразователя информации, на который поступает открытый текст, выход которого подключен к первому входу препроцессора открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, при этом к третьему входу препроцессора открытого текста подключен первый выход блока хранения управляющих параметров (N), выход препроцессора открытого текста подключен к первому входу блока шифрования, ко второму входу которого подключен выход процессора ключей шифрования (κе,i - итерационные ключи зашифрования, выработанные на основании секретного ключа ( )), при этом первый выход блока шифрования подключен к входу буфера вывода блоков шифртекста, второй выход блока шифрования подключен к первому входу промежуточного буфера, ко второму входу которого подключен выход блока параметров буфера, формируемые на основании управляющего воздействия (ρ); первая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения

)), при этом первый выход блока шифрования подключен к входу буфера вывода блоков шифртекста, второй выход блока шифрования подключен к первому входу промежуточного буфера, ко второму входу которого подключен выход блока параметров буфера, формируемые на основании управляющего воздействия (ρ); первая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения  , ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов

, ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов  , первый и второй входы которого подключены к первому и второму выходам блока формирования оснований

, первый и второй входы которого подключены к первому и второму выходам блока формирования оснований  , к входу которого подключен второй выход блока хранения управляющих параметров (N); третий и четвертый выходы блока формирования оснований

, к входу которого подключен второй выход блока хранения управляющих параметров (N); третий и четвертый выходы блока формирования оснований  подключены к третьей группе (k+3, k+4 входы) входов блока расширения

подключены к третьей группе (k+3, k+4 входы) входов блока расширения  , выход которого подключен к первому входу блока блока овеществления; вторая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения

, выход которого подключен к первому входу блока блока овеществления; вторая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения  , ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов

, ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов  , первый и второй входы которого подключены к первому и второму выходам блока формирования оснований

, первый и второй входы которого подключены к первому и второму выходам блока формирования оснований  , к входу которого подключен второй выход блока хранения управляющих параметров (N); третий и четвертый выходы блока формирования оснований

, к входу которого подключен второй выход блока хранения управляющих параметров (N); третий и четвертый выходы блока формирования оснований  подключены к третьей группе (k+3, k+4 входы) входов блока расширения

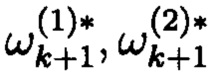

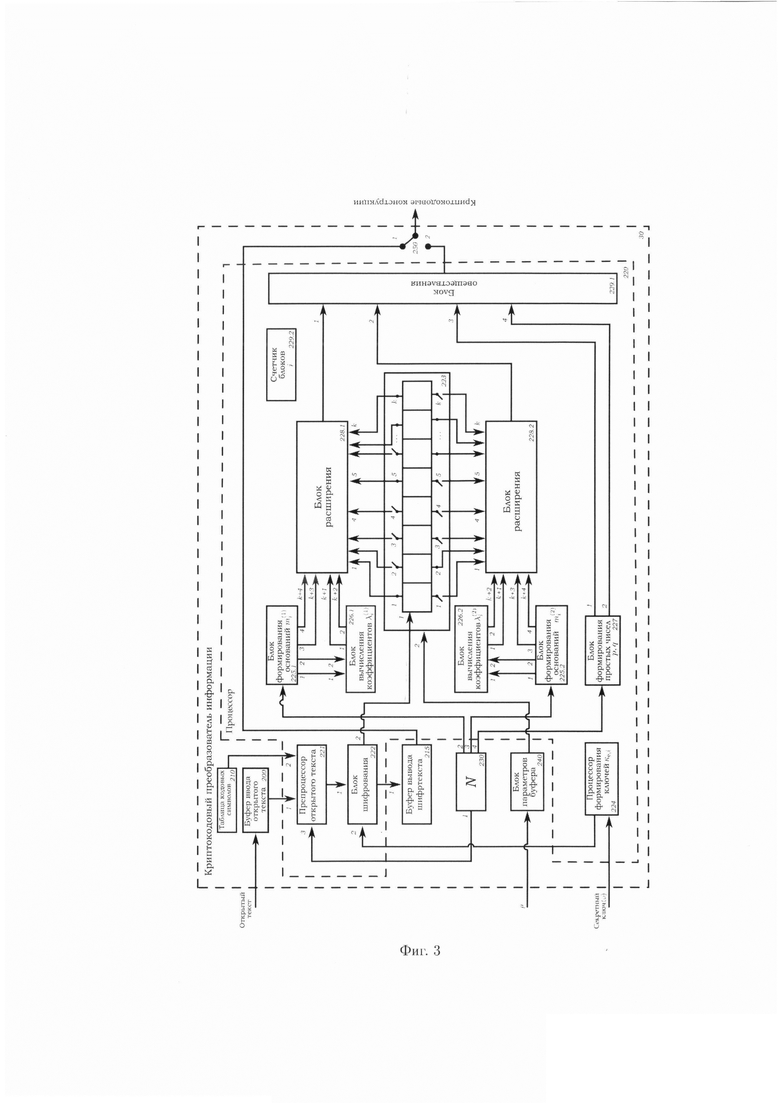

подключены к третьей группе (k+3, k+4 входы) входов блока расширения  , выход которого подключен к первому входу блока овеществления; при этом к третьему и четвертому входам блока овеществления подключены первый и второй выходы блока формирования простых чисел (р, q), к входу которого подключен третий выход блока хранения управляющих параметров (N); выход буфера вывода блоков шифртекста и выход блока овеществления подключены к первому и второму входам переключателя, выход которого является выходом криптокодового преобразователя информации, с выхода которого сформированные криптокодовые конструкции (помехоустойчивая последовательность шифрованного текста) поступают в канал связи; счетчик блоков текста отслеживает номер обрабатываемого блока, а на приемной стороне введены блок параметров буфера, переключатель и функциональные блоки процессора: блок формирования оснований

, выход которого подключен к первому входу блока овеществления; при этом к третьему и четвертому входам блока овеществления подключены первый и второй выходы блока формирования простых чисел (р, q), к входу которого подключен третий выход блока хранения управляющих параметров (N); выход буфера вывода блоков шифртекста и выход блока овеществления подключены к первому и второму входам переключателя, выход которого является выходом криптокодового преобразователя информации, с выхода которого сформированные криптокодовые конструкции (помехоустойчивая последовательность шифрованного текста) поступают в канал связи; счетчик блоков текста отслеживает номер обрабатываемого блока, а на приемной стороне введены блок параметров буфера, переключатель и функциональные блоки процессора: блок формирования оснований  , блок вычисления коэффициентов

, блок вычисления коэффициентов  , блок формирования оснований

, блок формирования оснований  , блок вычисления коэффициентов

, блок вычисления коэффициентов  , промежуточный буфер, блок расширения

, промежуточный буфер, блок расширения  , блок расширения

, блок расширения  , блок вычисления синдрома ошибки δ(1), блок вычисления синдрома ошибки δ(2), блок формирования запроса, при этом переключатель, вход которого является входом криптокодового преобразователя информации, на который из канала связи поступают криптокодовые конструкции - помехоустойчивая последовательность шифрованного текста, при этом первый выход переключателя подключен к первому входу блока обнаружения и коррекции искажений и к первому входу промежуточного буфера, ко второму входу которого подключен выход блока параметров буфера, формируемые на основании управляющего воздействия (ρ), к третьему входу промежуточного буфера подключен первый выход блока хранения управляющих параметров (N); первая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения

, блок вычисления синдрома ошибки δ(1), блок вычисления синдрома ошибки δ(2), блок формирования запроса, при этом переключатель, вход которого является входом криптокодового преобразователя информации, на который из канала связи поступают криптокодовые конструкции - помехоустойчивая последовательность шифрованного текста, при этом первый выход переключателя подключен к первому входу блока обнаружения и коррекции искажений и к первому входу промежуточного буфера, ко второму входу которого подключен выход блока параметров буфера, формируемые на основании управляющего воздействия (ρ), к третьему входу промежуточного буфера подключен первый выход блока хранения управляющих параметров (N); первая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения  , ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов

, ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов  , первый и второй входы которого подключены к первому и второму выходам блока формирования оснований

, первый и второй входы которого подключены к первому и второму выходам блока формирования оснований  , третий и четвертый выход блока формирования оснований

, третий и четвертый выход блока формирования оснований  подключены к третьей группе (k+3, k+4 входы) входов блока расширения

подключены к третьей группе (k+3, k+4 входы) входов блока расширения  , выход которого подключен к первому входу блока вычисления синдрома ошибки ко второму входу которого подключен пятый выход блока формирования оснований

, выход которого подключен к первому входу блока вычисления синдрома ошибки ко второму входу которого подключен пятый выход блока формирования оснований  , шестой и седьмой выходы блока формирования оснований

, шестой и седьмой выходы блока формирования оснований  подключены ко второму и третьему входам блока обнаружения и коррекции искажений, первый выход которого подключен к первому входу буфера вывода шифртекста; вторая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения

подключены ко второму и третьему входам блока обнаружения и коррекции искажений, первый выход которого подключен к первому входу буфера вывода шифртекста; вторая группа (1, 2, …, k выходы) выходов промежуточного буфера подключена к первой группе (1, 2, …, k входы) входов блока расширения  , ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов

, ко второй группе (k+1, k+2 входы) входов которого подключены первый и второй выходы блока вычисления коэффициентов  , первый и второй входы которого подключены к первому и второму выходам блока формирования оснований

, первый и второй входы которого подключены к первому и второму выходам блока формирования оснований  , третий и четвертый выходы блока формирования оснований

, третий и четвертый выходы блока формирования оснований  подключены к третьей группе (k+3, k+4 входы) входов блока расширения

подключены к третьей группе (k+3, k+4 входы) входов блока расширения  , выход которого подключен к первому входу блока вычисления синдрома ошибки δ(2), ко второму входу которого подключен пятый выход блока формирования оснований

, выход которого подключен к первому входу блока вычисления синдрома ошибки δ(2), ко второму входу которого подключен пятый выход блока формирования оснований  , шестой и седьмой выходы блока формирования оснований

, шестой и седьмой выходы блока формирования оснований  подключены к четвертому и пятому входам блока обнаружения и коррекции искажений; при этом второй выход переключателя подключен к первому входу блока комплексификации куда поступает из канала связи канала связи вещественный вычет h, ко второму и третьему входам блока комплексификации подключены первый и второй выходы блока формирования простых чисел (р, q), ко входу которого подключен второй выход блока хранения управляющих параметров (N), третий выход которого подключен к восьмому входу блока обнаружения и коррекции искажений; четвертый выходы блока хранения управляющих параметров (N) подключены к входам блоков формирования оснований

подключены к четвертому и пятому входам блока обнаружения и коррекции искажений; при этом второй выход переключателя подключен к первому входу блока комплексификации куда поступает из канала связи канала связи вещественный вычет h, ко второму и третьему входам блока комплексификации подключены первый и второй выходы блока формирования простых чисел (р, q), ко входу которого подключен второй выход блока хранения управляющих параметров (N), третий выход которого подключен к восьмому входу блока обнаружения и коррекции искажений; четвертый выходы блока хранения управляющих параметров (N) подключены к входам блоков формирования оснований  ; при этом первый и второй выходы блока комплексификации подключены к третьим входам блоков вычисления синдрома ошибки δ(1), δ(2) выходы которых подключены к шестому и седьмому входам блока обнаружения и коррекции искажений, второй выход которого подключен к входу блока формирования запроса с выхода которого направляется запрос на повторную передачу искаженных блоков шифртекста; выход буфера вывода шифртекста подключен к к первому входу блока расшифрования, ко второму входу которого подключен процессор ключей шифрования (κd,i), на вход которого поступает секретный ключ (

; при этом первый и второй выходы блока комплексификации подключены к третьим входам блоков вычисления синдрома ошибки δ(1), δ(2) выходы которых подключены к шестому и седьмому входам блока обнаружения и коррекции искажений, второй выход которого подключен к входу блока формирования запроса с выхода которого направляется запрос на повторную передачу искаженных блоков шифртекста; выход буфера вывода шифртекста подключен к к первому входу блока расшифрования, ко второму входу которого подключен процессор ключей шифрования (κd,i), на вход которого поступает секретный ключ ( )), при этом выход блока расшифрования подключен к первому входу буфера вывода блоков открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, выход которого является выходом криптокодового преобразователя информации, с выхода которого поступает открытый текст; счетчик блоков текста отслеживает номер обрабатываемого блока.

)), при этом выход блока расшифрования подключен к первому входу буфера вывода блоков открытого текста, ко второму входу которого подключен выход блока (таблицы) кодовых символов, выход которого является выходом криптокодового преобразователя информации, с выхода которого поступает открытый текст; счетчик блоков текста отслеживает номер обрабатываемого блока.

в) Причинно-следственная связь между признаками и техническим результатом

Благодаря введению в известный объект совокупности существенных отличительных признаков, способ и устройство обеспечения помехоустойчивой обработки данных на основе криптокодовых конструкций в комплексной плоскости позволяет:

- обеспечить доведение информации по каналам связи с ненулевой пропускной способностью;

- обеспечить гарантированную стойкость системы криптографической защиты информации;

- обеспечить обнаружение и локализацию искаженных, имитируемых злоумышленником данных, с последующим запросом на передачу искаженного фрагмента данных;

- обеспечить достоверное восстановление искаженных, имитируемых злоумышленником данных.

Доказательства соответствия заявленного изобретения условиям патептпоспособности «новизна» и «изобретательский уровень»

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующие совокупности признаков, тождественных всем признакам заявленного технического технического решения, отсутствуют, что указывает на соответствие заявленного способа условию патентноепособности « новизна ».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта показали, что они не следуют явно из уровня техники. Из уровня техники также не выявлена известность отличительных существенных признаков, обуславливающих тот же технический результат, который достигнут в заявленном способе. Следовательно, заявленное изобретение соответствует уровню патентноспособности «изобретательский уровень».

Краткое описание чертежей

Заявленный способ и устройство поясняется чертежами, на которых показано:

- фиг. 1 изображена схема, поясняющая сущность работы способа-прототипа (передающая часть);

- фиг. 2 изображена схема, поясняющая сущность работы способа-прототипа (принимающая часть);

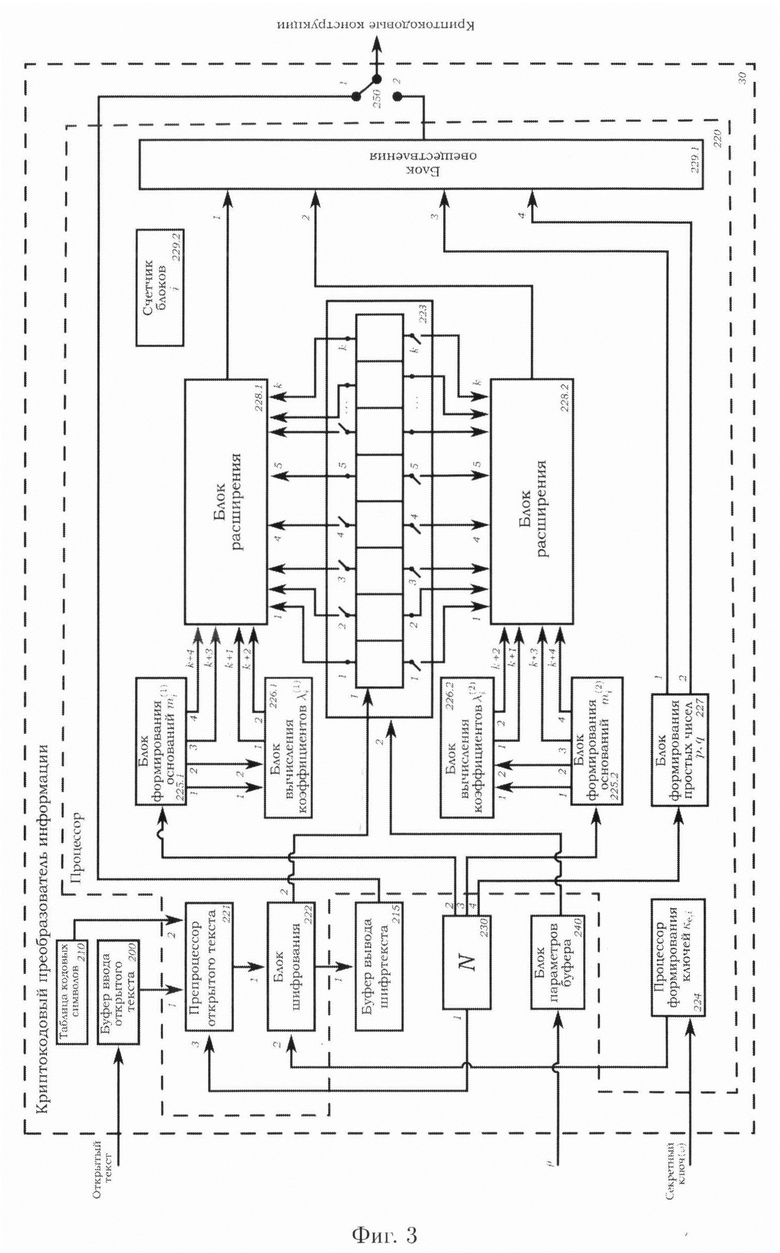

- фиг. 3 изображена схема устройства обеспечения помехоустойчивой обработки данных (передающая часть);

- фиг. 4 изображена схема устройства обеспечения помехоустойчивой обработки данных (принимающая часть);

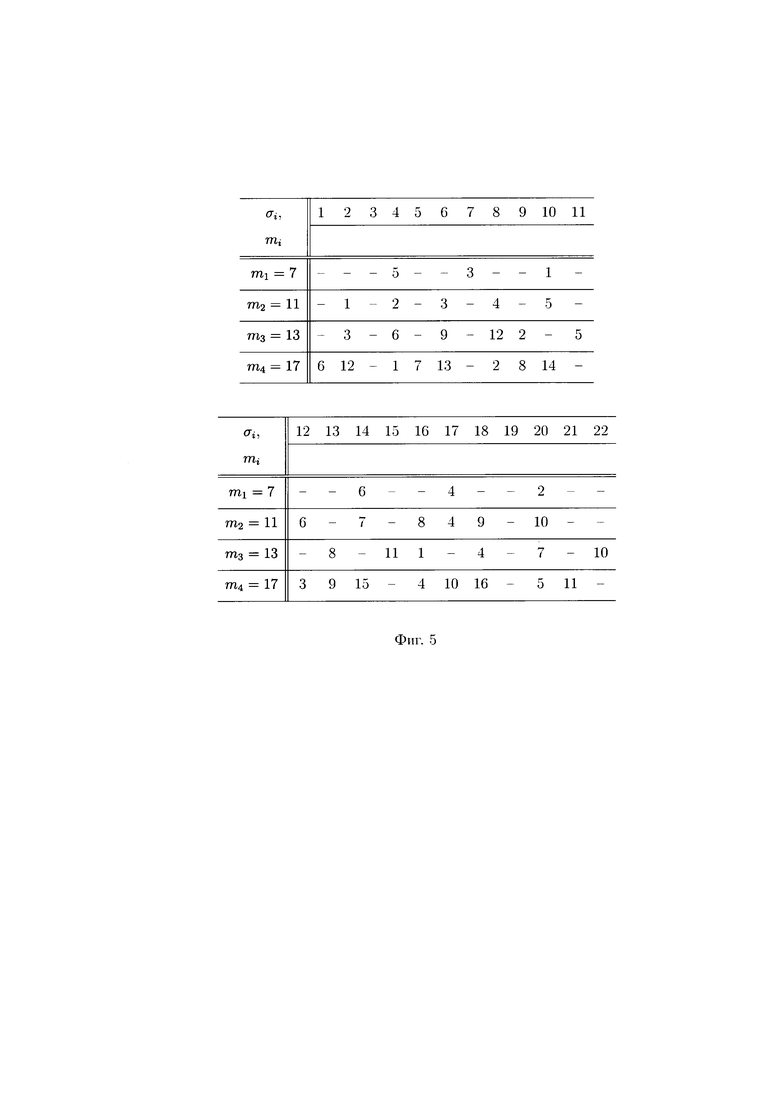

- фиг. 5 изображена таблица допустимых ошибок для системы оснований

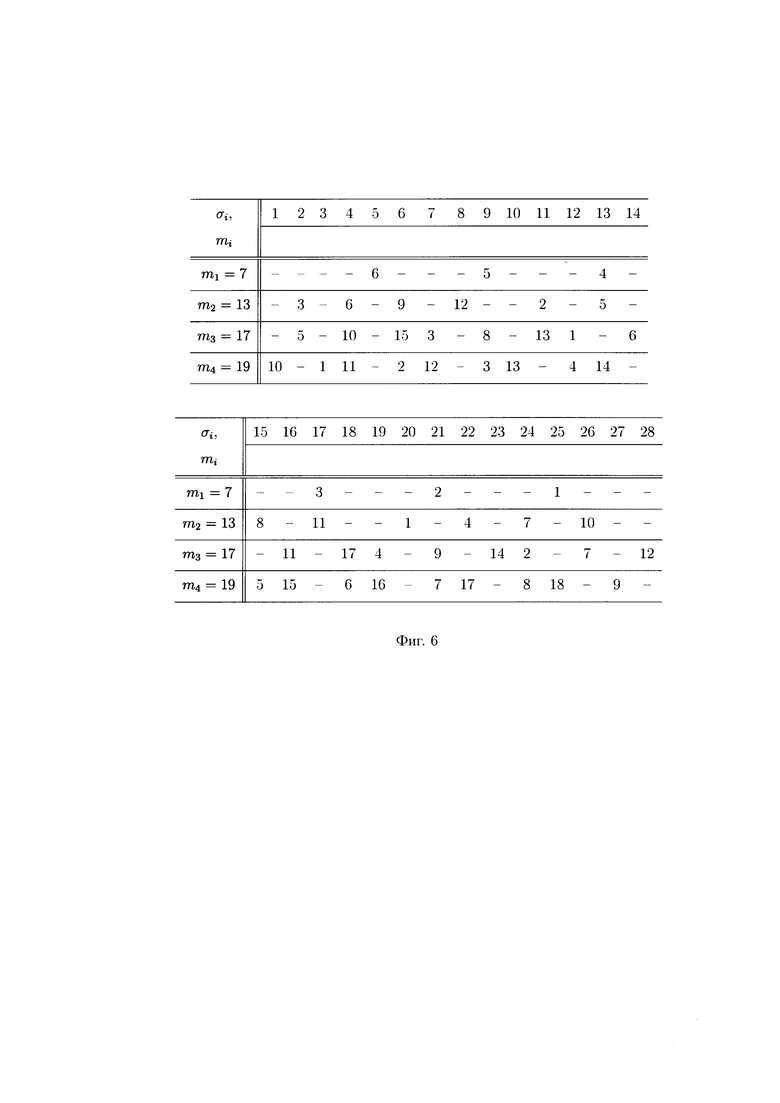

- фиг. 6 изображена таблица допустимых ошибок для системы оснований

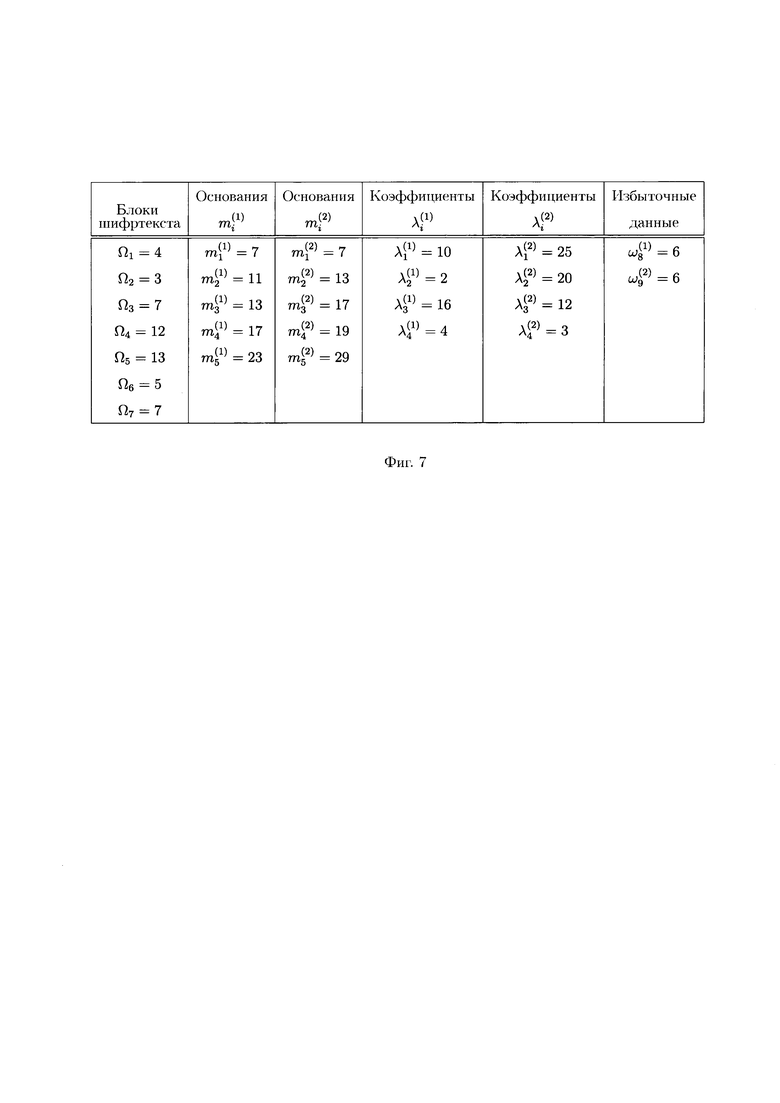

- фиг. 7 изображена таблица преобразований.

Осуществление изобретения

Для большей ясности описание изобретения, позволяющее специалисту произвести осуществление предложенного изобретения и показывающее влияние признаков, приведенных в формуле изобретения, на указанный выше технический результат, будем производить следующим образом: сначала раскроем структуру устройства, а затем опишем реализацию способа в рамках предложенного устройства.

Устройство обеспечения помехоустойчивой обработки данных на основе криптокодовых конструкций в комплексной плоскости содержит на передающей стороне (фиг. 3) криптокодовый преобразователь информации 30, состоящий из буфера 200 ввода открытого текста, блока (таблицы) 210 кодовых символов, буфера вывода шифртекста 215, блока хранения (накопителя) 230 управляющих параметров, блока 240 параметров буфера, процессора 220, реализующего функции, представленные в виде функциональных блоков: препроцессора 221 открытого текста, блока 222 шифрования, промежуточный буфер 223, процессора 224 ключей шифрования, блока 225.1 формирования оснований, блока 226.1 вычисления коэффициентов, блока 226.2 вычисления коэффициентов, блока 225.2 формирования оснований, блока 227 формирования простых чисел, блока 228.1 расширения, блока 228.2 расширения, блока 229.1 овеществления, счетчика 229.2 блоков текста; переключателя 250, и на приемной стороне устройство содержит (фиг. 4) криптокодовый преобразователь информации 50, состоящий из переключателя 300, блока 310 параметров буфера, блока хранения (накопителя) 315 управляющих параметров, процессора 320, реализующего функции, представленные в виде функциональных блоков: блока 321 формирования простых чисел, блока 322 комплексификации, блока 323.1 формирования оснований, блока 324.1 вычисления коэффициентов, блока 324.2 вычисления коэффициентов, блока 323.2 формирования оснований, блока 325.1 расширения, блока 325.2 расширения, промежуточный буфер 326, блока 327.1 вычисления синдрома ошибки, блока 327.2 вычисления синдрома ошибки, блока 328 обнаружения и коррекции искажений, буфера вывода 329 шифртекста, блока 329.1 расшифрования, буфера 329.2 вывода открытого текста, блока 329.3 формирования запроса, счетчика 329.4 блоков текста; блока (таблицы) 330 кодовых символов, процессора 343 ключей шифрования.

Устройство работает следующим образом:

Подлежащая передаче информация, представленная в виде потока символов поступает в криптокодовый преобразователь информации 30, буферизируется буфером 200 ввода открытого текста перед его предварительной обработкой препроцессором 221 открытого текста. Препроцессор 221 открытого текста анализирует входной поток символов открытого текста, разбивает его на блоки фиксированной длины в соответствии с параметром (N) накопителя 230 управляющих параметров и осуществляет преобразование символов открытого текста в числовые значения, поступающие с блока (таблицы) 210 кодовых символов. Сформированные блоки открытого текста поступают в блок 222 шифрования, в котором осуществляется процедура блочного шифрования с нелинейными биективными преобразованиями с помощью итерационных ключей зашифрования (κe,i), выработанных процессором 224 ключей шифрования на основании введенного секретного ключа ( ). Сформированные блоки шифртекста поступают в буфер 215 вывода шифртекста и в промежуточный буфер 223, в который поступают управляющие параметры из блока 240 параметров буфера, определяющие какие блоки шифртекста промежуточного буфера 223 поступают в блоки 228.1 и 228.2 расширения. В блоки 228.1 и 228.2 расширения для формирования 1-го и 2-го избыточных блоков данных из блоков 226.1 и 226.2 вычисления коэффициентов поступают необходимые параметры (коэффициенты

). Сформированные блоки шифртекста поступают в буфер 215 вывода шифртекста и в промежуточный буфер 223, в который поступают управляющие параметры из блока 240 параметров буфера, определяющие какие блоки шифртекста промежуточного буфера 223 поступают в блоки 228.1 и 228.2 расширения. В блоки 228.1 и 228.2 расширения для формирования 1-го и 2-го избыточных блоков данных из блоков 226.1 и 226.2 вычисления коэффициентов поступают необходимые параметры (коэффициенты  ) соответственно. Также в блоки 228.1 и 228.2 расширения и в блоки 226.1 и 226.2 вычисления коэффициентов поступают модули (основания

) соответственно. Также в блоки 228.1 и 228.2 расширения и в блоки 226.1 и 226.2 вычисления коэффициентов поступают модули (основания  ) для вычисления коэффициентов

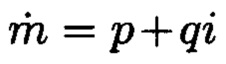

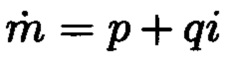

) для вычисления коэффициентов  , и последующего формирования избыточных блоков данных, выработанные блоками 225.1 и 225.2 формирования оснований в соответствии с параметром (N) накопителя 230 управляющих параметров. Выработанные блоками 228.1 и 228.2 расширения избыточные блоки данных поступают в блок 229.1 овеществления. Также в блок 229.1 овеществления из блока 227 формирования простых чисел поступают простые числа (р, q). Далее в блоке 229.1 овеществления из 1-го избыточного блока данных, выработанного блоком 228.1 расширения и 2-го избыточного блока данных, выработанного блоком 228.2 расширения формируется псевдокомплексное число и осуществляется вычисление вещественного вычета по заданному (сформированному) модулю p+qi. При этом сформированные блоки шифртекста с выхода буфера 215 вывода шифртекста (информационные элементы) направляются на первый выход переключателя 250, на второй выход которого поступает вычисленный в блоке 229-1 овеществления вещественный вычет (избыточный элемент), полученная последовательность блоков шифртекста и вещественного вычета образует таким образом криптокодовые конструкции - помехоустойчивую последовательность шифрованного текста.

, и последующего формирования избыточных блоков данных, выработанные блоками 225.1 и 225.2 формирования оснований в соответствии с параметром (N) накопителя 230 управляющих параметров. Выработанные блоками 228.1 и 228.2 расширения избыточные блоки данных поступают в блок 229.1 овеществления. Также в блок 229.1 овеществления из блока 227 формирования простых чисел поступают простые числа (р, q). Далее в блоке 229.1 овеществления из 1-го избыточного блока данных, выработанного блоком 228.1 расширения и 2-го избыточного блока данных, выработанного блоком 228.2 расширения формируется псевдокомплексное число и осуществляется вычисление вещественного вычета по заданному (сформированному) модулю p+qi. При этом сформированные блоки шифртекста с выхода буфера 215 вывода шифртекста (информационные элементы) направляются на первый выход переключателя 250, на второй выход которого поступает вычисленный в блоке 229-1 овеществления вещественный вычет (избыточный элемент), полученная последовательность блоков шифртекста и вещественного вычета образует таким образом криптокодовые конструкции - помехоустойчивую последовательность шифрованного текста.

При этом счетчик блоков 229.2 текста отслеживает обрабатываемый блок текста для согласования с управляющими параметрами процедур зашифрования.

На приемной стороне принятые криптокодовые конструкции (помехоустойчивая последовательность шифрованного текста) поступают в криптокодовый преобразователь информации 50, на вход переключателя 300, с первого выхода которого принятая последовательность шифртекста поступает в блок 328 обнаружения и коррекции искажений и в промежуточный буфер 326. В блоках 328 обнаружения и коррекции искажений и в промежуточном буфере 326 принятая последователь шифрованного текста разбивается на блоки фиксированной длины в соответствии с параметром (N) накопителя 315 управляющих параметров. В промежуточный буфер 326 поступают управляющие параметры из блока 310 параметров буфера, определяющие какие блоки шифртекста промежуточного буфера 326 поступают в блоки 325.1 и 325.2 расширения. Для формирования избыточных блоков данных в блоки 325.1 и 325.2 расширения от принятой последовательности блоков шифртекста из блоков 324.1 и 324.2 вычисления коэффициентов поступают вычисленные параметры (коэффициенты  ) соответственно. Далее блоками 323.1 и 323.2 формирования оснований в соответствии с параметром (N) накопителя 315 управляющих параметров формируются модули (основания

) соответственно. Далее блоками 323.1 и 323.2 формирования оснований в соответствии с параметром (N) накопителя 315 управляющих параметров формируются модули (основания  ), которые направляются в блоки 324.1 и 324.2 вычисления коэффициентов для вычисления коэффициентов

), которые направляются в блоки 324.1 и 324.2 вычисления коэффициентов для вычисления коэффициентов  , а также в блоки 325.1 и 325.2 расширения для формирования избыточных блоков данных. Выработанные блоками 325.1 и 325.2 расширения избыточные блоки данных поступают в блоки 327.1 и 327.2 вычисления синдрома ошибки. Теперь со второго выхода переключателя 300 принятый вещественный вычет поступает в блок 322 комплексификации, в котором осуществляется преобразование вещественного вычета по заданному модулю р+qi в псевдокомплексное число (1-ый избыточный блок данных и 2-ой избыточный блок данных), куда также поступают простые числа (р, q), выработанные блоком 321 формирования простых чисел в соответствии с параметром (N) накопителя 315 управляющих параметров (количество и значения выработанных чисел соответствуют параметрам передающей стороны). Сформированные 1-ый и 2-ой избыточные блоки данных (избыточные элементы) поступают в блоки 327.1 и 327.2 вычисления синдрома ошибки, сюда же для вычисления синдрома ошибки поступают модули (основания

, а также в блоки 325.1 и 325.2 расширения для формирования избыточных блоков данных. Выработанные блоками 325.1 и 325.2 расширения избыточные блоки данных поступают в блоки 327.1 и 327.2 вычисления синдрома ошибки. Теперь со второго выхода переключателя 300 принятый вещественный вычет поступает в блок 322 комплексификации, в котором осуществляется преобразование вещественного вычета по заданному модулю р+qi в псевдокомплексное число (1-ый избыточный блок данных и 2-ой избыточный блок данных), куда также поступают простые числа (р, q), выработанные блоком 321 формирования простых чисел в соответствии с параметром (N) накопителя 315 управляющих параметров (количество и значения выработанных чисел соответствуют параметрам передающей стороны). Сформированные 1-ый и 2-ой избыточные блоки данных (избыточные элементы) поступают в блоки 327.1 и 327.2 вычисления синдрома ошибки, сюда же для вычисления синдрома ошибки поступают модули (основания  ), выработанные блоками 323.1 и 323.2 формирования оснований. Полученные в блоках 327.1 и 327.2 вычисления синдрома ошибки значения синдромов поступают в блок 328 обнаружения и коррекции искажений, где обеспечивают обнаружение и локализацию ошибок в принятой последовательности блоков шифрованного текста. Также в блок 328 обнаружения и коррекции искажений поступают модули (основания

), выработанные блоками 323.1 и 323.2 формирования оснований. Полученные в блоках 327.1 и 327.2 вычисления синдрома ошибки значения синдромов поступают в блок 328 обнаружения и коррекции искажений, где обеспечивают обнаружение и локализацию ошибок в принятой последовательности блоков шифрованного текста. Также в блок 328 обнаружения и коррекции искажений поступают модули (основания  ) выработанные блоками 323.1 и 323.2 формирования оснований, на основе которых осуществляется построение таблиц допустимых ошибок. Таблицы ошибок содержат значение ошибки в цифре соответствующего модуля (основания

) выработанные блоками 323.1 и 323.2 формирования оснований, на основе которых осуществляется построение таблиц допустимых ошибок. Таблицы ошибок содержат значение ошибки в цифре соответствующего модуля (основания  ). Проверенная и восстановленная последовательность блоков шифртекста из блока 328 обнаружения и коррекции искажений поступает в буфера 329 вывода шифртекста. Далее последовательность блоков шифртекста поступает на вход блока 329.1 расшифрования, в котором выполняется процедура обратного преобразования последовательности блоков шифртекста в последовательность блоков открытого текста в соответствии с заданным алгоритмом шифрования и с помощью итерационных ключей расшифрования (κd,i). При этом итерационные ключи расшифрования вырабатываются процессором 343 ключей шифрования на основании введенного секретного ключа (

). Проверенная и восстановленная последовательность блоков шифртекста из блока 328 обнаружения и коррекции искажений поступает в буфера 329 вывода шифртекста. Далее последовательность блоков шифртекста поступает на вход блока 329.1 расшифрования, в котором выполняется процедура обратного преобразования последовательности блоков шифртекста в последовательность блоков открытого текста в соответствии с заданным алгоритмом шифрования и с помощью итерационных ключей расшифрования (κd,i). При этом итерационные ключи расшифрования вырабатываются процессором 343 ключей шифрования на основании введенного секретного ключа ( ). Расшифрованная последовательность блоков открытого текста поступает в буфер 329.2 вывода открытого текста, в котором осуществляется преобразование числовых значений в символы открытого текста, поступающие с блока (таблицы) 330 кодовых символов. При этом счетчик блоков 329.4 текста отслеживает обрабатываемый блок текста для согласования с управляющими параметрами процедур расшифрования.

). Расшифрованная последовательность блоков открытого текста поступает в буфер 329.2 вывода открытого текста, в котором осуществляется преобразование числовых значений в символы открытого текста, поступающие с блока (таблицы) 330 кодовых символов. При этом счетчик блоков 329.4 текста отслеживает обрабатываемый блок текста для согласования с управляющими параметрами процедур расшифрования.

В случае превышения корректирующих способностей принятых криптокодовых конструкций блок 328 обнаружения и коррекции направляет сигнал в блок 329.3 формирования запроса на повторную передачу искаженных блоков данных и локализованную посредством синдромов ошибок. Также блок 329.3 формирования запроса направляет управляющий сигнал в буфер 329 вывода шифртекста о превышении корректирующих способностей криптокодовых конструкций, блокирующий выход буфера 329 вывода шифртекста.

Кроме того, настоящее изобретение предлагает способ обеспечения помехоустойчивой обработки данных на основе криптокодовых конструкций в комплексной плоскости.

В одном варианте исполнения способ (устройство) обеспечения помехоустойчивой обработки данных на основе криптокодовых конструкций может быть реализован(о) в соответствии с положениями слабо-арифметических кодов системы остаточных классов (слабо-арифметических модулярных кодов, САМK).

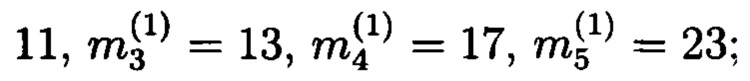

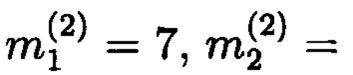

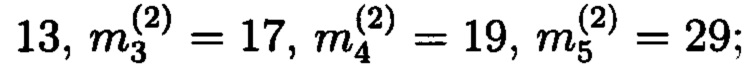

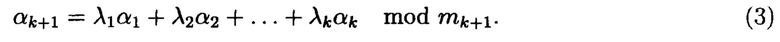

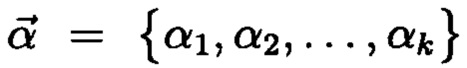

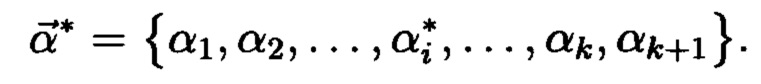

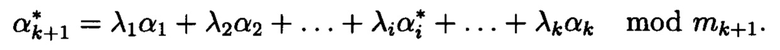

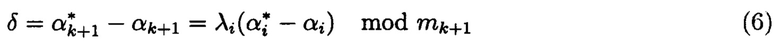

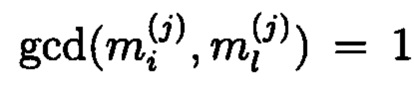

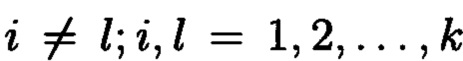

Математический аппарат САМK основывается положениях, описанных в [И.Я. Акушский, И.Т. Пак Вопросы помехоустойчивого кодирования в непозиционном коде // Вопросы кибернетики. 1977. №28. с. 36-56]. Пусть m1, m2, …, mk ∈ R взаимно простые числа, упорядоченные по величине, т.е. m1 < m2 < … < mk. Рассмотрим систему с основаниями

m1 < m2 < … < mk

и введем дополнительное контрольное основание

Порядок вычисления избыточной цифры αk+1 по контрольному основанию mk+1 определяется следующим образом:

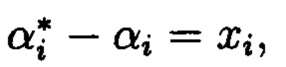

Процедура подбора коэффициентов λi (i = 1, 2, …, k) линейной формы реализуется в совокупности с процедурой подбора оснований mi. Для этого часть оснований mi и λi может быть выбрана так, что

а другая ее часть  и коэффициенты

и коэффициенты  с учетом

с учетом

Пусть в последовательности элементов  произошла однократная ошибка (ошибка в цифре по одному основанию) и вместо

произошла однократная ошибка (ошибка в цифре по одному основанию) и вместо  получим

получим

Далее вычисляется избыточный элемент CAMK

Вычислим

или, переопределив

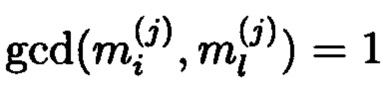

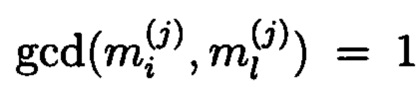

Для того, чтобы любая ошибка по основанию mi была обнаружена, требуется чтобы указанное выше сравнение имело единственное решение. Иными словами, каждому значению δ выражения (6) должно соответствовать определенное значение ошибки xi и наоборот, каждому значению xi - определенное значение δ. Поскольку в CAMK на систему оснований т» наложено условие gcd(mi, mj) = 1 (i = 1, 2, …, k), то для единственности решения сравнения (7), требуется чтобы λi было взаимно просто с mk+1. Отсюда в соответствии с [И.Я. Акушский, И.Т. Пак Вопросы помехоустойчивого кодирования в непозиционном коде // Вопросы кибернетики. 1977. №28. с. 36-56], для того, чтобы избыточный элемент кода CAMK позволял обнаружить любую одиночную ошибку необходимым и достаточным условием является требование gcd(λi, mk+1) = 1 (i = 1, 2, …, k).

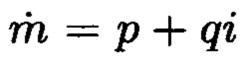

Второй этап математических преобразований изобретения базируется на фундаментальной теореме Гаусса [И.Я. Акушский, Д.И. Юдицкий Машинная арифметика в остаточных классах. М., «Советское радио», 1968. 440 с.; В.М. Амербаев, И.Т. Пак Параллельные вычисления в комплексной плоскости. Алма-Ата.: Изд-во. «Наука». 1984. 183 с.; В.Г. Лабунец Алгебраическая теория сигналов и систем (цифровая обработка сигналов). Красноярск: Изд-во Красноярского университета, 1984. 244 с.].

Теорема Гаусса. По заданному комплексному модулю  , норма которого равна K=р2+q2 и для которого р и q являются взаимно простыми числами, каждое комплексное число сравнимо с одним и только одним вычетом из ряда

, норма которого равна K=р2+q2 и для которого р и q являются взаимно простыми числами, каждое комплексное число сравнимо с одним и только одним вычетом из ряда

0, 1, 2, 3, …, K-1.

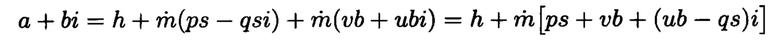

Доказательство. Из теории чисел известно, что для двух взаимно простых чисел р и q можно найти такие два целых числа u и v, что

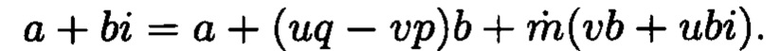

Составим тождество

и пусть дано комплексное число а+bi. которое перепишем заменив i из (9)

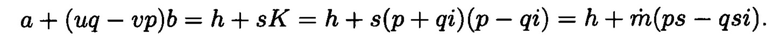

Обозначим через h наименьший положительный вещественный вычет числа a+(uq-vp)b по модулю K и положим, что

Тогда будет выполняться равенство

или в форме сравнения

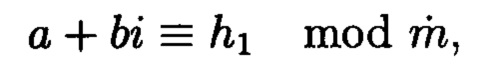

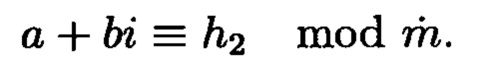

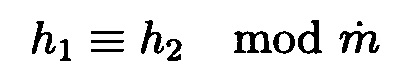

Таким образом, доказано, что а+bi сравнимо с одним из чисел 0, 1, 2, 3, …, K-1 по модулю  . Причем это число единственное. Предположим, что имеют место два сравнения

. Причем это число единственное. Предположим, что имеют место два сравнения

По свойству сравнений числа h1 и h2 сравнимы между собой по модулю  , т.е.

, т.е.

или

Из (11) следует выполнимость равенства

(hl-h2)(p-qi)=K(e+fi),

эквивалентного двум вещественным равенствам:

Умножив первое равенство (12) на u и второе на v и сложив их, получим

(h1-h2)(up+vq)=K(eu-fv),

откуда, принимая во внимание (8), следует

h1-h2=K(eu-fv)

или

Поскольку по предположению h1<K и h2<K, то (14) возможно только в случае h1=h2.

Таким образом, исключается существование двух чисел h1 и h2, меньших K, которые были бы сравнимы с а+bi по модулю  , а имеется только одно такое число, которое определяется из сравнения

, а имеется только одно такое число, которое определяется из сравнения

а+(uq-vp)b≡h mod K

или

а+bρ≡h mod K.

Указанная теорема устанавливает изоморфизм между комплексными числами и их вещественными вы чета ми.

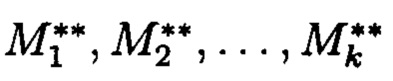

Сгенерированное отправителем сообщение М подлежащее зашифрованию, поступает на вход криптокодового преобразователя информации 30, буферизируется в виде символов в буфере 200 ввода открытого текста перед его предварительной обработкой препроцессором 221 открытого текста. Препроцессор 221 открытого текста анализирует входной поток символов открытого текста, осуществляет преобразование символов открытого текста в числовые значения, поступающие с блока (таблицы) 210 кодовых символов и в соответствии с параметром (N) блока хранения 230 управляющих параметров разбивает его на блоки фиксированной длины М={М1||М2|| … ||Mk} в зависимости от алгоритма шифрования (например, ГОСТ 34.12-2015 с блоками 64, 128 бит соответственно). С целью обеспечения необходимого уровня конфиденциальности информации сформированная последовательность блоков открытого текста M1, M2, …, Mk поступает в блок 222 шифрования. Для получения последовательности блоков шифртекста Ω1, Ω2, …, Ωk потребуется выполнение k операций зашифрования. Соответственно отображение (1) может быть представлено в виде:

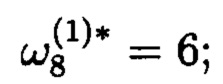

где κе,i _ итерационные ключи зашифрования (i=1, 2, …, k), выработанные процессором 224 формирования ключей на передающей стороне на основании введенного секретного ключа ( ). Далее последовательность блоков шифртекста Ωi (i=1, 2, …, k) поступает в буфер 215 вывода шифртекста и параллельно поступает в промежуточный буфер 223. Поступившая в промежуточный буфер 223 последовательность блоков шифртекста Ωi (i=1, 2, …, k) буферизируется. В каждый момент времени t с выходов промежуточного буфера 223 через переключатели блоки шифртекста Ωi (i=1, 2, …, k) поступают в блоки 228.1 и 228.2 расширения. Переключатели промежуточного буфера 223 соединяют его выходы с входами блоков 228.1 и 228.2 расширения. Порядок работы переключателей промежуточного буфера 223, а также удаление блоков шифртекста Ωi (i=1, 2, …, k) из промежуточного буфера 223 реализуется посредством управляющих параметров блока 240 параметров регистра. Принятая блоками 228.1 и 228.2 расширения последовательность блоков шифртекста Ωi (i=1, 2, …, k) представляется в виде наименьших неотрицательных вычетов по основаниям

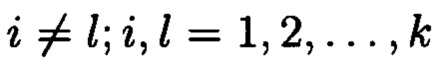

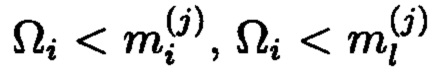

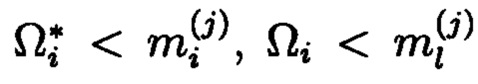

). Далее последовательность блоков шифртекста Ωi (i=1, 2, …, k) поступает в буфер 215 вывода шифртекста и параллельно поступает в промежуточный буфер 223. Поступившая в промежуточный буфер 223 последовательность блоков шифртекста Ωi (i=1, 2, …, k) буферизируется. В каждый момент времени t с выходов промежуточного буфера 223 через переключатели блоки шифртекста Ωi (i=1, 2, …, k) поступают в блоки 228.1 и 228.2 расширения. Переключатели промежуточного буфера 223 соединяют его выходы с входами блоков 228.1 и 228.2 расширения. Порядок работы переключателей промежуточного буфера 223, а также удаление блоков шифртекста Ωi (i=1, 2, …, k) из промежуточного буфера 223 реализуется посредством управляющих параметров блока 240 параметров регистра. Принятая блоками 228.1 и 228.2 расширения последовательность блоков шифртекста Ωi (i=1, 2, …, k) представляется в виде наименьших неотрицательных вычетов по основаниям  (i=1, 2, …, k; j=1, 2), сформированным блоками 225.1 и 225.2 формирования оснований, таким, что

(i=1, 2, …, k; j=1, 2), сформированным блоками 225.1 и 225.2 формирования оснований, таким, что  ,

,  . Причем

. Причем  . Основания

. Основания  (i=1, 2, …, k; j=1, 2), полученные блоками 225.1 и 225.2 формирования оснований поступают в блоки 226.1 и 226.2 вычисления коэффициентов, выработанные коэффициенты

(i=1, 2, …, k; j=1, 2), полученные блоками 225.1 и 225.2 формирования оснований поступают в блоки 226.1 и 226.2 вычисления коэффициентов, выработанные коэффициенты  направляются в блоки 228.1 и 228.2 расширения. Далее блоками 225.1 и 225.2 формирования оснований осуществляется вычисление избыточных оснований

направляются в блоки 228.1 и 228.2 расширения. Далее блоками 225.1 и 225.2 формирования оснований осуществляется вычисление избыточных оснований  , удовлетворяющих условию (2) таких, что

, удовлетворяющих условию (2) таких, что  , для

, для  с их последующим направлением в блоки 228.1 и 228.2 расширения. В блоках 228.1 и 228.2 расширения в соответствии с выражением (3) вырабатываются 1-ый и 2-ой избыточные блоки данных (вычеты), которые обозначим как

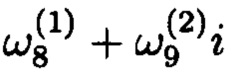

с их последующим направлением в блоки 228.1 и 228.2 расширения. В блоках 228.1 и 228.2 расширения в соответствии с выражением (3) вырабатываются 1-ый и 2-ой избыточные блоки данных (вычеты), которые обозначим как  . Сформированные в блоках 228.1 и 228.2 расширения 1-ый и 2-ой избыточные блоки данных (вычеты) поступают в блок 229.1 овеществления, где формируется псевдокомплексное число

. Сформированные в блоках 228.1 и 228.2 расширения 1-ый и 2-ой избыточные блоки данных (вычеты) поступают в блок 229.1 овеществления, где формируется псевдокомплексное число  . Так же в блок 229.1 овеществления дополнительно поступают простые числа (р, а) выработанные блоком 227 формирования простых чисел для формирования комплексного модуля

. Так же в блок 229.1 овеществления дополнительно поступают простые числа (р, а) выработанные блоком 227 формирования простых чисел для формирования комплексного модуля  и вычисления нормы K. После формирования комплексного модуля

и вычисления нормы K. После формирования комплексного модуля  псевдокомплексное число

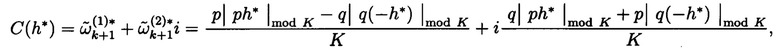

псевдокомплексное число  преобразуется в целое вещественное число h, для этого сравнение (10) представляется в следующем виде:

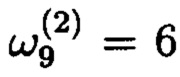

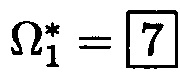

преобразуется в целое вещественное число h, для этого сравнение (10) представляется в следующем виде: