Изобретение относится к вычислительной технике, а именно к устройствам преобразования кода с заданием определенной циклограммы выдачи последовательных кодов.

Известны устройства для преобразования парадлельного кода в последовательный . содержащие генератор импульсов, соединенный со входом счетчика, подключенного к дешифратору, часть выходов которого соединена с первыми входами логических элементов И, вторые входы которых подключены к регистрам, а выходы - к логическому элементу ИЛИ, блок управления, входь которого подключен к дешифратору.

Известное устройство выдает информацию в последовательном коде с интервалами между словами, которые не могут быть меньше времени записи слова в регистр. В тех случаях, когда информация в последовательном коде записывается в накопители, предназначенные для работы в других вычислительных комплексах, где к интервалам между словами предъявляются жесткие требования, существующие устройства преобразования не пригодны для записи.

Цель изобретения - обеспечение возможности регулирования интервала между словами в широких (практически неограниченных) пределах.

Предлагаемое устройство отличается тем, что выход дешифратора соединенный со входом блока управления, подключен ко входу триггера со счетным входом, выходы которого подключены к третьим входам упомянутых логических элементов И и к первым входам двух дополнительных логических элементов И, вторые входы которых соединены через узел задержки с одним из выходов блока управления, выходы - с управляюидами входами регисттров, а другой выход блока управления подключен к сбросовому входу счетчика.

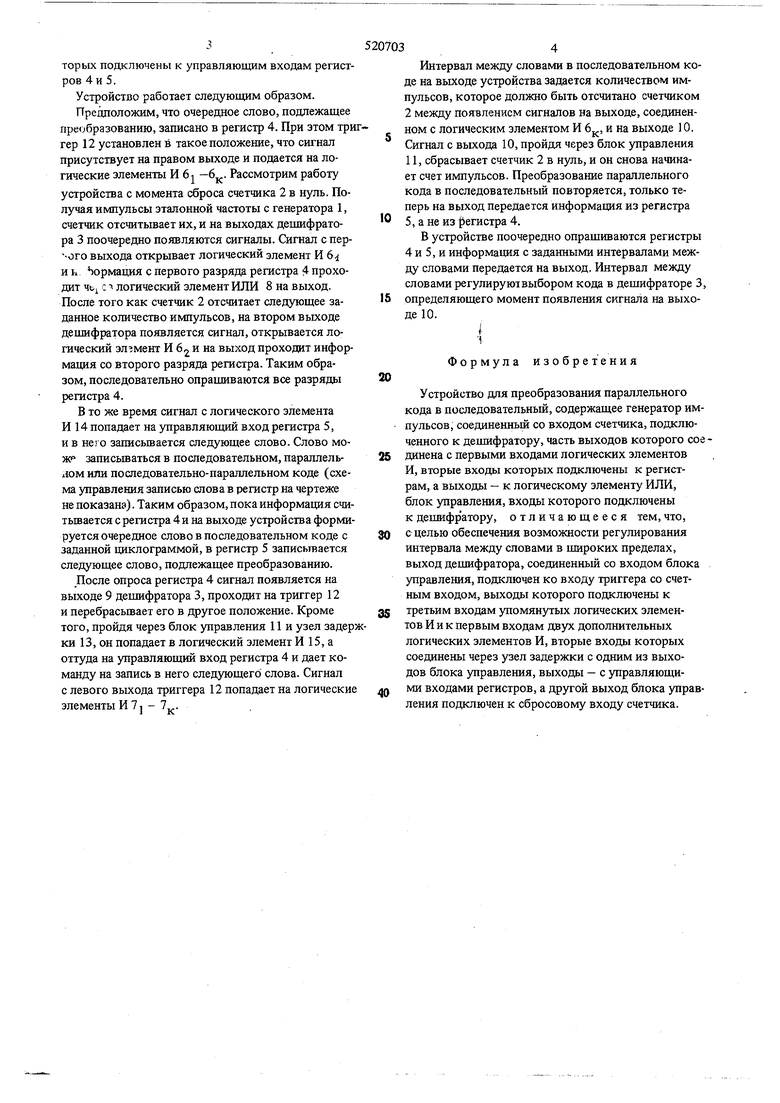

На чертеже изображено данное устройство.

Генератор импульсов 1 соединен со счетчиком 2, выходы которого подключены ко входам дешифратора 3. Часть выходов дешифратора, соответствующая количеству разрядов в регистрах 4 и 5, подключена ко входам логических элементов И 61 -И 6 и И 7 J- И 7j. Выходы всех логических элементов подключены ко входам логического элемента ИЛИ 8, выходы 9 и 10 дешифратора 3 подключены ко входам блока управления 11, а выход 9 связан также со входом триггера со счетным входом 12. Выход блок, управления через узел задержки 13 подключен ко входам логических элементов И 14 и 15, выходы которых подключены к управляющим входам регистров 4 и 5.

Устройство работает следующим образом.

Предположим, что очередное слово, подлежащее пре(бразованию, записано в регистр 4. При зтом тригер 12 установлен в такое положение, что сигнал присутствует на правом выходе и подается на логические элементы И 6 -6j. Рассмотрим работу

устройства с момента сброса счетчика 2 в нуль. Получая импульсы эталонной частоты с генератора 1, счетчик отсчитывает их, и на выходах дешифратора 3 поочередно появляются сигналы. Сигнал с пер-ого выхода открывает логический элемент И 6 и h Ьормация с первого разряда регистра 4 проходит чь с 1 логический элемент ИЛИ 8 на выход. После того как счетчик 2 отсчитает следующее заданное количество импульсов, на втором выходе дешифратора появляется сигнал, открывается логический элемент И 6 и на выход проходит информация со второго разряда регистра. Таким образом, последовательно опраишваются все разряды регистра 4.

В то же время сигнал с логического элемента И 14 попадает на заправляющий вход регистра 5, и в него записьтается следующее слово. Слово мож записьшаться в последовательном, параллельлом или последовательно-параллельном коде (схема управления записью слова в регистр на чертеже не показана). Таким образом, пока информация считьшается с регистра 4 и на выходе устройства формируется очередное слово в последовательном коде с заданной циклограммой, в регистр 5 записывается следующее слово, подлежащее преобразованию.

После опроса регистра 4 сигнал появляется на выходе 9 дешифратора 3, проходит на триггер 12 и перебрасьтает его в другое положение. Кроме того, пройдя через блок управления 11 и узел задер ки 13, он попадает в логический элемент И 15, а оттуда на управляющий вход регистра 4 и дает команду на запись в него следующего слова. Сигнал с левого выхода триггера 12 попадает на логические элементы И 7 J - 7j.

207034

Интервал между словами в последовательном коде на выходе устройства задается количеством импульсов, которое должно быть отсчитано счетчиком 2 между появлением сигналов на выходе, соединенном с логическим элементом И 6j, и на выходе 10. Сигнал с выхода 10, пройдя через блок управления 11, сбрасывает счетчик 2 в нуль, и он снова начинает счет импульсов. Преобразование параллельного кода в последовательный повторяется, только теперь на выход Передается информация из регистра 5, а не из {Регистра 4.

В устройстве поочередно опрашиваются регистры 4 и 5, и информация с заданными интервалами между словами передается на выход. Интервал между словами регулируют выбором кода в дещифраторе 3, 15 определяющего момент появления сигнала на выходе 10.

I

Формула изобретения

Устройство для преобразования параллельного кода в последовательный, содержащее генератор импульсов, соединенньш со входом счетчика, подключенного к дешифратору, часть выходов которого сое

динена с первыми входами логических элементов И, вторые входы которых подключены к регистрам, а выходы - к логическому элементу ИЛИ, блок управления, входы которого подключены к дешифратору, отличающееся тем, что,

с целью обеспечения возможности регулирования интервала между словами в широких пределах, выход дешифратора, соединенный со входом блока управления, подключен ко входу триггера со счетным входом, выходы которого подключены к

третьим входам упомянутых логических элементов И и к первым входам двух дополнительных логических элементов И, вторые входы которых соединены через узел задержки с одним из выходов блока управления, выходы - с управляющими входами регистров, а другой выход блока управления подключен к сбросовому входу счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1980 |

|

SU898419A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1985 |

|

SU1277123A1 |

| Устройство для преобразования параллельного кода в последовательный | 1975 |

|

SU549804A1 |

| Устройство для соряжения цифровой вычислительной машины с внешним накопителем | 1975 |

|

SU575653A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1987 |

|

SU1432534A1 |

| Устройство для сопряжения электронно-вычислительной машины с абонентом | 1984 |

|

SU1238088A1 |

| Устройство для сопряжения электронной вычислительной машины с абонентом | 1983 |

|

SU1137474A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1989 |

|

SU1679495A1 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

Авторы

Даты

1976-07-05—Публикация

1975-04-07—Подача