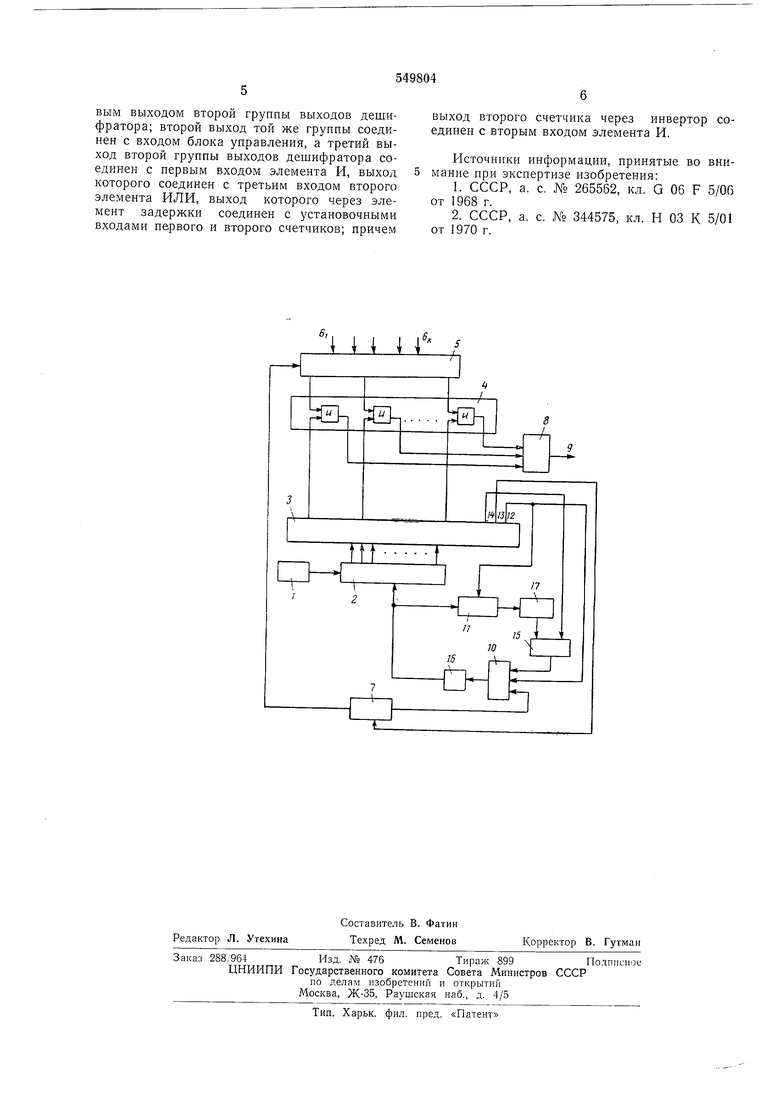

динены с дешифратором 3. Первая группа выходов дешифратора 3 соединена с первой группой входов блока 4 элементов И, вторая группа входов которого соединена с выходами регистра 5, информационные входы которого подключены к входным шинам , а управляющий вход соединен с первым выходом блока 7 управления. Выходы блока 4 элементов И соединены с входами элемента ИЛИ 8, выход которого подключен к выходной шине 9. Иервый вход элемента ИЛИ 10 соединен с вторым выходом блока 7 управления, второй вход - с информационным входом счетчика // и выходом 12 второй группы выходов дешифратора 3, выход 13 той же группы соединен с входом блока 7 управления, а выход 14 - с первым входом элемента И /5, выход которого соединен с третьим входом элемента ИЛИ 10. Выход элемента ИЛИ 1П через элемент 16 задержки соединен с установочными входами счетчиков 2 и //. Выход счетчика // через инвертор 17 соединен со вторым входом элемента И 15.

Перед началом работы с блока 7 управления через элемент ИЛИ 10 на установочный вход счетчика 2 подается сигнал сброса, а на установочный вход счетчика // - сигнал установки в положение, соответствующее отсчету одной единицы. С другого выхода блока 7 на управляющий вход регистра 5 подается сигнал, по которому в него записывается слово, подлежащее преобразованию из параллельного кода в последовательный. Работа схемы начинается с отсчета числа импульсов, поступающих с генератора 1 импульсов на информационный вход счетчика 2. С выхода счетчика 2 в параллельнолт коде на вход дешифратора 3 подается число отсчитанных импульсов. Когда это число дойдет до величины, соответствующей появлению сигнала на выходе 3, первой группы выходов дешифратора 3, первый логический элемент И блока 4 элементов И иронускает информацию («нуль или «единицу) из первого разряда регистра 5 на вход элемента ИЛИ 8. Аналогично последовательно опрашиваются все разряды регистра 5, и информация с них в последовательном коде через элемент ИЛРТ 8 поступает на выходную шину 9.

Через заданное время после опроса последнего разряда регистра появляется сигнал на выходе 14 второй группы выходов дешифратора 3 и, пройдя через элемент И 15, открытый сигналом с инвертора /7, элемент ИЛИ 10 и элемент 16 задержки, сбрасывает в «нуль счетчик 2 и записывает вторую «единицу в счетчик //. Счетчик 2 снова начинает отсчитывать импульсы, поступающие с генератора / импульсов, и последовательно опрашивать разряды регистра 5.

По окончании второго цикла опроса снова появляется сигнал на выходе 14 дешифратора 3, и сбрасывается в нулевое состояние счетчик 2, а счетчик 11 отсчитывает еще одну единицу.

После очередного цикла опроса регистра 5 счетчик // заполняется (его емкость равна требуемому числу повторений), на его выходе появляется потенциальный сигнал, который, пройдя через инвертор 17, снимает разрешающий сигнал со входа элемента И 15.

Поскольку счетчик 2 сбрасывается в нуль сигналом, переполнившим счетчик 11, начинается новый цикл опроса регистра 5, но

0 после его окончания сигнал с выхода 14 дешифратора 3 не проходит через элемент И 15 и счетчик 2 продолжает считать.

На блок 7 управления с выхода 13 дешифратора 3 поступает сигнал, по которому

5 блок 7 управления дает команду в регистр 5 на сброс информации и запись нового слова.

Через заданный интервал времени появляется сигнал на выходе 12 дешифратора 3, который сбрасывает в нуль счетчик // и,

П пройдя через элемент ИЛИ 10 и элемент 16 задержки сбрасывает в «нуль счетчик 2 и записывает «единицу в счетчик 11. Начинается многократный опрос и передача в последовательном коде следующего слова.

Интервал времени между окончанием последнего опроса одного слова и началом опроса следующего слова задается соответствующим выбором числа импульсов, определяю0щим появление сигнала на выходе 12 дешифратора.

Использование предлагаемого устройства обеспечивает по сравнению с известными устройствами следующие преимущества: п-крат5ное повторение каждого слова в последовательном коде и формирование требуемых интервалов времени между повторениями одного и того же слова и между различными словами достигается без существенного услож0нения аппаратуры.

Формула изобретения

Устройство для преобразования парал5лельного кода в последовательный, содержащее генератор импульсов, выход которого соединен с информационным входом первого счетчика, выходы которого соединены с дешифратором, первая группа выходов которого соединена с нервой группой входов блока

0 элементов И, вторая группа входов которого соедииена с выходами регистра, информационные входы которого подключены к входным шинам, а управляющий вход соединен с первым выходом блока управления, выходы блока элементов И соединены с входами первого элемента ИЛИ, выход которого подключен к выходной шине, элемент задержки, отличающееся тем, что, с целью расширения

0 класса решаемых задач, в него дополнительно введены второй счетчик, инвертор, элемент И и второй элемент ИЛИ, первый вход которого соединен с вторым выходом блока управления, второй вход соединен с инфор5мационным входом второго счетчика и первым выходом второй группы выходов дешифратора; второй выход той же группы соединен с входом блока управления, а третий выход второй группы выходов дешифратора соединен с первым входом элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, выход которого через элемент задержки соединен с установочными входами первого и второго счетчиков; причем

выход второго счетчика через инвертор соедииеи с вторым входом элемента И.

Источники информации, принятые во внимание при экспертизе изобретения:

1.СССР, а. с. № 265562, кл. G 06 F 5/06 от 1968 г.

2.СССР, а. с. N° 344575, кл. Н 03 К 5/01 от 1970 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1980 |

|

SU898419A1 |

| Постоянное запоминающее устройство | 1974 |

|

SU741321A1 |

| Устройство для ввода-вывода информации | 1982 |

|

SU1061128A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU824312A1 |

| Устройство для формирования учебной информации | 1988 |

|

SU1562951A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1989 |

|

SU1679495A1 |

| Многоканальное устройство для сопряжения абонентов с ЦВМ | 1989 |

|

SU1697081A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1987 |

|

SU1432534A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1985 |

|

SU1277123A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

М I /

Авторы

Даты

1977-03-05—Публикация

1975-01-10—Подача