(5J) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования входных воздействий в системе программного контроля | 1980 |

|

SU920729A1 |

| Устройство для умножения | 1978 |

|

SU771669A1 |

| Программное устройство управления | 1986 |

|

SU1339558A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

I

Изобретение otHOcwTCfl к автоматике и вычислительной технике и может быть использовано при построении преобразователей с заданием определенной циклогрёммы выдачи последовательных кодов и многократным повторением каж:дого кода.

Известен преобразователь параллельного кода в последовательный, содержащий счетчик, генератор импульсов, соединенный со входом счетчика, который подключен к дешифратору, группу элементов И, группу регистров, блок управления, триггер со счетным входом и элемент задержки , причем выход дешифратора соединен со входом триггера со счетным входо, выход которого соединен с входами элементов И группы, выход блока упраапения соединен со входом сброса счет« 1ка 11.

Недостатком данного преобразователя является наличие неопределенности при появлении нулевого кода на его выходе, так как этот «од может являться результатом неисправности преобразователя.

Наиболее близким решением данной задачи по технической сущности и схемному построению является преобразователь параллельного кода в последовательный, содержащий регистр, группу элементов И, первый элемент ИЛИ, входы которого соединены с выходами элементов И группы, дешифраторS первый

10 и второй счетчики, генератор импульсов,блок: управлений, элемент И, элемент задержки и второй элемент ИЛИ, причем выходы первого счетчика соединена со входами дешифратора, первая

15 группа выходов которого соединена со входами элементов И группы, а выходы второй группы дешифратора соединены со входом блока управления, вхо„ дом сброса второго счетчика и через элементы И, ИЛИ, задержки со входом сброса первого счетчика f2.

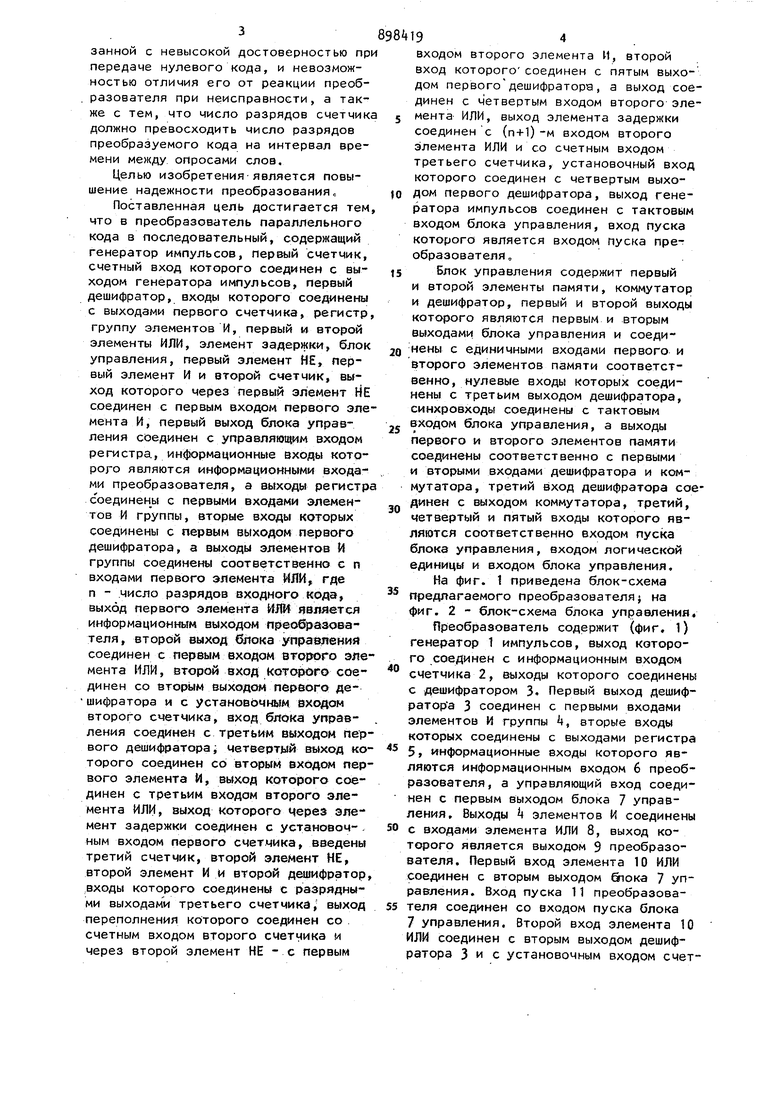

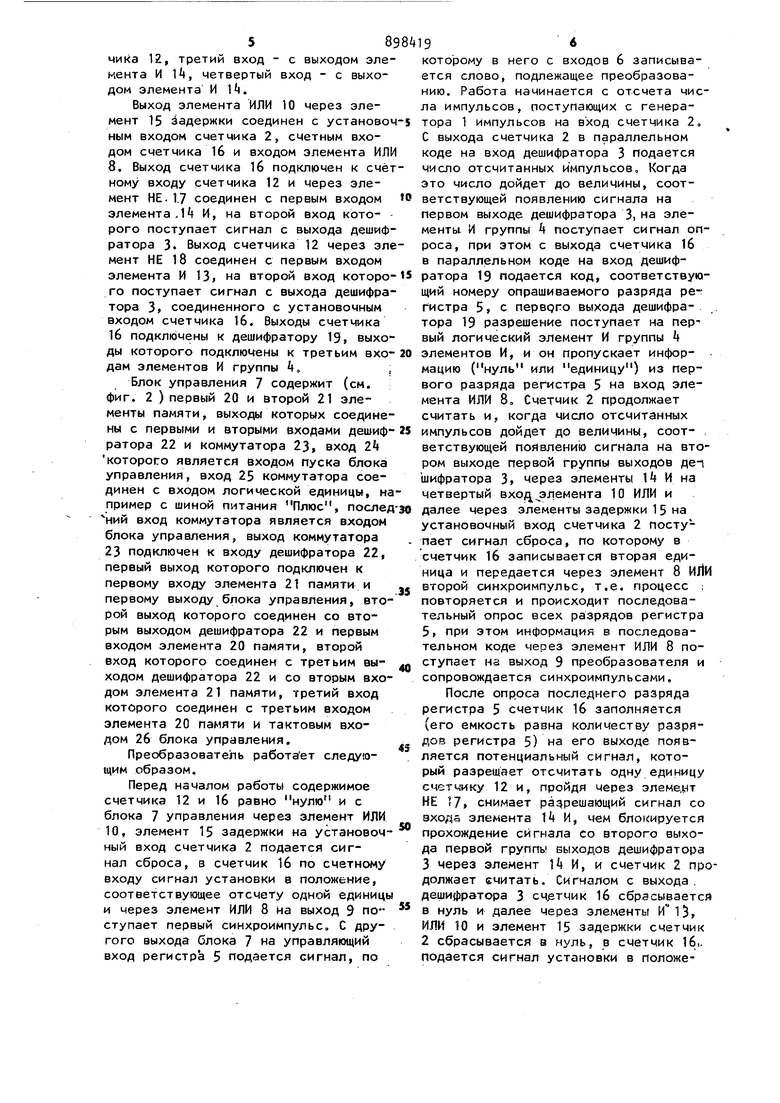

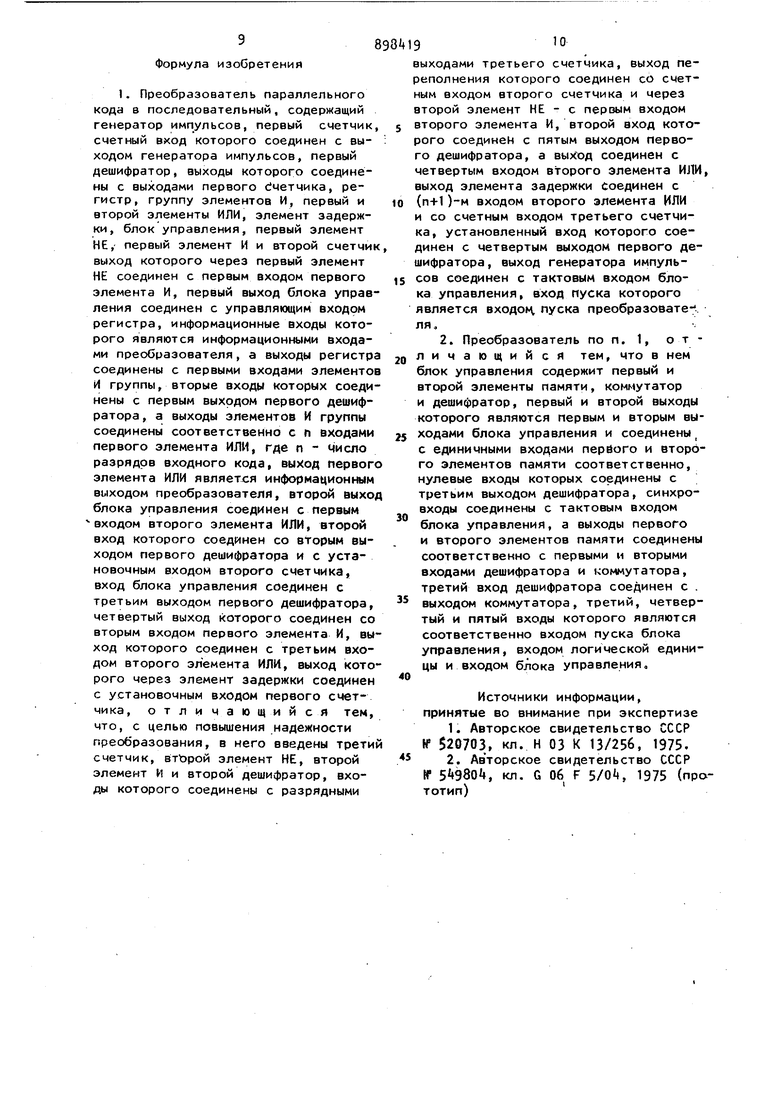

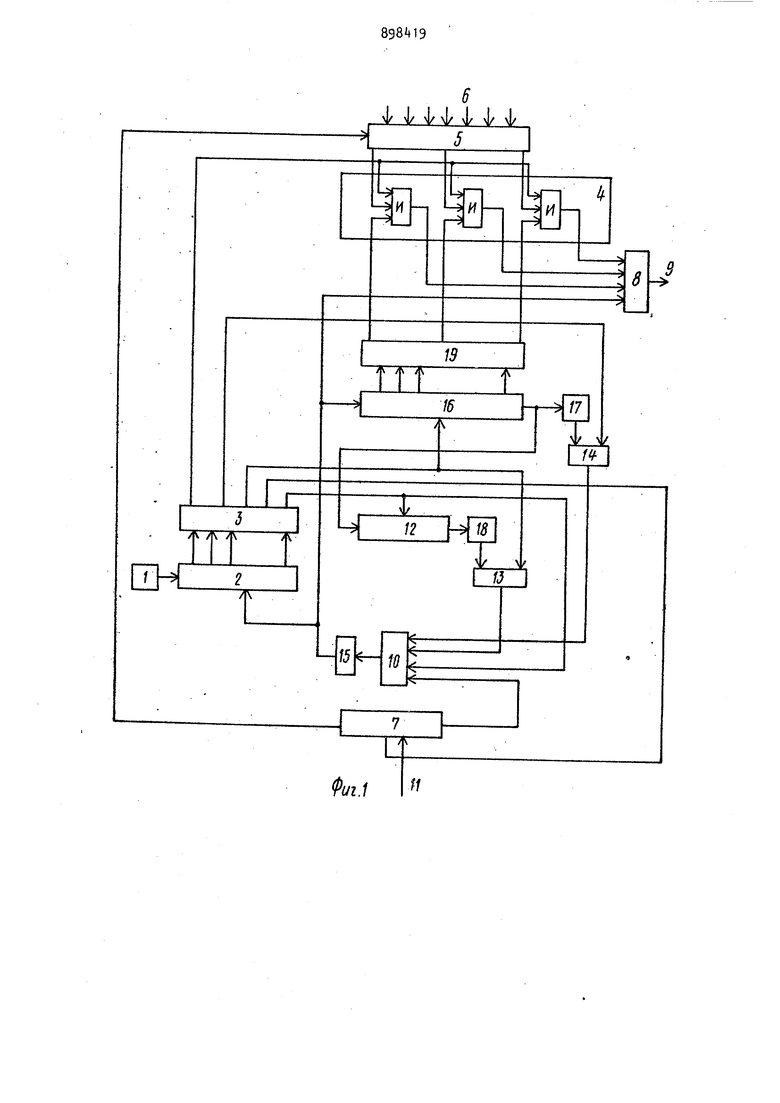

Недостаток этого преобразователя состоит в его низкой надежности, свя3занной с невысокой достоверностью пр передаче нулевого кода, и невозможностью отличия его от реакции преобразователя при неисправности, а также с тем, что число разрядов счетчик должно превосходить число разрядов преобразуемого кода на интервал времени между опросами слов. Целью изобретения-является повышение надежности преобразования Поставленная цель достигается тем что в преобразователь параллельного кода в последовательный, содержащнй генератор импульсов, первый счетчик, счетный вход которого соединен с выходом генератора импульсов, первый дешифратор, входы которого соединены с выходами первого счетчика, регистр группу элементов И, первый и второй элементы ИЛИ, элемент задержки, блок управления, первый элемент НЕ, первый элемент И и второй счетчик, выход которого через первый элемент НЕ соединен с первым входом первого эле мента И, первый выход блока управления соединен с управляющим входом регистра., информа14ионные входы которого являются информационными входами преобразователя, а выходы регистр соединены с первыми элементов И группы, вторые входы которых соединены с первым выходом первого дешифратора, а выходы элементов И группы соединены соответетвенно с п входами первого элемента ИЛИ, где п - число разрядов входного «ода, выход первого элемента ИЛИ является информационным выходом преобразователя, вторьй выход блока управлений соединен с первым входом второго эле мента ИЛИ, второй вход Которого соединен со вторым выходсж первого де шифратора и с установочным входом второго счетчика, вход блока управления соединен с третьим выходом пер вого дешифратора j четвертый выход ко торого соединен со вторым входом пер вого элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, выход которого через элемент задержки соединен с установоч-ным входом первого счетчика, введены третий счетчик, второй элемент НЕ, второй элемент И И второй дешифратор входы которого соединены с разрядными выходами третьего счетчика, выход переполнения которого соединен со . счетным входом второго счетчика и через второй элемент НЕ - с первым 94 входом второго элемента И, второй вход которогосоединен с пятым выходом первогодешифратора, а выход соединен с четвертым входом второго элемента ИЛИ, выход элемента задержки соединен с (п+1) -м входом второго элемента ИЛИ и со счетным входом третьего счетчика, установочный вход которого соединен с четвертым выходом первого дешифратора, выход генератора импульсов соединен с тактовым входом блока управления, вход пуска которого является входом пуска преобразователя „ Блок управления содержит первый и второй элементы памяти, коммутатор и дешифратор, первый и второй выходы которого являются первым и вторым выходами блока управления и соединены с единичными входами первого и второго элементов памяти соответственно, нулевые входы которых соединены с третьим выходом дешифратора, синхровходы соединены с тактовым входом блока управления, а выходы первого и второго элементов памяти соединены соответственно с первыми и вторыми входами дешифратора и коммутатора, третий вход дешифратора соединен с выходом коммутатора, третий, четвертый и пятый входы которого являются соответственно входом пуска блока управления, входом логической единиць и входом блока управления. На фиг. 1 приведена блок-схема предлагаемого преобразователя} на фиг. 2 - блок-схема блока управления Преобразователь содержит (фиг. 1) генератор 1 импульсов, выход которого соединен с информационным входом счетчика 2, выходы которого соединены с дешифратором 3 Первый выход дешифратора 3 соединен с первыми входами элементов И группы k, вторые входы которых соединены с выходами регистра 5, информационные входы которого являются информационным входом 6 преобразователя, а управляющий вход соединен с первым выходом блока 7 управления. Выходы 4 элементов И соединены с входами элемента ИЛИ 8, выход которого является выходом 9 преобразователя. Первый вход элемента 10 ИЛИ соединен с вторым выходом &1ока 7 управления. Вход пуска 11 преобразователя соединен со входом пуска блока 7 управления. Второй вход элемента 10 ИЛИ соединен с вторым выходом дешифратора 3 и с установочным входом счетчика 12, третий вход - с выходом элемента И 1, четвертый вход - с выходом элемента И I.

Выход элемента ИЛИ 10 через элемент 15 задержки соединен с установоч-5 ным входом счетчика 2, счетным входом счетчика 16 и входом элемента ИЛИ 8. Выход счетчика 1б подкщочен к счётному входу счетчика 12 и через элемент НЕ. 1.7 соединен с первым входом О элемента,I И, на второй вход которого поступает сигнал с выхода дешифратора 3. Выход счетчика 12 через элемент НЕ 18 соединен с первым входом элемента И 13, на второй вход которо-5 го поступает сигнал с выхода дешифратора 3, соединенного с установочным входом счетчика 16. Выходы счетчика 16 подключены к дешифратору 19, выходы которого подключены к третьим входам элементов И группы i, , Блок управления 7 содержит (см. фиг. 2 ) первый 20 и второй 21 элементы памяти, выходы которых соедимены с первыми и вторыми входами дешиф- 25 ратора 22 и коммутатора 23, вход 2 которого является входом пуска блока управления, вход 25 коммутатора соединен с входом логической единицы, н пример с шиной питания Плюс, после НИИ вход коммутатора является входом блока управления, выход коммутатора 23 подключен к входу дешифратора 22, первый выход которого подключен к первому входу элемента 21 памяти и первому выходу блока управления, вто рой выход которого соединен со вторым выходом дешифратора 22 и первым входом элемента 20 памяти, второй вход которого соединен с третьим выходом дешифратора 22 и со вторым вхо дом элемента 21 памяти, третий вход которого соединен с третьим входом элемента 20 памяти и тактовым входом 26 блока управления. Преобразователь работает следующим образом. Перед началом работы содержимое счетчика 12 и 16 равно нулю и с блока 7 управлений через элемент ИЛИ 10, элемент 15 задержки на установоч ный вход счетчика 2 подается сигнал сброса, в счетчик 16 по счетному входу сигнал установки в положение, соответствующее отсчету одной единиц и через элемент ИЛИ 8 на выход 9 по ступает первый синхроимпульс, С другого выхода блока 7 на управляющий вход регистра 5 подается сигнал, по

которому в него с входов 6 записывается слово, подлежащее преобразованию. Работа начинается с отсчета числа импульсов, поступающих с генератора 1 импульсов на вход счетчика 2, С выхода счетчика 2 в параллельном коде на вход дешифратора 3 подается число отсчитанных импульсов. Когда это число дойдет до величины, соответствующей появлению сигнала на первом выходе дешифратора 3, на элементы И группы k поступает сигнал опроса, при этом с выхода счетчика 1б в параллельном коде на вход дешифратора 19 подается код, соответствующии номеру опрашиваемого разряда регистра 5, с первдго выхода дешифратора 19 разрешение поступает на пер вый логический элемент И группы k элементов И, и он пропускает информацию (нуль или единицу) из первого разряда регистра 5 на вход элемента ИЛИ В, Счетчик 2 продолжает считать и, когда число отсчитанных импульсов дойдет до величины, соответствующей появлению сигнала на втором выходе первой группы выходов деп шифратора 3, через элементы 1 И на четвертый Bxojtj элемента 10 ИЛИ и далее через элементы задержки 15 на установочный вход счетчика 2 поступает сигнал сброса, по которому в счетчик 16 записывается вторая единица и передается через элемент 8 HJiM второй синхроимпульс, т.е. процесс i повторяется и происходит последовательный опрос всех разрядов регистра 5, при этом информация в последовательном коде через элемент ИЛИ 8 поступает на выход 9 преобразователя и сопровождается синхроимпульсами. После опроса последнего разряда регистра 5 счетчик 16 заполняется (его емкость равна количеству разрядов регистра 5) на его выходе появляется потенциальный сигнал, который разрешает отсчитать одну единицу счетчику 12 и, пройдя через элеме,мт НЕ 7, снимает разрешающий сигнал со входа элемента 14 И, чем блокируется прохождение сигнала со второго выхода первой группы выходов дешифратора 3 через элемент 14 И, и счетчик 2 продолжает считать. Сигналом с выхода , дешифратора 3 счетчик 16 сбрасывается в нуль и далее через элементы И 15, ИЛИ 10 и элемент 15 задержки счетчик 2 сбрасывается в нуль, в счетчик 16,. подается сигнал установки в положение, соответствующее отсчету одной единицы и формируется очередной синхроимпульс, прИ этом начинает повторяться описанный цикл ortpoca разрядов регистра 5.

После очередного цикла опроса регистра 5 счетчик 12 заполняется (его емкость равна требуемому числу повторений), на его выходе появляется потенциальный сигнал, который, пройдя через элемент НЕ 18, снимает разрешающий сигнал со входа элемента И 13 чем блокируется прохождение сигнала с третьего выхода второй группы выходов дешифратора 3 через элемент И 13 и счетчик 2 продолжает считать. На блок 7 управления со второго выхода второй группы выходов дешифратора 3 поступает.сигнал, по которому блок 7 управления дает команду в регистр 5 на сброс информации и запись нового слова

Через заданный интервал времени появляется сигнал на втором выходе дешифратора 3, который сбрасывает в нуль счетчик 12 и, пройдя через элементы ИЛИ 10 и элемент 15 задержки, сбрасывает в нуль счетчик 2, запи cbiBaer единицу в счетчик 16 и передается ачередной синхроимпульс через элемент 8 ИЛИ на выход 9. Начинается многократный юпрос, и передача следующего слова в последовательном коде, сопровождаемом синхроимпульсами. Интервал времени между синхроимпульсом и информационным импульсом задается соответствующим выбором чис ла отсчитанных импульсов счетчиком 2, определяющим появление сигнала на первом выходе дешифратора 3 между синхроимпульсами соответственно определяется появление сигнала на втором выходе дешифратора 3 между словами сигналом на третьем выходе дешифратора 3 и между повторяющимися словами сигналом с второго выхода дешифратора 3«

Блок управления 7 работает следующим образом.

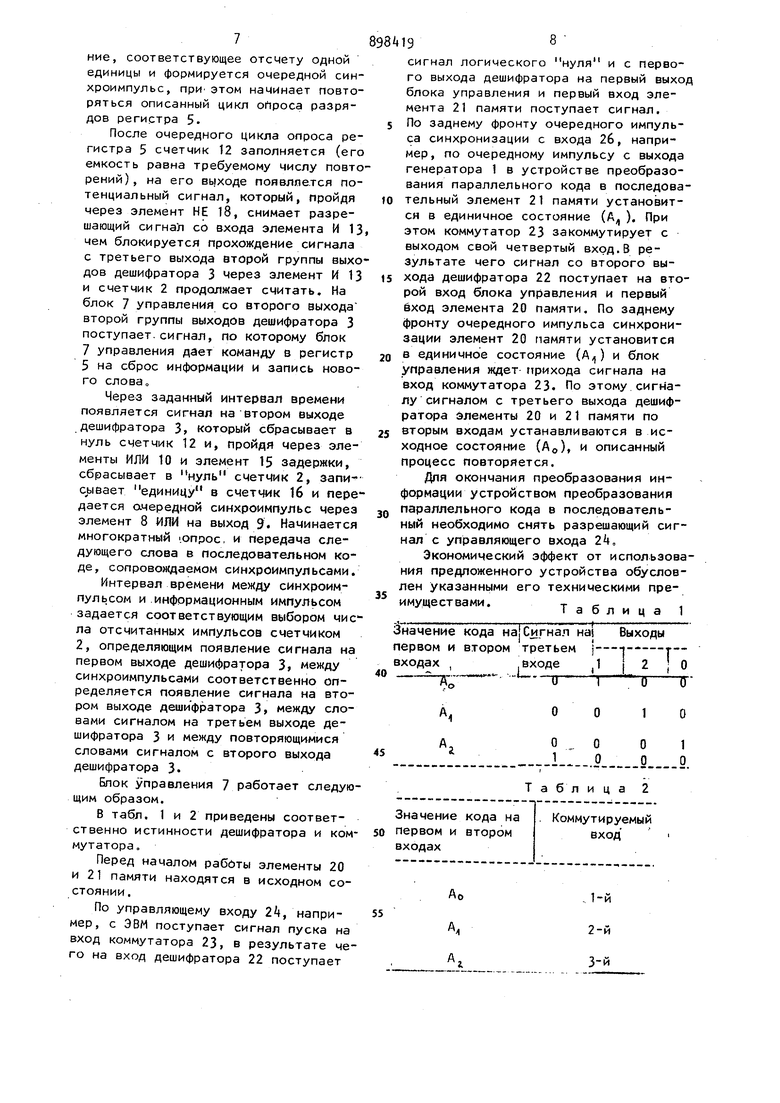

В табл. 1 и 2 приведены соответственно истинности дешифратора и коммутатора.

Перед началом работы элементы 20 и 21 памяти находятся в исходном состоянии.

По управляющему входу 24, например, с ЭВМ поступает сигнал пуска на вход коммутатора 23, в результате чего на вход дешифратора 22 поступает

сигнал логического нуля и с первого выхода дешифратора на первый выход блока управления и первый вход элемента 21 памяти поступает сигнал. 5 По заднему фронту очередного импульса синхронизации с входа 26, например, по очередному импульсу с выхода генератора 1 в устройстве преобразования параллельного кода в последовательный элемент 21 памяти установится в единичное состояние (А, ). При

этом коммутатор 23 закоммутирует с выходом свой четвертый вход,В результате чего сигнал со второго выхода дешифратора 22 поступает на второй вход блока управления и первый вход элемента 20 памяти. По заднему фронту очередного импульса синхронизации элемент 20 памяти установится 20 в единичное состояние () и блок управления ждет прихода сигнала на вход коммутатора 23. По этому сигналу сигналом с третьего выхода дешифратора элементы 20 и 21 памяти по вторым входам устанавливаются в исходное состояние (АО), и описанный процесс повторяется.

Для окончания преобразования информации устройством преобразования параллельного кода в последовательный необходимо снять разрешающий си| нал с управляющего входа 2,

Экономический эффект от использования предложенного устройства обусловлен указанными его техническими преФормула изобретения 1. Преобразователь параллельного кода в последовательный, содержащий генератор импульсов, первый счетчик счетный вход которого соединен с выходом генератора импульсов, первый дешифратор, выходы которого соединены с выходами первого Счетчика, регистр, группу элементов И, первый и второй элементы ИЛИ, элемент задержки, блок управления, первый элемент НЕ, первый элемент И и второй счетчи выход которого через первый элемент НЕ соединен с первым входом первого элемента И, первый выход блока управ ления соединен с управляющим входрм регистра, информационные входы которого являются информационными входами преобразователя, а выходы регистр соединены с первыми входами элементо И группы, вторые входы которых соеди нены с первым выходом первого дешифратора , а выходы элементов И группы соединены соответственно с п входами первого элемента ИЛИ, где п - число разрядов входного кода, выход первог элемента ИЛИ является информационьмм выходом преобразователя, второй выхо блока управления соединен с первым входом второго элемента ИЛИ, второй вход которого соединен со вторым выходом первого дешифратора и с установочным входом второго счетчика, вход блока управления соединен с третьим выходом первого дешифратора, четвертый выход которого соединен со вторым входом первого элемента И, вы ход которого соединен с третьим входом второго элемента ИЛИ, выход кото рого через элемент задержки соединен с установочным входом первого счетчика, отличающийся тем, что, с целью повышения надежности преобразования, в него введены трети счетчик, втЪрой элемент НЕ, второй элемент И и второй дешифратор, входы которого соединены с разрядными 9° ыходами третьего счетчика, выход пееполнения которого соединен со счетным входом второго счетчика и через второй элемент НЕ - с персзым входом второго элемента И, второй вход которого соединен с пятым выходом первого дешифратора, а выход соединен с четвертым входом второго элемента ИЛИ, выход элемента задержки Соединен с (п+1)-м входом второго элемента ИЛИ и со счетным входом третьего счетчика, установленный вход которого соединен с четвертым выходом первого дешифратора, выход генератора импульсов соединен с тактовым входом блока управления, вход пуска которого является входом, пуска преобразовате-. ля. 2. Преобразователь по п. 1, отличающийся тем, что в нем блок управления содержит первый и второй элементы памяти, коммутатор и дешифратор, первый и второй выходы которого являются первым и вторым вЫходами блока управления и соединены, с единичными входами перйого и второго элементов памяти соответственно, нулевые входы которых соединены с третьим выходом дешифратора, синхровходы соединены с тактовым входом блока управления, а выходы первого и второго элементов памяти соединены соответственно с первыми и вторыми входами дешифратора и коммутатора, третий вход дешифратора соединен с . выходом коммутатора, третий, четвертый и пятый входы которого являются соответственно входом пуска блока управления, входом логической единицы и входом блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР If 520703, кл. Н 03 К 13/256, 1975. 2.Авторское свидетельство СССР If 5 9804, кл. G 06 F , 1975 (прототип)

Ф у V 1/ b у xb

23

22

Авторы

Даты

1982-01-15—Публикация

1980-03-03—Подача