Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах дискретной автоматики для определения экстремальных значений,

Известно устройство, содержащее регистры, группу элементов И элементы ИЛИ TiE 1И. Известное устройство имеет низкое быстродействие и не позволяет выделять параметры по мере уменьшения (увеличения) их значения. Наиболее близким к изобретению является устройство, содержащее регистры, группу элементов ИЛИ, первую группу элементов И и группу элементов НЕ. Это устройство имеет низкое быстродействие при выделении параметров по мере возрастания их значения и не позволяет указывать номера регистров по мере определения значений параметров, содержащихся в них,

Целью изобретения является повышение быстродействия и расширение функциональных возможностей. В описываемом устройстве это достигается тем, что оно содержит вторую группу элементов И, блок

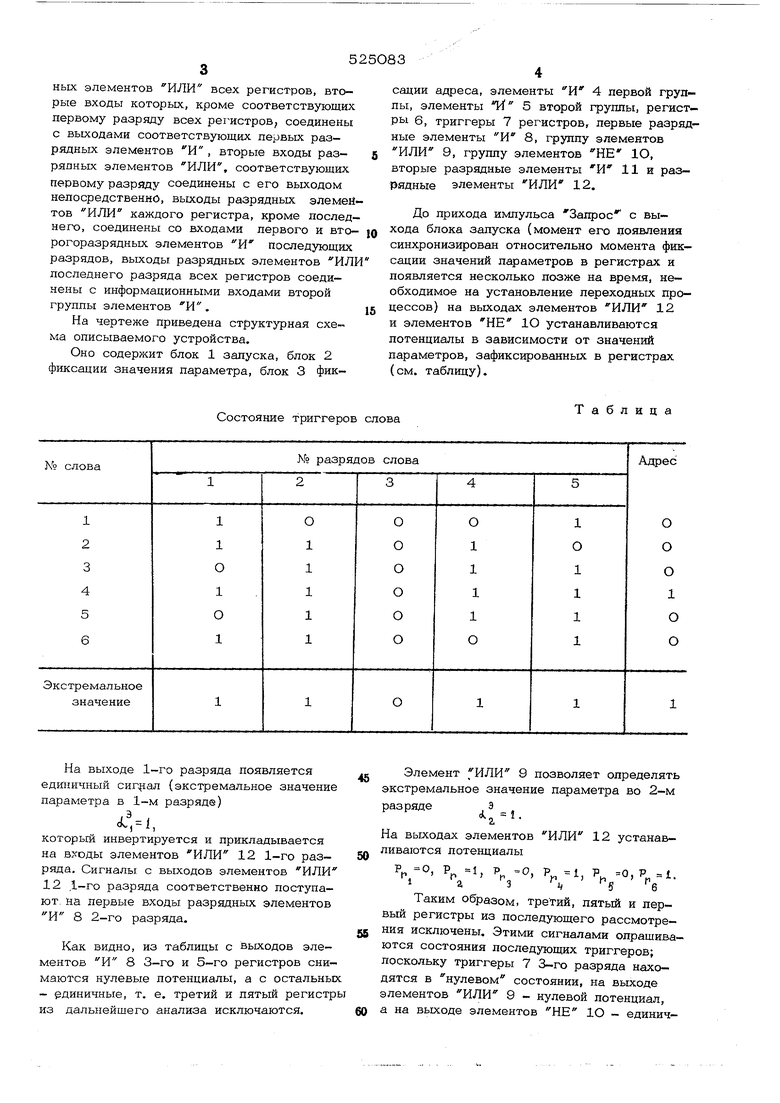

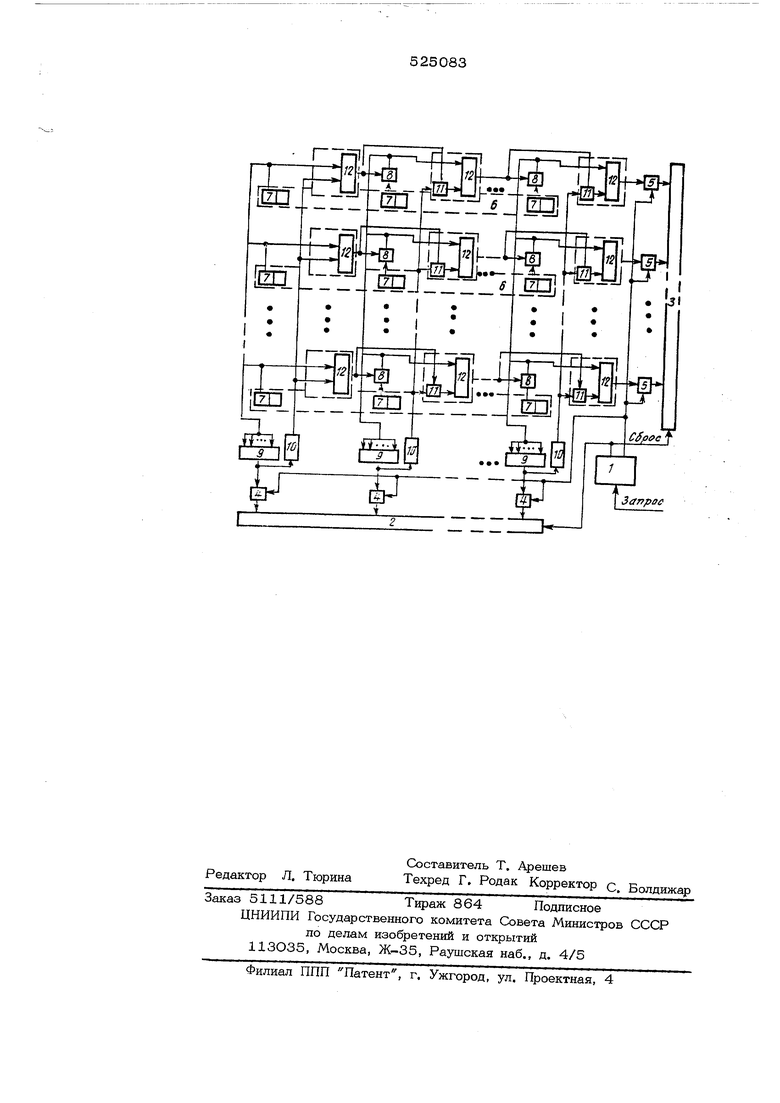

запуска, блок фиксации значения параметра, блок фиксации адреса, разрядные элементы И и ИЛИ, причем выходы первых разрядов всех регистров непосредственно, а выходы остальных разрядов регистров через первые разрядные элементы И соединены со входами соответствующих элементов ИЛИ группы, выходы которых соединенысо входами группы элементов НЕ и информационными входами элементов И первой группы, управляющий вход которой соединен с управляющим входом элементов И второ группы и с первым Е.ЬКОДОМ блока запуска, вход которого соединен со входом устройства, выходы элементов И первой группы соединены с информационными входами блок фиксации значения параметра, управляющий вход которого соединен со вторым выходом блока запуска и управляющим входом блока фиксации адреса, информационные входы которого соединены с выходами элементов И второй группы, первый выход группы элементов НЕ непосредственно, а остальные - через вторые разрядные элементы И соединены с первыми входами разрядных элементов ИЛИ всех регистров, вторые входы которых, кроме соответствующих первому разр5щу всех регистров, соединены с выходами соответствующих первых разрядных элементов И , вторые входы разряпных элементов ИЛИ, соответствующих первому разраду соединены с его выходом непосредственно, выходы разрядных элемей тов ИЛИ каждого регистра, кроме последнего, соединены со входами первого и вто- рогоразрядных элементов И последующих разрядов, выходы разрядных элементов ИЛ последнего разряда всех регистров соединены с информационными входами второй группы элементов И. На чертеже приведена структ эная схема описываемого устройства. Оно содержит блок 1 запуска, блок 2 фиксации значения параметра, блок 3 фикСостояние триггеров слова

Таблица сации адреса, элементы И 4 первой группы, элементы И 5 второй группы, регист- РЬ1 6, триггеры 7 регистров, первые разрядные элементы И 8, группу элементов ИЛИ 9, группу элементов НЕ 1О, вторые разрядные элементы И 11 и разрядные элементы ИЛИ 12. До прихода импульса Запрос с выхода блока запуска (момент его появления синхронизирован относительно момента фиксации значений параметров в регистрах и появляется несколько позже на время, необходимое на установление переходных процессов) на выходах элементов ИЛИ 12 и элементов НЕ Ю устанавливаются потенциалы в зависимости от значений параметров, зафиксированнььх в регистрах (см. таблицу).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска экстремального значения параметров | 1977 |

|

SU922725A1 |

| Устройство для поиска экстремальных чисел | 1980 |

|

SU883895A1 |

| Устройство для поиска экстремальных значений | 1975 |

|

SU534762A1 |

| Устройство для контроля параметров | 1979 |

|

SU842721A1 |

| Устройство для упорядоченной выборки значений параметра | 1982 |

|

SU1048470A1 |

| Устройство для упорядоченной выборки значений параметра | 1978 |

|

SU739527A1 |

| Многоканальное устройство для упорядоченной выборки значений параметра | 1978 |

|

SU898404A2 |

| Устройство для сравнения @ @ -разрядных двоичных чисел | 1981 |

|

SU983703A1 |

| СПОСОБ ЦЕНТРАЛИЗОВАННОГО КОНТРОЛЯ N ОБЪЕКТОВ | 2000 |

|

RU2198418C2 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

На выходе 1-го разряда появляется единичный сигнал (экстремальное значение параметра в разряд®)

1,

который инвертируется и прикладывается на входы элементов ИЛИ 12 1-го разряда. Сигналы с выходов элементов ИЛИ 12 1-го разряда соответственно поступают на первые входы разрядных элементов И 8 2-го разряда.

Как видно, из таблицы с выходов элементов И 8 3-го и 5-го регистров снимаются нулевые потенциалы, а с остальных - единичные, т. е. третий и пятый регистры из дальнейшего анализа исключаются.

Элемент ИЛИ 9 позволяет определять экстремальное значение параметра во 2-м

разрядеJ 3 ,

а-На выходах элементов ИЛИ 12 устанавливаются потенциалы

-° 1, Р.

-О.

Р 1 РИ о.Р. i.

1 -а 3Таким образом, третий, пятый и первый регистры из последующего рассмотрения исключены. Этими сигналами опрашиваются состояния последующих триггеров; поскольку триггеры 7 3-го разряда находятся в нулевом состоянии, на выходе элементов ИЛИ 9 - нулевой потенциал, а на выходе элементов НЕ 1О - единичный сигнал, тогда на выходах элементов ИЛИ 12 третьего разряда сохраняются неизменныгх и сигналы Сигналы с выходов разрядны,х элементов 4-го разряда поступают на вход элеме тов ИЛИ 9, и определяется экстремальное значение параметра во втором разряде L, i, на выходах элементов ИЛИ 12 устанавливаются потеьщиалы Р„ о; Р : Р о o- г з Наконец, олределяется сигнал на выходе элементов ИЛИ 9 5-го разряда , на выходах логических элементов ИЛИ 1 устанавливаются потенциалы Р 0. Р., 0 РП,-О, Pf.o,.. т, е. единичный сигнал проходит через все разрядные элементы регистра, в котором зафиксировано наибольшее значение параметра среди N лараметров, через остальные - в зависимости от зафиксированного значения не проходит совсем или проходят через определенную часть блоков. На выходах элементов ИЛИ 9 устанавливается наибольшее значение (зафиксированно в 4-м регистре) параметра (11О11), а на выходах элементов ИЛИ 5-го разряда код его адреса (ООО1О). Процесс установления значения экстремального параметра (наибольшего или наименьшего) определяется только быстродействием элементов 8, 9, 1О, 11 и 12. При поступлении сигнала Запрос на вход блока запуска 1 блоки 2 и 3 фиксации значения и адреса экстремального параметра устанавливаются в исходное состояние сигналом с соответствуюшего выхода блока 1, экстремальное значение (11О11) и код его адреса (ООО1ОО) фиксируются соответственно в блоках 2 и 3. Моменты записи параметров в регистры и поступление сигнала Запрос синхронизированы между собой, момент Запрос поступает несколько позже на время, необходимое на установления экстремального зн чения на выходах элементов ИЛИ 9 и эл ментов И 11 первого разряда. Таким образом, описываемое устройство позволяет обрабатывать весь массив информации за один цикл и устанавливать экстреальное значение параметра и адрес регистра, где оно содержится. Формула изобретения Устройство для поиска экстремальных значений, содержащее регистры, группу элементов ИЛИ, первую группу элементов И и группу элементов НЕ, о тличаюш;ееся тем, что, с целью (1Овыа1е;-шя быстродействия и расширения функдиональньгх возможностей, оно содержит вторую группу элементов И, блок чЗапуска, блок фиксации значения параметра, блок фиксации адреса, разрядные элементы И и ИЛИ, причем выходы первых разрядов всех регистров непосредственно, а вьгходы остальных разрядов регистров через первые разрядные 3ne vieHT:n И соединены со входами соответствующих элементов ИЛИ группы, выходы которых соединены со входами группы элементов НЕ и информационными входами элементов И первой группы, управляющий вход которой соединен с управляющим входом элементов И второй группы и с первым выходом блока запуска, вход рсоторого соединен со входом устройства, выходы элементов И первой грулпь; соединены с информационнымк входами блока фиксации значения параметра, управляющий вход которого соединен со вторым выходом блока запуска и управляющим входом блока фиксации адреса, информациоины:е входы которого соединены с выходами элементов И второй группь, первый выход группы элементов НЕ непосредственно, а остальные через втор1ые разрядные элементы И соединены с первыми входами разрядных элементов ИЛИ всех регистров, вторые входы которых, кроме соответствующих первому разряду всех регистров, соединены с выходами соответствующих первых разрядных элементов И, вторые входы разрядных элементов ИЛИ, соответствующих первому разряду, соединенгл с его выходом непосредственно, выходы разрядных элементов ИЛИ каждого регистра, кроме последнего, соединены со входами первого и второго разрядньтх элементов И последующих разрядов, выходы разрядных элеДГентов ИЛИ последнего разряда всех регистров соединены с информационными входами второй группы элементов И.

Авторы

Даты

1976-08-15—Публикация

1975-04-24—Подача