(5.4)УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Корреляционное устройство для определения задержки | 1982 |

|

SU1051545A1 |

| Декодер кодов Рида-Соломона | 1989 |

|

SU1777244A1 |

| Корреляционное устройство дляОпРЕдЕлЕНия зАдЕРжКи | 1979 |

|

SU849226A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Многоканальный цифроаналоговый преобразователь | 1989 |

|

SU1709527A1 |

| Устройство для текущей оценки уровня сигнала | 1984 |

|

SU1191920A1 |

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля параметров технических объектов в ЭВМ и устройствах информационно-измерительной техники при решении задач оперативной и достоверной обработки информации. Известно устройство содержащее бло регистров, группу элементов ИЛИ, первую группу элементов НЕ, первую группу элементов И, вторую группу элементов И, блок запуска, блок фиксации значения параметра, фиксации адр са, разрядные элемента И и ИЛИ,, причем выходы первых разрядов всех ре- . гисторов непосредственно, а выходы остальных разрядов регистров через первые разрядные элементы И соединены со входами соответствующих элементов ИЛИ группы, выходы которых соединены со входами группы элементов НЕ и информационными входами элементов И первой группы, управляющий вход, кото рой соединен с управляющим входом элементов И второй группы и с первым Выходом блока запуска, вход которого соединен со входом устройства, выходы элементов И первой группы соединены с информационными входами блока фиксации значения параметра, управляющий вход которого соединен со вторым выходом блока запуска и управляющим входом блока фиксации адреса; информационные входы которого соединены с выходами элементов И второй группы, первый выход группы элементов ЙЕ непосредственно, а остальные - через вторые разрядные элементы И соединены с первыми входами разрядных элементов ИЛИ всех регистров, вторые входы которыхjкроме соответствующих первому разряду всех регистров, соединены с выходами соответствующих первых разрядных элементов И, вторые входы разрядных элементов ИЛИ, соответствующих первому разряду соединены с его выходом непосредственно, выходы разрядных элементов ИЛИ каждого регистра, кроме последнего, соединены со входами пер вого и второго разрядных элементов И последующих разрядов, выходы разрядных элементов ИЛИ последнего разряда всех релкстров соединены с информационными входами второй группы элементов И . К недостаткам известного устройст ва относится ограниченность функциональных возможностей, заключающаяся в отсутствии учета результатов анали за, информации о параметрах , значения которьк не являются истинными, а содержат как составляющую значения самого параметра, так и составляющую помех. Известно .устройство для поиска экстремальных значений параметров, содержащее коммутатор опроса разрядо регистров, состоящий из двоичного счетчика дешифратора, управляемый генератор, триггер запуска, разрядные элементы И и ИЛИ, регистры записи значений контролируемых параметров, разрядные блоки логики,двухвходо вые элементы И, входы которых подключены к выходам коммутатора и раз,рядных блоков логики, блоки регистра ции экстремального значения параметра и его адрес, позволяющее за цикл работы коммутатора определить параметр, имеющий .экстремальное значение и его адрес L22. Недостатком устройства является ограниченность функциональных воз,можНостей, заключающаяся в отсутствии учета результатов анализа информации о параметрах,значение которых содержит составляющую помеху. Наиболее близким техническим решением к предлагаемому является устройство для контроля параметров, со.держащее блок регистров , узлы анализ группу элементов ИЛИ, группу элементов .И, генератор, элементы задержки, переключатель, дифференцирующие цепи в котором выходные шины управления узлов анализа соединены со входами элемента И, выход которого через nepB5.To дифференцирующую цепь подключён ко входу установки в единичное состояние триггера, прямой вьтод которого подключен ко входу второго регистра, выходы которого соединены с входными шинами переключателя, выходная шина которого подключена ко входу установки в нулевое состояние

равления первого разряда, выход первого элемента ИЛИ соединен со вхЪдом установки в нулевое состояние первого триггера, выход которого подключен

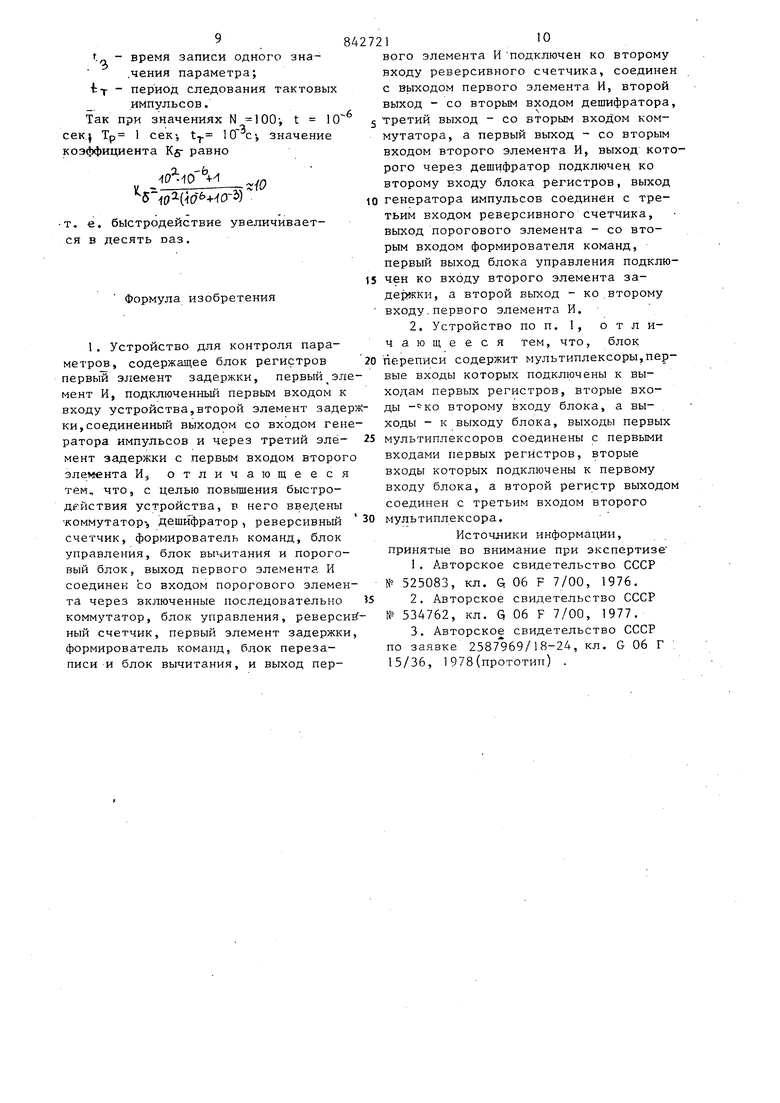

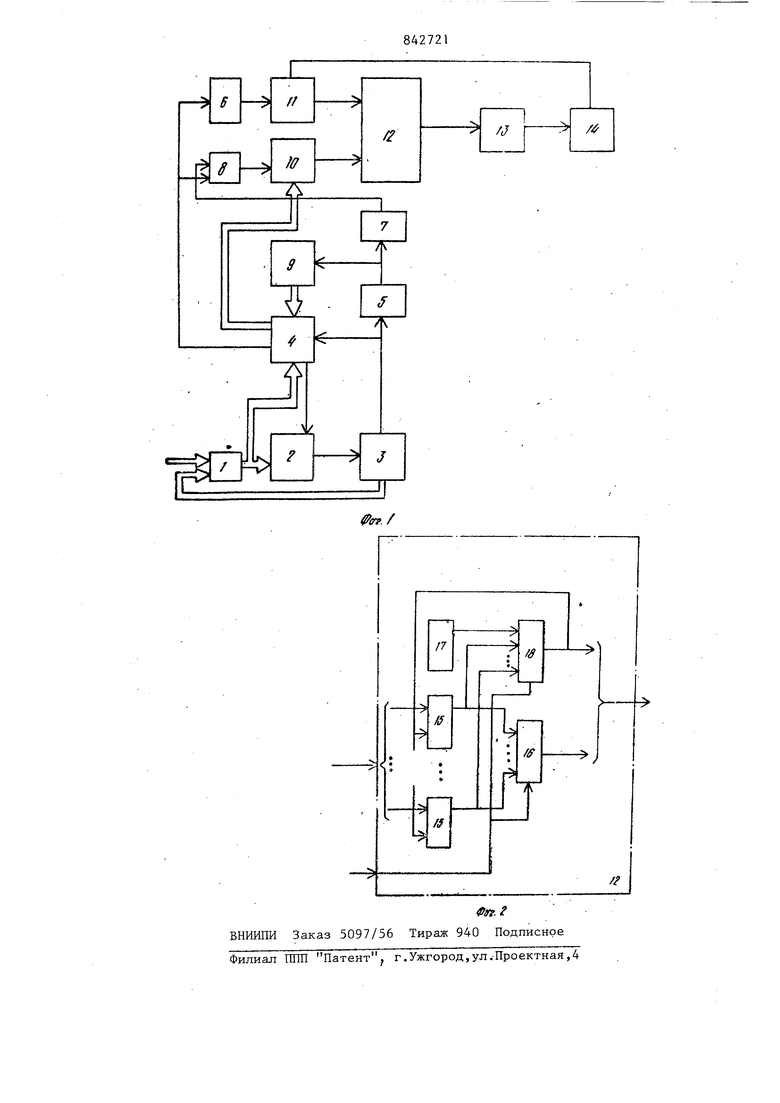

ко-вторым входам- элементов И первой групйы, выход m .-гб элемента ИЛИ, группы соединен с первым входом элемента И и с первым входом третьего элемента ИЛИ, второй вход которого

подключен к первому установочному входу узла анализа, а выход - ко входу установки в единичное состояние первого триггера и ко входу уста141 триггера, ко вторым входам элемента И группы и через вторую дифференцирующую цепь и первый элемент задержки к управляющим входам второго регистра, выход генератора тактовых импульсов- через второй элемент задержки соединен, с третьими входами элементов И группы, выход элемента ИЛИ подключен к установочным входам всех узлов анализа, вь1ход второго элемента задержки соединен со вторыми установочными входами- узлов анализа, а каждый из узлов анализа содеря т m -разрядный регистр, группы элементов И,- ИЛИ, триггеры,, элементы И, ИЛИ, НЕ, -причем информационные входы узла анализа соединены с первыми входами элементов И первой группы, а выход i-ro элемента И первой группы подключен к i-му входу первого элемента ИЛИ и ко входу i-ro разряда регистра, где i 1,2,..,, m выход j-ro разряда регибтра,где ,3,..., m, соединен с J/ -ым входом второго элемента ИЛИ и. первым .входом j-ro элемента И второй группы, второй вход которого подключен к выходу (j-l)-ro элемента ИЛИ группы, выход j-ro элемента И второй группы соединен с первым входом j-ro элемента И третьей группы и с первым входом j -го элемента ИЛИ группы, выход .(j-l)-ro элемента ИЛИ группы подключен к первому входу j -го элемента И четвертой группы, второй вход которого соединен с входом управления -го разряда, выход -го элемента И четвертой группы :i: подключен ко второму входу j -го элемента ИЛИ группы, выход первого разряда регистра соединен с первым входом второго элемента ИЛИ, i с первым входом первго элемента И . третьей группы и с первым входом первого элемента PfflH группы,, второй вход которого подключен ко входу унновки в нулевое состояние регистра, первый установочный вход узла анализ соединен со входом установки в едини ное состояние второго триггера и череЬ элемент НЕ со вторым входом элемента И, выход которого подключен ко входу установки в нулевое сос тояние второго триггера, третий вход элемента И.соединен со вторым ycTkновочным входом узла анализа, прямой выход второго триггера подключен ко вторьм входам-элементов И второй и третьей групп ктретьему входу эле ментов И четвертой, группы, выход вто рого элемента ИЛИ соединен с выходной шиной управления узла анализа fs Недостатком устройства является низкое быстродействие при обработке информации, содержащей помехи. В дискретные моменты времени в устройство поступает ряд значений контроли руемого параметра, изменяющегося по неизвестному закону, на которые накл дываются- помехи. Таким образом на входе устройства прйсутствует суммарный сигнал. Устройство не решает задачи быстрой обработки сигнала, та как оператору приходится вручную локализовать и исключать те.значения параметра, которые содержат составляющую помех-и. Цель изобретения - повьгшение быст родействия обработки контролируемых параметров.У Поставленная цель достигается тем что в устройство для контроля параметров содержащее блок регистров,. первый элемент задержки, первый элемент И, подключенный первым входом к входу устройства, второй элемент задержки, соединенный выходом со входом генератора импульсов и через третий элемент задержки с первым вхол,ом второго элемента И,, введены коммутатор, дешифратор, реверсивный счетчик, формирователь команд, блок управления, блок, вычитания и пороговый блок, выход первого элемента И соединен со входом порогового злемен та через включенные последовательно коммутатор, блок управления, реверсивный счетчик, первый элемент задержки, формирователь команд, блок перезаписи и блок вычитания, второй вход реверсивного счетчика соединен с выходом первого элемента И, второй выход - со вторьм входом дешифоатора, третий выход - со вторым входом коммутатора, а первьй выход со вторым входом второго элемента И, выход которого через дешифратор подключен ко второму входу блока регистров, выход генератора импульсов соединен с третьим входом реверсивного счетчика, выход порогового элемента со вторым входом формирователя команд, первый выход блока управления подклю- чен ко входу второго элемента задеожки, а второйвыход ко второму входу первого элемента И. Кроме того, блок переписи содержит мультиплексоры, первые входы которых подключены к выходам первых регист- . ров, вторые входы - ко второму входу блока, а выходы - к выходу блока, выходы первых мультиплексоров соединены с первыми входами первых регистров, вторые входы которых подключены к первому входу блока, а второй регистр выходом соединен, с третьим входом второго мультиплексора. На фиг. 1 представлен структурная схема устройства; на фиг. 2 структурная схема блока перезаписи значений контролируемых параметров. Устройство содержит первый элемент И 1, коммутатор 2, блок 3 управления, реверсивный счетчик 4, первый, второй и третий элементы 5,6 и 7 задержки, второй элемент И 8, генератор 9 импульсов, дешифратор 10, формирователь 11 команд, блок 12 перезаписи, блок 13 вычитания, пороговый блок 14, первые регистры 15, первые мультиплексоры 16, второй регистр. 17, второй мультиплексор 18. . Устройство работает следующим образом. .В исходном состоянии комммутатор 2и реверсивный счетчик 4 находятся в. нулевых состояниях. Сигнал с первого выхода блока 3 управления, который соединен с первым входом реверсивного счетчика 4,устанавливает реверсивный счетчик 4 в режим слежения и через элементы 6 и 7 задержки прикладываясь к первому входу элемента ИЗ, закрывает его. На втором выходе блока 3управления присутствует потенциал логической единицы, который прикладываясь ко второму входу элемента И 1, -подготавливает его к срабатыванию. На первом выходе реверсивного счетчика 4 сигнал отсутствует и, как следствие этого, отсутствует сигнал на выходелогического блока 11. На

84 управляющем выходе дечтфратора 10 сигнала нет, так как элемент И 8, с которым он соединен, закрыт. Первую запись информации в устройство производит оператор, поэтому эта информация считается достоверной. Он же вводит в блок 3 управления ив пороговь й блок 14 значения: числаконтролируемых значений параметра N и величину порога 6 (на фиг 1 и фиг,2 цепи записи информации и ввода ее не показаны. Работа устройства начинается с момента коммутации входа устройства. Импульсы наличия информации на входе устройства поступают на первый вход элемента И 1 и с выхода его поступают на вход коммутатора 2 к па второй вход реверсивного счетчика 4, При подсчете коммутатором N импульсов на втором выходе блока 3 управления устанавливается потенциал логического нуля, который приклйдываясь ко второму входу элемента И 1 вызывает закрывание-его. Импульсы наличия информации на ходе устройства перестают поступать на вход коммутатора 2, Одновременно с появлением нулевого потенциала на втором выходе блока 3 на его первом выходе появляется сигнал, который свидетельствуетО том,, что в блок 12 перезаписи записано N значений параметра. Этот сигнал,прикладываясь к первому входу реверсивнрго счетчика 4, вызывает переключение его в режим вычитания И через элемент 6 задержки запускает генератор 9, а через элемент 7 задержки подготавливает элемент И 8 к срабатыванию. Первым импульсом с генератора 9, которьгй прикладывается к третьему входу реверсивного счетчика 4, реверсивньш счетчик 4 передает (N-l)--oe состояние и на первом выходе появляется сигнал свидетельствующий о том, что реверсивный счетчик 4 перешел в (N-l)-oe состояние. Этот сигнал открываетвторой элемент И 8 и через первый элемент 5 задержки поступает на первый вход формирователя 11 команд.Открываясь,элемент ИЗ своим сигналом с выхода разрешает считывание информации с первого выхода реверсивного счетчика 4 на второй вход дешифратора 10. Дешифратор 10 дешифрируя (N-l)-oe состояние реверсивного счетчика 4 выдает со своего выхода сигнал, который прикладываясь ко второму входу блока 12

8

перезаписи, выбывает срабатывание мультиплексоров 16 и, как следствие этбго, считывание на его управляющий выход - 1-го и 2-го значений параметра С управляющего выхода блока 12 перезаписи 1-ое и 2-ое значения параметра подаютсяна вход блока 13 вычитания, на выходе которого образуется абсолютная величина разности между 1-ым и 2-ым значениями параметра, которая подается на вход порогового блока 14, Если получившаяся разность больше порога g , то на выходе порогового блока 14 появляется сигнал, который прикладываясь ко второму входу формирователя 11 команд вызывает появление, сигнала на его выходе, который воздействуя на первый вход блка 12 перезаписи попадает на первый вход первого регистра 15 записи, что вызывает перезапись содержимого 2-ого регистра 15 записи в 1-ый регистр) 15 записи.

Таким образом, ошибочное 2-ое значение параметра заменяется достоверным 1-ым значением; Если получившаяся разность меньше порога или равна ему, то на выходе порогового блока 14 сигнала не будет и, как следствие этого, перезаписи не будет. Все вышеописанные процессы в устройстве протекают в течение одного такта работы генератора 9, N -ым импульсом с генератора 9 реверсивный сетчик 4 перейдет в нулевое состояние и на третьем выходе появляется импульс, который прикладываясь ко входу установки в нулевое состояние коммутатора 2 переводит коммутатор 2 нулевое состояние и тем самым устройство возвращается в исходное состояние.

Технические преимущества предложенного устройства заключаются в расширении функциональных возможностей известного устройства, т.е. повьш1ении быстродействия при обработке контролируемых параметров, выигрыш.которого можно оценить следующим коэффициентом

N-t,,Tp N(t3+tT-)

где N - число значений контролируемого параметра; TQ- время ручной обработки; t - время записи одного зна.чения параметра; fc-f - период следования тактовых импульсов. Так при значениях N 100-, t 10 сек} Тр 1 сек-, t , значение коэффициента Kg- равно ) т. е. быстродействие увеличивает.ся в десять паз. Формула изобретения 1. Устройство для контроля параметров, содержащее блок регистров первьй элемент задержки, первый эл мент И, подключенный первым входом к входу устройства,второй элемент заде ки, соединенный выходом со входом ген ратора импульсов и через третий эле- мент задержки с первым входом второг элемента И, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены коммутатор-, дешйфратор , реверсивный счетчик, формирователь команд, блок управления, блок вычитания и пороговый блок, выход первого элемента И соединен со входом порогового элемен та через включенные последовательно коммутатор, блок управления, реверси ный счетчик, первый элемент задержки формирователь команд, блок перезаписи и блок вычитания, и выход пер1. ° вого элемента И подключен ко второму входу реверсивного счетчика, соединен с вьпсодом первого элемента И, второй выход - со вторым входом дешифратора, третий выход - со вторым входом коммутатора, а первый выход - со вторым входом второго элемента И, выход которого через дешифратор подключен ко второму входу блока регистров, выход генератора импульсов соединен с третьим входом реверсивного счетчика, выход порогового элемента - со вторым входом формирователя команд, первый выход блока управления подключен ко входу второго элемента задержки, а второй выход - ко.второму входу.первого элемента И, 2. Устройство по п. 1, о т л ичающееся тем, что, блок переписи содержит мультиплексоры,первые входы которых подключены к выходам первых регистров, вторые входы -око второму входу блока, а выходы - к выходу блока, выходы первых мультиплексоров соединены с первыми входами первых регистров, вторые входы которых подключены к первому входу блока, а второй регистр выходом соединен с третьим входом второго мультиплексора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство. СССР № 525083, кл. Gj 06 F 7/00, 1976. 2.Авторское свидетельство СССР № 534762, кл. Q 06 F 7/00, 1977. 3.Авторское свидетельство СССР по заявке 2587969/18-24, кл. G 06 Г : 15/36, 1978(прототип) .

Авторы

Даты

1981-06-30—Публикация

1979-08-16—Подача