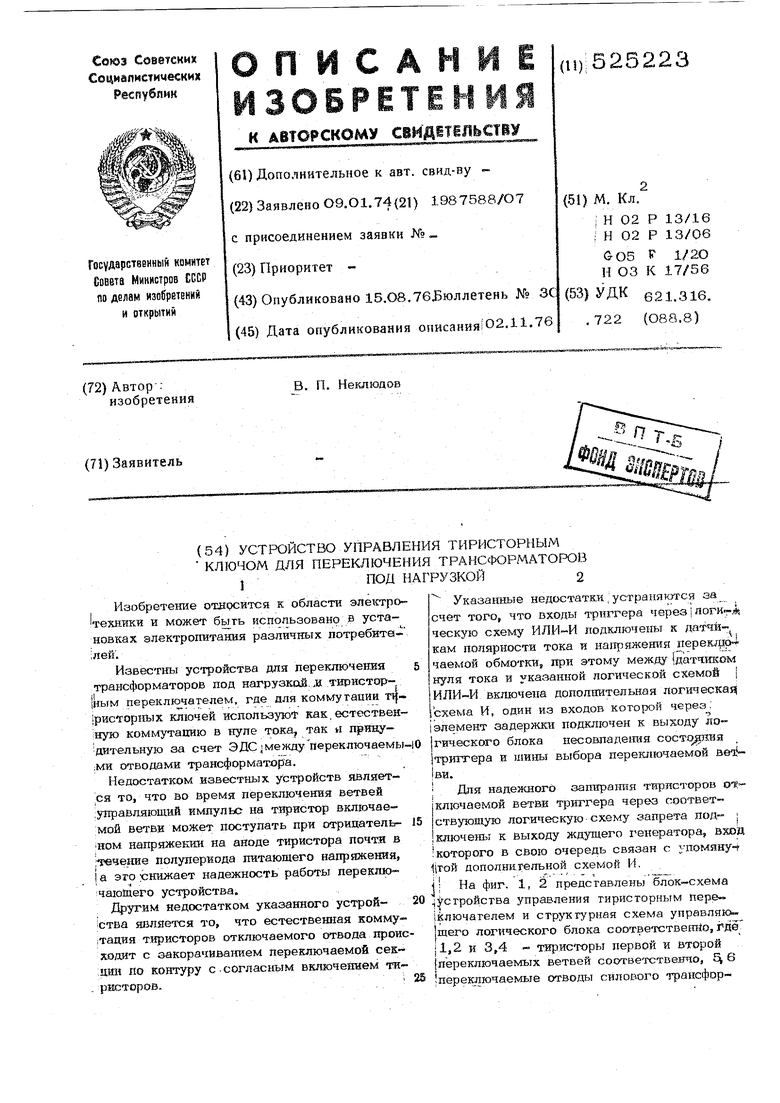

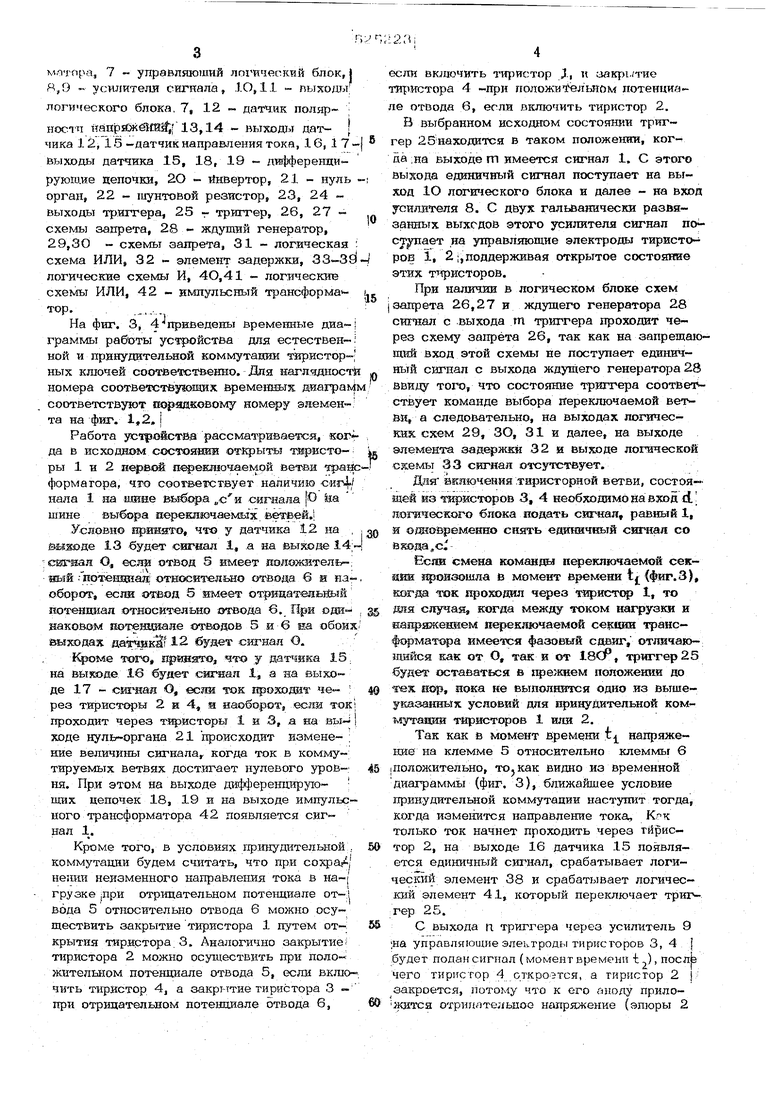

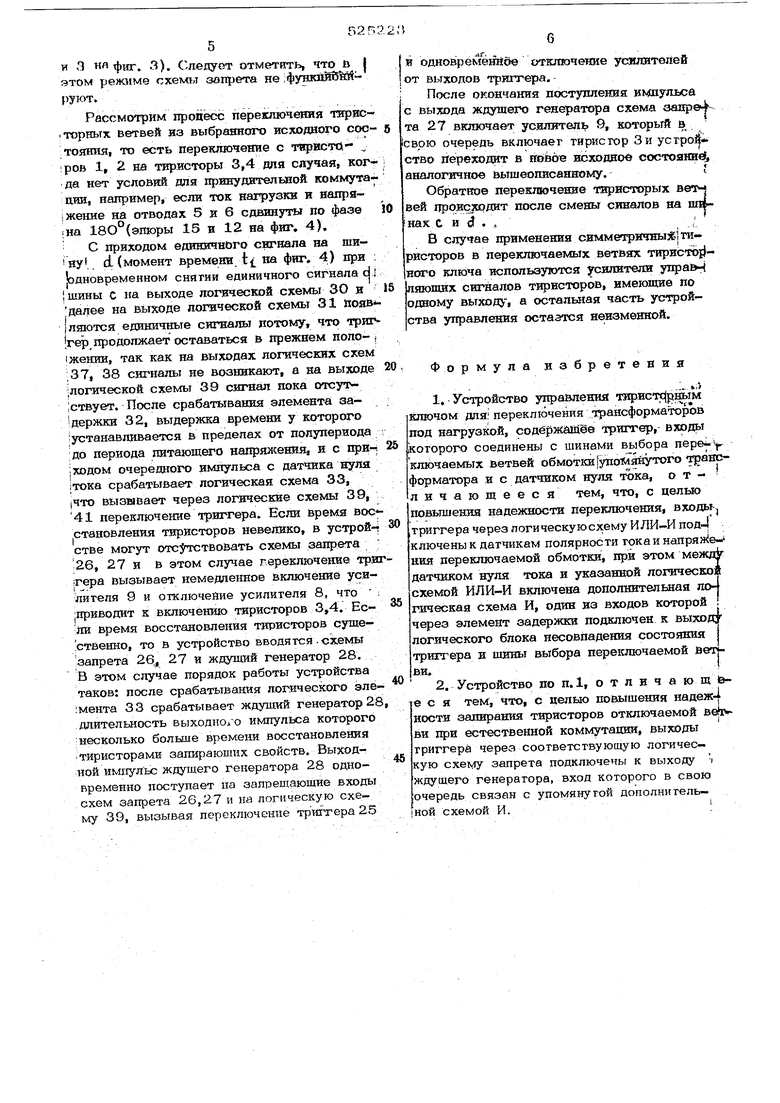

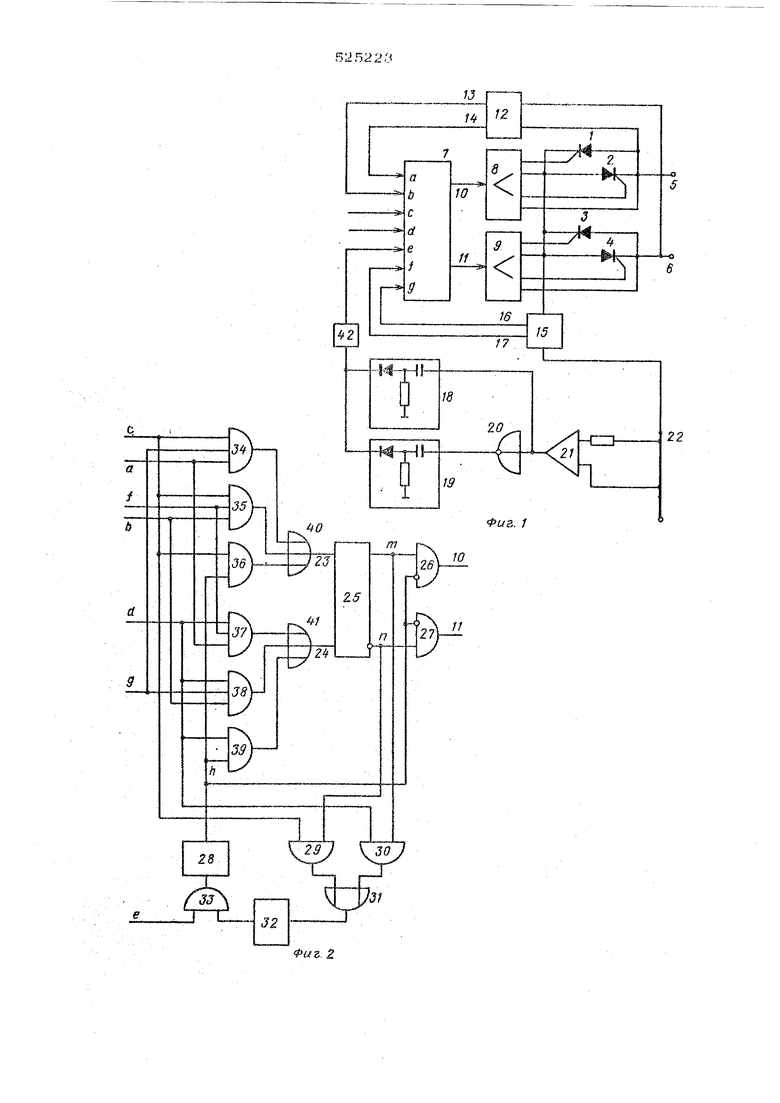

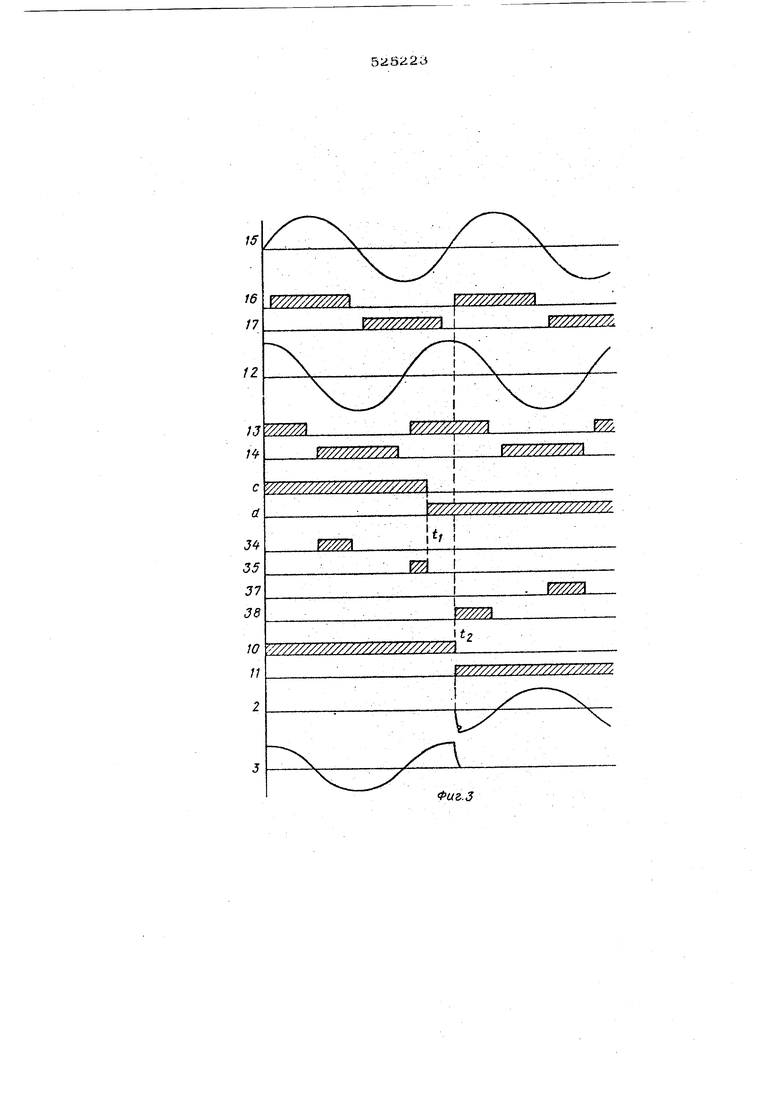

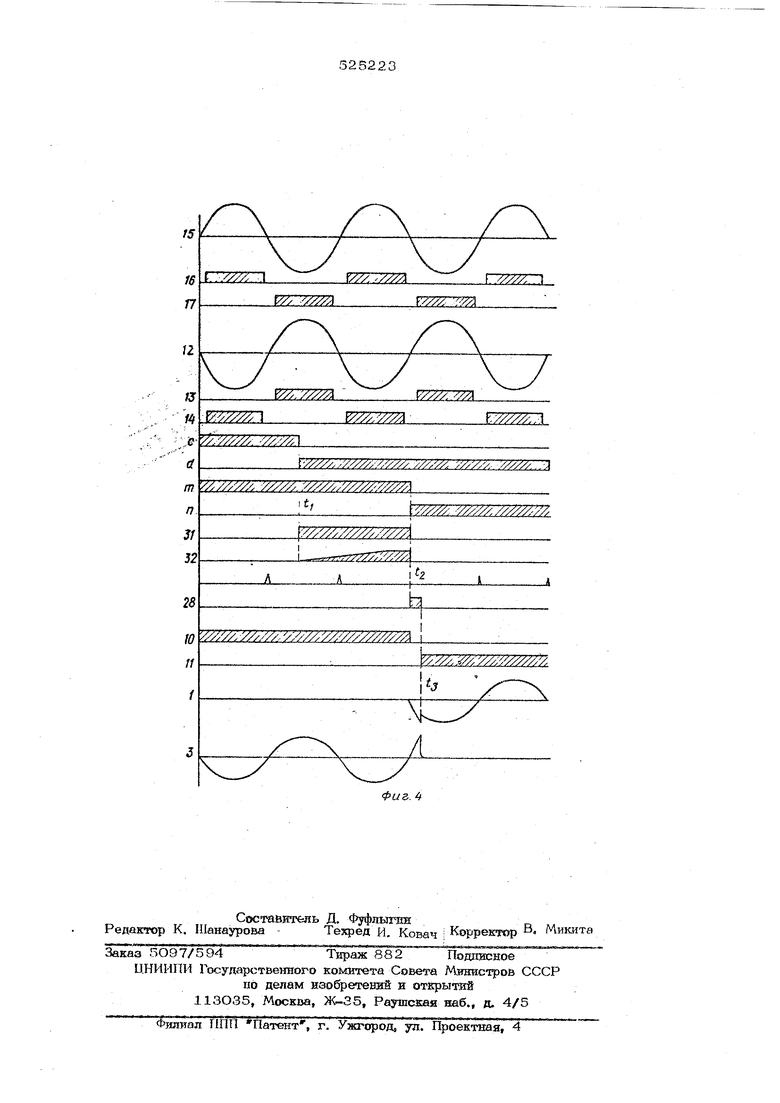

мотора, 7 - управляющий лохическвй блок, | М,9 - уоиштели сигнала, J.0,11 - выходы; логического блока. 7, 12 - датчик поляр- ностп Hanpscs 6tta,13,14 - выходаг датчика 12, 15 -датчик направления тока, 16, 1 7- выходы датчика 15, 18, 19 дифференцируюш.ие цепочки, 2О - инвертор, 21 - нуль орган, 22 - шунтовой резистор, 23, 24 выходы триггера, 25 - триггер, 26, 27 схемы запрета, 28 - ждущий генератор, 29,ЗО - схемы запрета, 31 - логическая : схема ИЛИ, 32 - элемент задержки, логические схемы И, 4О,41 - логические схемы ИЛИ, 42 - импульсный трансформа тор. . .,, На фиг. 3j 4 приведены временные диа-I граммы работы устройства для естествен™. ной и принудительной коммутании тиристор-; ных ключей соответст&енно. Для наглядности номера соответстврощих &реме1Шык диаграйм соответствуют норяяковому номеру эяемен-; та на ф.иг. 1,2, j Работа усчройстаа рассматриваемся, в исходном состоянии открыты тиристоры 1 и 2 n BfflS переЕшочаемой бетви чраж форматора, что соогветствует наличию сигА/ нала 1 на .шиие выбора „си сигяагаа О ka шине выб1Мра а екижэчаемгых. ветвей.; Условно иринато, что у датчика 12 на , 13 будет снгнал 1, ,а на выходе 14;н Сигнал О, ес-Лй отвод 5 имеет йояожитель-; иый .нртен 31йая| относительно отвода 6 и на оборот, еспя отвод S имеет отрииатеяы& й иотеициал относительно отвода 6. При ода наково-М иотеяэдааие отводов 5 и 6 на обоих. выходах даетркЖ 12 будет сигнал О. 1%юме того, H|№(HssTO, что у йатчйяа 15. на )де, 16 будет сш:ч1ал 1., а на выходе 17 - сигнал О, есгш проходит че- рез тиристоры 2 и 4, и наоборот, есгш ток) проходит через тиристоры 1 и .3, а на вы- j ходе нуль-органа 21 происходит измене- ; ние величины сигнала когда ток в коммутируемых ветвях достигает нулевого уровня. При этом на выходе дифференцирующих цепочек 18, 19 и на выходе импульсного трансформатора 42 появляется сигнал 1. Кроме того, в условиях принудительной:, коммутации будем считать, что при cospai неиии неизменного направления тока в на-/ грузке рри отрицательном потенциале от-; вода 5 относительно отвода 6 можно осуществить закрытие тиристора 1 путем от- крытия тиристора 3. Аналогично закрытие; тиристора 2 можно осуществить при поло-жительном потенциале отвода 5, если BKHIO-. чить тиристор 4j а закрт-ттие тиристора 3 при отрицательном потенциале отвода 6, если вюцочить тиристор JI., и зак|)ь/тие тЩКстора 4 -при положительном потенциае отвода 6, если включить тиристор 2. В выбранном ИСХОД1ЮМ состоянии триггер 25находится в таком положении, когда ;иа выходе m имеется сигнал 1. С этого выхода единичный сигнал поступает на выход 1О логшсеского блока и далее - на вход усилителя 8. С двух гальванически развязакных выходов этого усилителя сигнал по сужает на управляющие электроды тиристо ров i, 2;,поддерживая открытое состояние этих тфисторов. При наличии в логическом блоке схем запрета 26,27 и ждущего генератора 28 сигнал с выхода m триггера проходит через схему занрёта 26, так как на запрещающий вход этой схемы не поступает единичный сигнал с выхода ждутдего генератора 28 ввиду TOiX), что состояние тркггера соответ ствует команде выбора переключаемой вет- аи, а следовательно, на выходах погическиэс схем 29, ЗО, 31 и далее, на выходе элемента 32 и выходе логической сжемтэт 33 сигнал отсутствует. Дая включения .тиристорной ветви, состоя- шей из тяристоров 3, 4 необходимо на вход d пюгкческого блока додать сигнал, равный 1, 5 одао&|эе1 4енно егданнчкый сигнал со ,с ЕСЛИ смена команды переключаемой сека ш произошла е момент времени tj (фиг.З), квгда ток ярокодал через Т1ф:истс 1, то тз. случая, когда между током нагрузки и капряжением яерекяючаемой серийи тфансформатх эа имеется фазовый сдвиг, отличающийся как от О, так и от 18СР, триггер 2 5 будет оставаться в положении до в&р, пока не выподнвтся одно из вышеуйлза шнх усяовий для принудительной коммуташш тиристоров 1 или 2. Так как в момент времени t напряжение на клемме 5 относительно клеммы 6 (Положительно, тоjкак видно из временной диаграммы (фиг. 3), ближайшее условие принудительной коммутании наступит тогда, когда изме1тется направление тока, Кгк только ток начнет проходить через тиристор 2, на выходе 16 датчика 15 появляется единичный сигнал, срабатывает логический элемент 38 и срабатывает логичес1Шй элемент 41, который переключает триггер 25. С выхода п триггера через усилитель 9 ;на управляющие электроды тиристоров 3, 4 | .будет подан сигнал (момент времени t ), после чего тиристор 4 откроется, а тиристор 2 | закроется, потому что к его аноду прило кится отритгятельное напряжение (эпюры 2 и 3 ня фиг, 3), Следует отметить, что в | этом режиме схек«,1 запрета не ;фушшЙЙШ ). Рассмотрим процесс переключения тиряс1 торных ветвей из выбранного исходаого сое тояшШ| то есть переключение с тнршзто- , ipoB 1, 2 на тиристоры 3,4 для случая, ког да нет условий для принудительной коммута аии, например, есяи ток нагрузки и напряI женке на отводах 5 и 6 сдвинуты iio фазе 1на 18О°(эшоры 15 и 12 на фиг, 4), С приходом единкчнЬго сигнала на ши- ну1 d (момент времени i: на фиг, 4) при рдновременном снятии единичного сигнала d 1шины с на выходе логической схемы 30 и далее на выходе логической схемы 31 йояв )ляются единичные сигналы потому, что триг |гер продолжает оставаться в прежнем поло 1жешш, так как на выходах логических схем ,37, 38 сигналы не возникают, а на выходе логической схемы 39 сигнал пока отсут :ствует. После срабатывания элемента1 аадержки 32, выдержка времени у которого ; устанавливается в пределах от попупериода до периода питающего напрялсения, и с при;ходом очередного импульса с датчика нуля 1тока срабатывает логическая схема 33, |Что вызывает через логические схемы 39, 41 переключение триггера. Если время вос становления тиристоров невелико, в устройстве могут отсутствовать схемы запрета ; 26, 27 и в этом случае переключение три ;гера вызывает немедленное включение усилителя 9 и отключейие усилителя 8, что :приводит к включению тиристоров 3,4, время восстановления тиристоров существенно, то в устройство вводятся-схемы запрета 26, 27 и ждзшшй генератор 28. В этом случае порядок работы устройства таков: после срабатывания логического эле:мента 33 срабатывает ждущий Генератор 28 длительность выходно о импульса которого несколько больше времени восстановления тиристорами запираюших свойств. Выходной импульс ждущего генератора 28 одновременно поступает па запрещающие входы схем запрета 26,27 и на логическую схему 39, вызывая переключение триггера 25 в одновременное отключение усшштепей от выходов триггера. После окончания поступления импульса с выхода ждущего генератора схема аапре4 та 27 включает усилителе 9, который в свою очередь включает тиристор Зи устрой ство п;ереходит в новбв всжэддое состояние, аналогичное вышеописанному. Обратное переключение тяристорых ветм вей пррвярхрдит после смены синалов на пшнак t ad.,; В случае применения симметричны тиристоров в переключаетиых ветвях тиристо1} наго ключа используются усилителя унравч ляюпшх сжналов Т1фисторов, имеющие по одному выходу, а остальная часть устройства управления остается неизменной. Формула избретения 1,Устройство управления гаристс(рй.1м ключом ДЛЯ) переключения трансформаторов под нагрузкой, содержащее триггер, входы которого соединены с шинами выбора nepei-y ключаемых ветвей обмотки упоМяйсутого транс форматора и с датчиком нуля тока, отличающееся тем, что, с целью повышения надежности переключения, входьь триггера через логическуюсхему И ЛИ-И под-j ключены к датчикам полярности токаинапрян ения переключаемой обмотки, при этом датчиком нуля тока и указанной логической схемой ИЛИ-И включена дополнительная ло4 гическая схема И, один из входов которой через элемент задержки подключен к выход; логического блока несовпадения состояния триггера и шины выбора переключаемой вет ви, 2.Устройство до п. 1, о т л и ч а ю щ feе с я тем. Что, с целью повышения надежкости запирания тиристоров отключаемой при естественной коммутации, выходы триггера через соответствующую логическую схему запрета подключены к выходу -j ждущего генератора, вход которого в свою очередь связан с упомянутой дополнительной схемой И.I

У//////////Щ

У///////////Л

//////////////////////

Ш/

/////////////y///

//7//////////J(

У//7///7//л

V////////////i

/

Ш.

У//////////Л

V///////////A

I

V/////////////////////7//Z////

r

I I

V////A

«2

У///////////////////////Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регулирования мощности конденсаторных батарей | 1987 |

|

SU1460754A1 |

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ В ДЕЙСТВИЕ ТРАМВАЙНОЙ СТРЕЛКИ С ПОЕЗДА | 2001 |

|

RU2191715C1 |

| Устройство для управления встречно-параллельно включенными тиристорами | 1979 |

|

SU884144A1 |

| Устройство для управления инвертором с @ резонансными нагрузками | 1986 |

|

SU1410242A1 |

| Устройство для управления тиристорным преобразователем | 1975 |

|

SU549873A1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

| Следящий электропривод | 1985 |

|

SU1259207A2 |

| Способ непрерывно-импульсного регулирования постоянного тока | 1988 |

|

SU1631528A1 |

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ СУШКИ ЗЕРНА | 2008 |

|

RU2395048C2 |

| Устройство для приведения в действие трамвайной стрелки с поезда | 2002 |

|

RU2224675C2 |

ХЯ

Л

Ig/. g-gj j

V//..7/7A

.;2ii21 L

V//,7/7/A

SL

-ESZL a.

- i222S2L

V/7/7/Z

/7////. 77///. 7/7/////////fZ- /y7A

/П

-f

J/

52

25

ZlZSZZZ SZ ZS iW //

. . 77/7/7//77/.

Авторы

Даты

1976-08-15—Публикация

1974-01-09—Подача