(54) УСТЮЙСТВО ДЛЯ УПРАВЛЕНИЯ ВСТРЕЧНО. ПАРАЛЛЕЛЬНО ВКЛЮЧЕННЫМИ ТИЙ1СТОРАМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Бесконтактный переключатель | 1979 |

|

SU834912A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ M-ФАЗНЫМ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2027294C1 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Устройство для управления тиристором | 1977 |

|

SU683020A1 |

| Устройство для управления встечно-параллельно включенными тиристорами | 1977 |

|

SU731523A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2320071C1 |

| Устройство для регулирования температуры | 1985 |

|

SU1260928A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для ограничения угла регулирования многозонного сетевого преобразователя | 1983 |

|

SU1128347A1 |

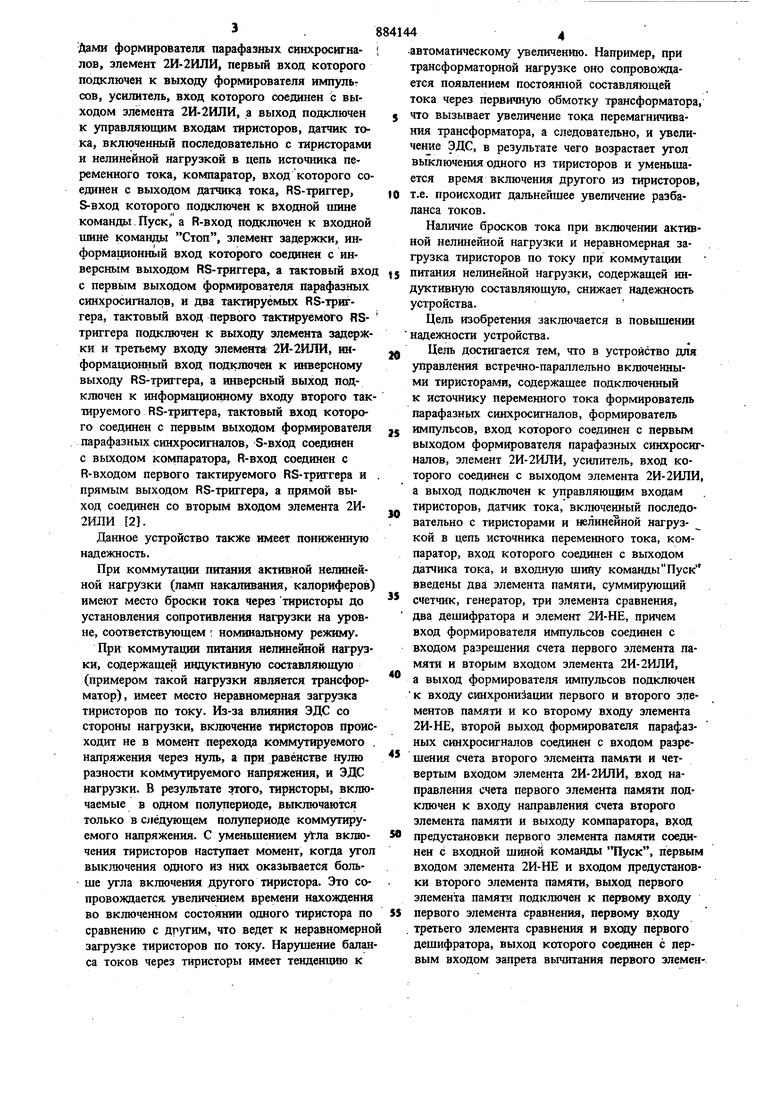

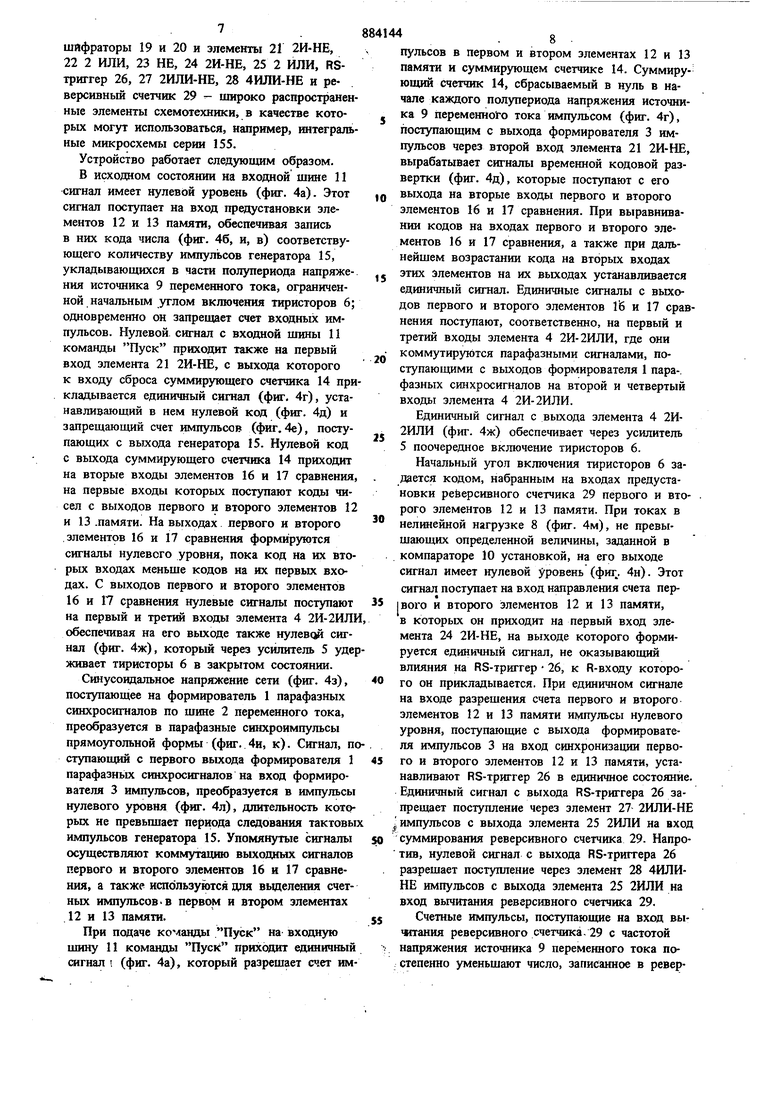

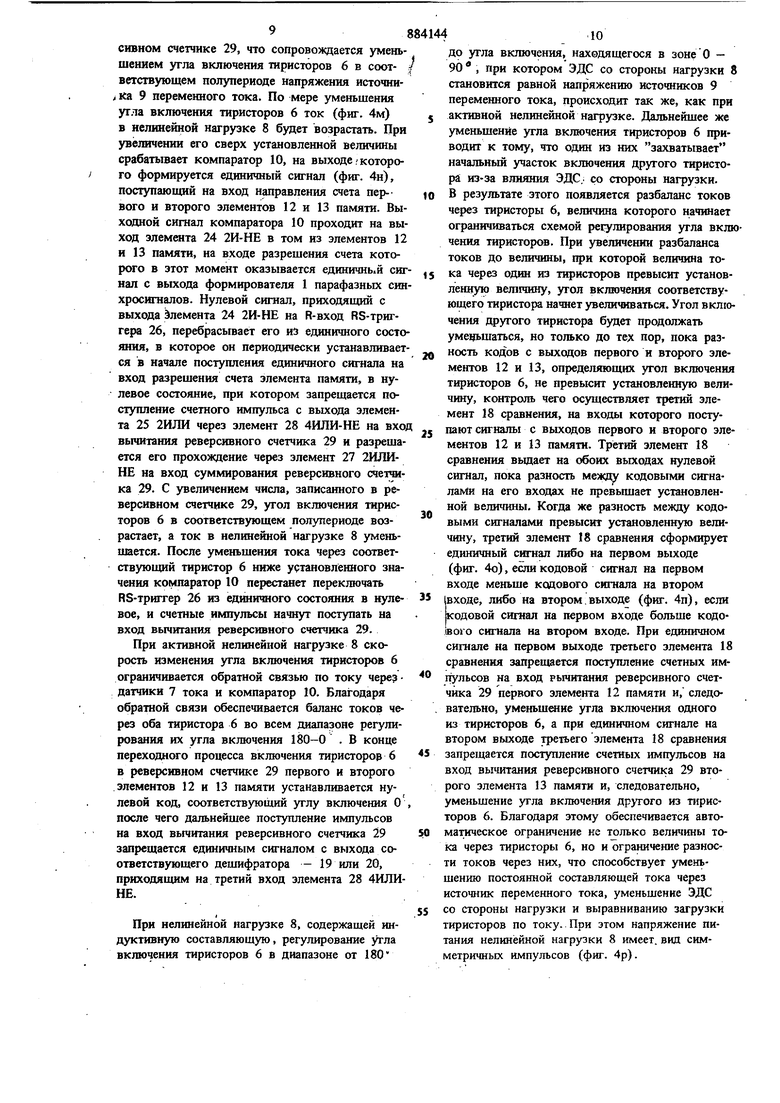

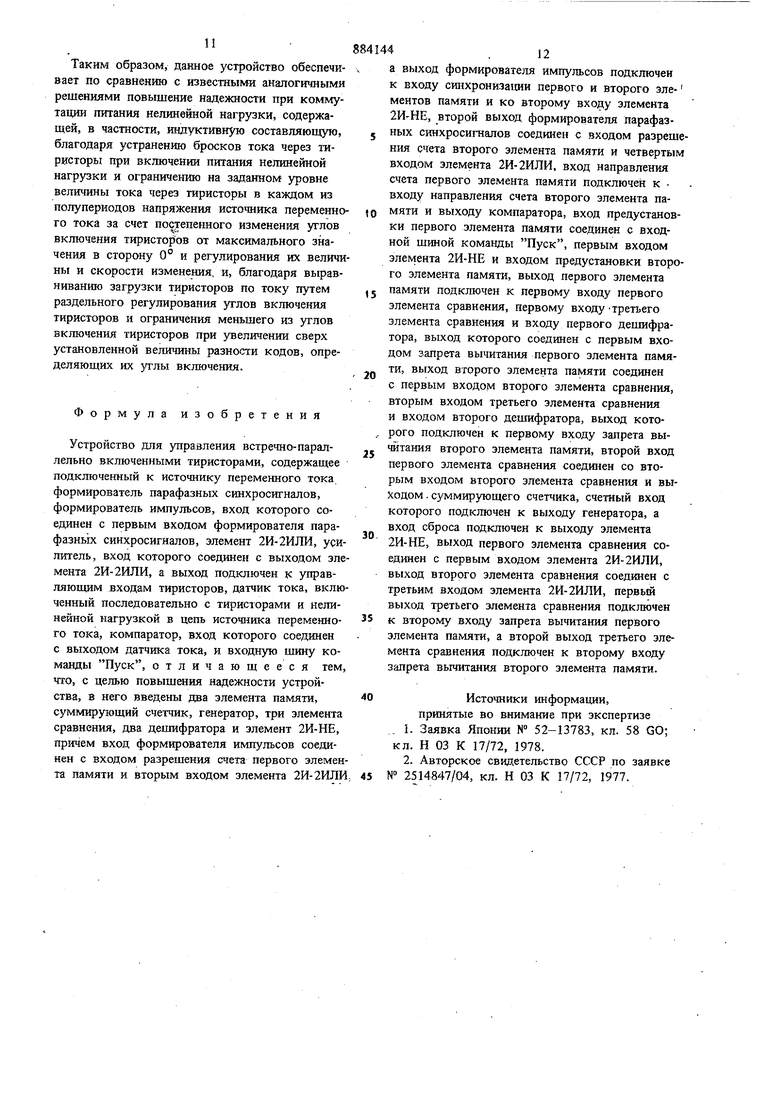

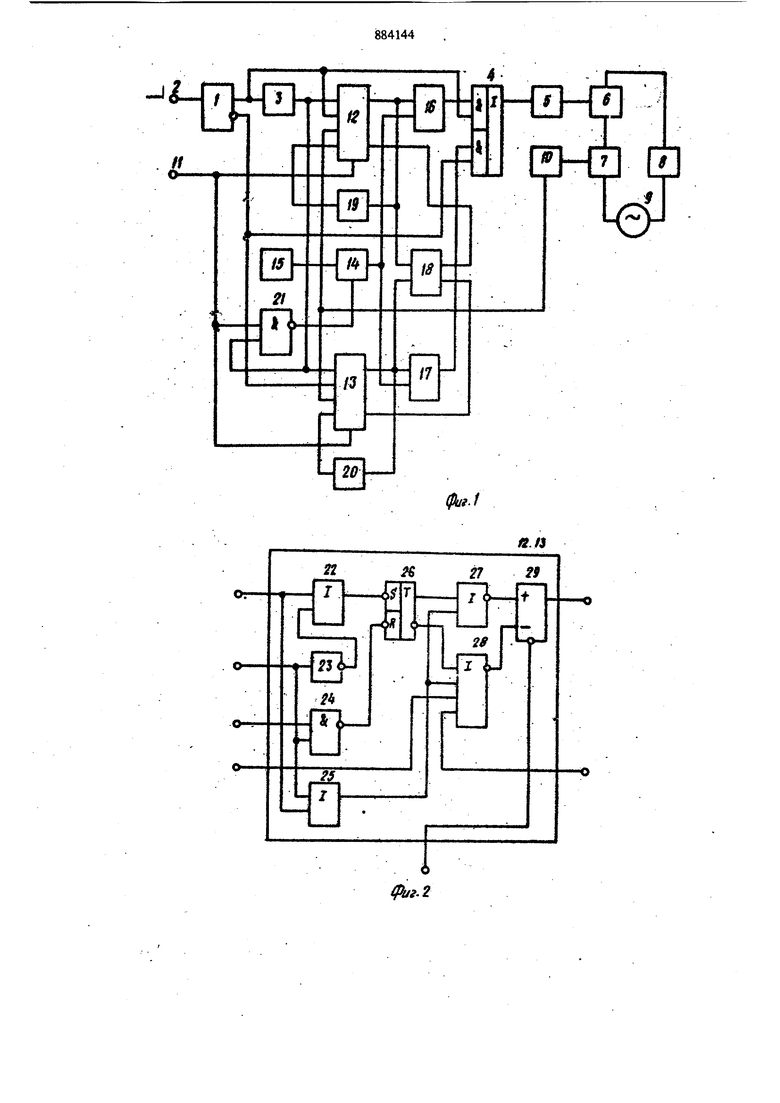

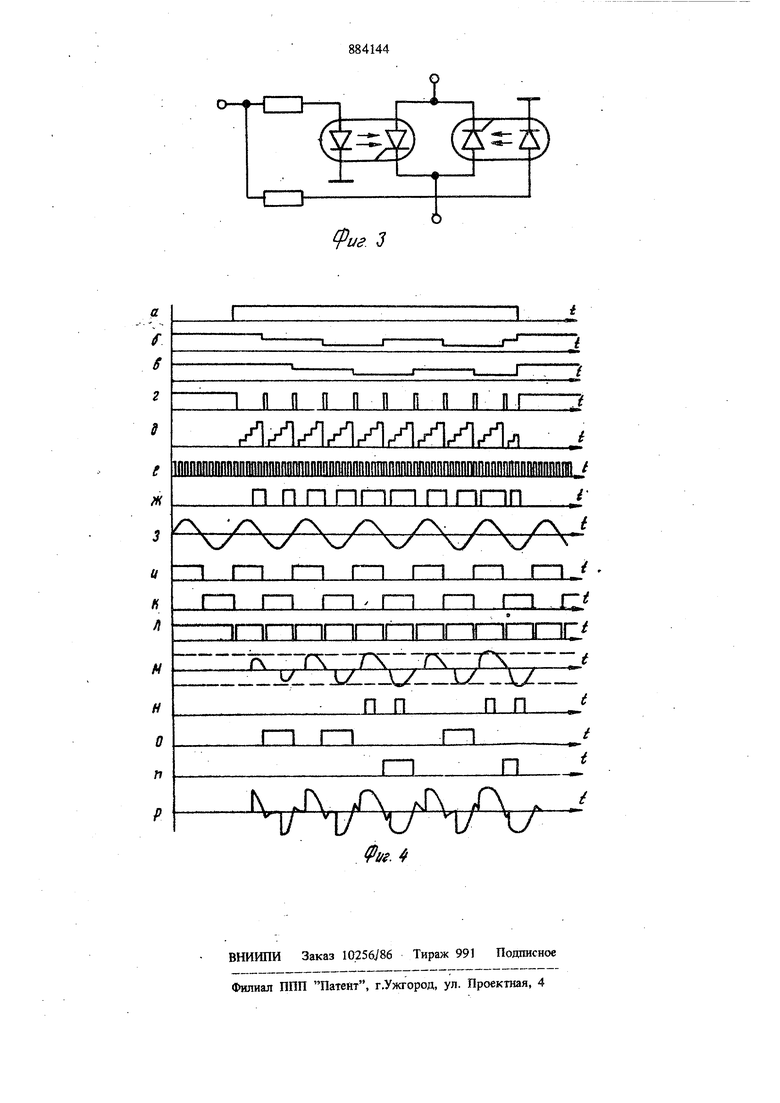

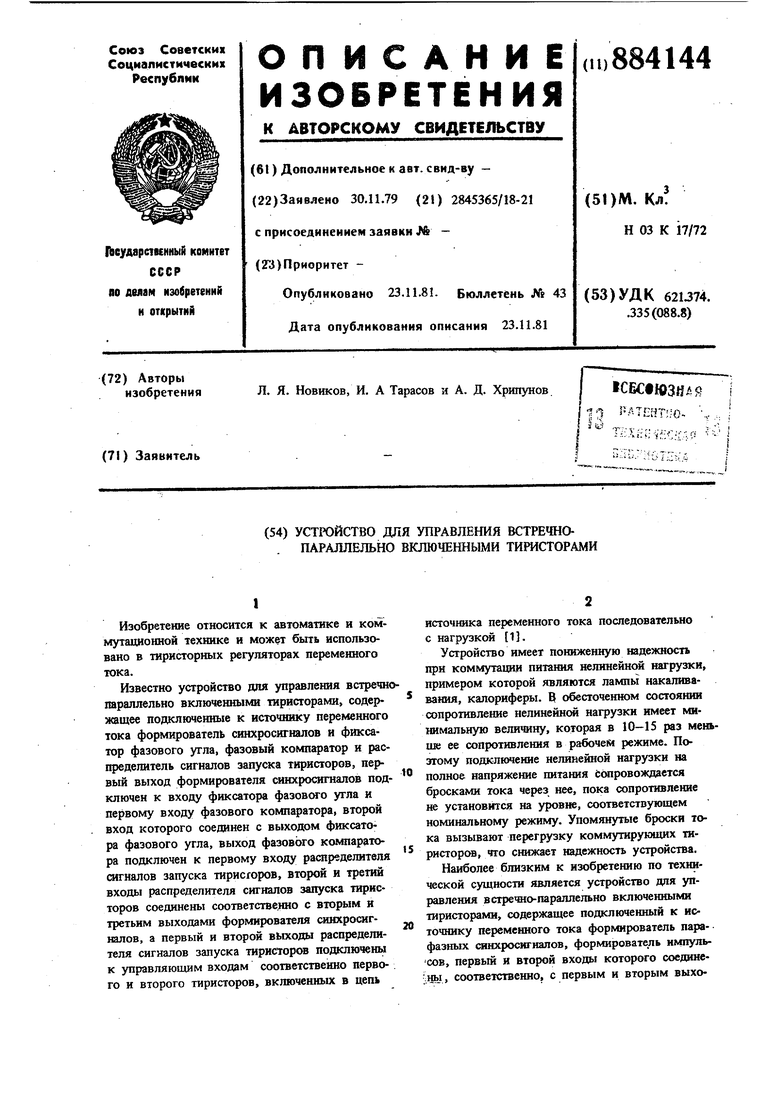

Изобретение относится к автоматике и коммутационной технике и может быть использовано в тирнсторных регуляторах переменного тока. Известно устройство цпя управления встречн траллельно включенными тиристорамн, содержащее подключенные к источнику переменного тока формирователь синхросигналов и фиксатор фазового угла, фазовый компаратор и распределитель сигналов запуска тиристоров, первый выход формирователя синхросигналов под ключен к входу фиксатора фазовся-о угла и первому входу фазового компаратора, второй вход которого соединен с выходом фиксатора фазового угла, выход фазового компаратора подключен к первому входу распределителя сигналов запуска тирисгоров, второй и третий входы распределителя сигналов запуска тиристоров соединены соответстве.нно с вторым и третьим выходами формирователя (жнхросигналов, а первый и второй вЬгходы распределителя сигналов запуска тиристоров подключены к управляющим входам соответственно первого и второго тиристоров, включенных в цепь источника переменного тока последовательно с нагрузкш 1. Устройство имеет пониженную надежность при коммутации питания нелинейной нагрузки, примером которой являются лампь накаливавания, калориферы. Q обесточенном состоянии сопротивление нелинейной нагрузкн имеет минимальную величину, которая в 10-15 раз меньше ее сопротивления в рабочем режиме. Позтому подключенне нелинейной нагрузки на полное напряжение питания сопровождается бросками тока через нее, пока сопротивление не установится на уровне, соответствующем номинальному режиму. Упомянутые броски тока вызывают перегрузку коммутирующих тиристоров, что снижает надежность устройства. Наиболее близким к изобретению по технической сущности является устройство для управления встречно-параллельно включенными тиристорами, содержащее подключенный к источнику переменного тока формирователь парафазных синхросигналов, формирователь импульсов, первый и второй входы которого соединеHbj, соответственно, с первым и вторым выхоДами формирователя парафазных синхросигналов, элемент 2И-2ИЛИ, первый вход которого подключен к выходу формирователя импульт сов, усилитель, вход которого соединен с выходом элемента 2И-2ИЛИ, а выход подключен к управляющим входам тиристоров, датчик тока, включенный последовательно с тиристорами и нелинейной нагрузкой в цепь источника переменного тока, компаратор, вход которого соединен с выходом датчика тока, RS-триггер, S-вход которого подключен к входной шине команды Пуск, а R-вход пощслючен к входной шине команды Стоп, элемент задержки, информационный вход которого соединен с ииверсным выходом RS-триггера, а тактовый вхо с первым выходом формирователя парафазных синхросигналов, и два тактируемых RS-триггера, тактовый вход первого тактируемого RSтриггера подключен к выходу элемента задержки и третьему входу элемента 2И-2ИЛИ, информационный вход подключен к инверсному выходу RS-триггера, а инверсный выход подключен к информационному входу второго так шруемого RS-трштера, тактовый вход которого соединен с первым выходом формирователя парафазных синхросигналов, S-вход соединен с выходом компаратора, R-вход соединен с R-вход ом первого тактируемого RS-триггера и прямым выходом RS-триггера, а прямой выход соединен со вторым входом элемента 2И2ИЛИ 2. Данное устройство также имеет пониженную надежность. При коммутации питания активной нелинейной нагрузки (ламп накаливания, калориферов) имеют место броски тока через тиристоры до установления сопротивления нагрузки на уровне, соответствующем : номинальному режиму. При коммутации питания нелинейной нагрузки, содержащей индуктивную составляющую (примером такой нагрузки является трансформатор), имеет место неравномерная загрузка тиристоров по току. Из-за влияния ЭДС со стороны нагрузки, включение тиристоров проис ходит не в момент перехода коммутируемого напряжения через нуль, а при равенстве нулю разности коммутируемого напряжения, и ЭДС нагрузки. В результате этого, тиристоры, вклю чаемые в одном полупериоде, выключаются только в следующем полупериоде коммутируемого напряжения. С уменьшением ytna включения тиристоров наступает момент, когда угол выключения одного из них оказывается больше угла включения другого тНристора. Это сопровождается увеличением времени нахождения во включенном состоянии одного тиристора по сравнению с другим, что ведет к неравномерно загрузке тиристоров по току. Нарушение балан са токов через тиристоры имеет тенденцию к 4 автоматическому увеличению. Например, при трансформаторной нагрузке оно сопровождается появлением постоянной составляющей тока через первичную обмотку трансформатора, что вызывает увеличение тока перемагничивания трансформатора, а следовательно, и увеличен ие ЭДС, в результате чего возрастает угол выключения одного из тиристоров и уменьшается время включения другого из тиристоров, т.е. происходит дальнейшее увеличение разбаланса токов. Наличие бросков тока при включении активной нелинейной нагрузки и неравномерная загрузка тиристоров по току при коммутации питания нелинейной нагрузки, содержащей индуктивную составляющую, снижает надежность устройства. Цель изобретения заключается в повышении надежности устройства. Цель достигается тем, что в устройство для управления встречно-параллельно включенными тиристорами, содержащее подключенный к источнику переменного тока формирователь парафазных синхросигналов, формирователь импульсов, вход которого соединен с первым выходом формирователя парафазных синхросигналов, элемент 2И-2ИЛИ, усилитель, вход которого соединен с выходом элемента 2И-2ИЛИ, а выход подключен к управляющим входам тиристоров, датчик тока, включенный последовательно с тиристорами и жлинейной нагрузкой в цепь источника переменного тока, компаратор, вход которого соединен с выходом датчика тока, и входную шияу команды Пуск введены два элемента памяти, суммирующий счетчик, генератор, три элемента сравнения, два дешифратора и элемент 2И-НЕ, причем вход формирователя импульсов соединен с входом разрешения счета первого элемента памяти и вторым входом элемента 2И-2ИЛИ, а выход формирователя импульсов подключен к входу синхронизации первого и второго элементов памяти и ко второму входу элемента 2И-НЕ, второй выход формирователя парафазных синхросигналов соединен с входом разрешения счета второго элемента памяти и четвертым входом элемента 2И-2ИЛИ, вход направления счета первого элемента памяти подключен к входу направления счета второго злемента памяти и выходу компаратора, вход предустановки первого элемента памяти соединен с входной шиной команды Пуск, первым входом злемента 2И-НЕ и входом предустановки второго злемента памяти, выход первого элемента памяти подключен к первому входу первого элемента сравнения, первому входу третьего элемента сравнения и входу первого дешифратора, выход которого соединен с первым входом запрета вычитания первого злемен5та памяти, выход второго элемента памяпГ соединен с первым входом второго элемента сравнения, вторым входом третьего элемента сравнения и входом второго дешифратора, выход которого подключен к первому входу запрета вычитания второго элемента памяти, второй вход первого элемента сравнения соединен со вторым входом второго элемента сравнения и выходом суммирующего счетчика, счетный вход которого подключен к выходу генератора, а вход сброса подключен к выходу элемента 2И-НЕ, выход первого элемента сравнения соединен с первым входом элемента 2И-2ИЛИ, выход второго элемента сравнения соединен с третьим входом элемента 2И-2ИЛИ, первый выход третьего элемента сравнения подключен к второму входу запрета вычитания первого элемента памяти, а второй выход третьего элемента сравнения подключен к второму входу эапрета вычитания второго элемента памяти. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - пример структурной схемы элемента памяти; на фиг. 3 - пример принципиальной схемы тиристорного коммутато ра, а на фиг. 4 - диаграммы, поясняющие работу устройства. Устройство (фиг. 1) содержит формирователь 1 парафаэных синхросигналов, выход кото рого соединен с щиной 2 переме{-шого тока, формирователь 3 импульсов, вход icoToporo соединен с первым выходом формирователя 1 парафазных синхросигналов, элемент 4 2И-2ИЛИ, усилитель 5, вход которого соединен с выходом элемента 4 2Й-2ИЛИ, а выход подключен к управляющим входам тиристоров 6, датчик 7 TOKaj включенный последовательно с тиристорами 6 и нелинейной нагрузкой 8 в цепь источника 9 переменного тока, компаратор 10, вход которого соединен с выходом датчика 7 тока, входную шину 11 команды Пуск, первый элемент 12 памяти и второй элемент 13 памяти, суммирующий счетчик 14, генератор 15, пер вый элемент 16 сравнения, второй элемент 17 сравнения, третий элемент 18 сравнения, первый дешифратор 19, второй дешифратор 20 и элемент 21 2И-НЕ. Вход формирователя 3 импульсов соединен с входом разрешения счета первого элемента 12 памяти и вторым входом элемента 4 2И-2ИЛИ, а выход формирователя 3 импульсов подключен к входу синхронизации первого 12 и второго 13 элементов памяти и ко второму входу элемента 21 2И-НЕ, второй выход формирователя 1 парафазных синхросигналов соединен с входом разрешения счета второго элемента 13 памяти и с четвертым входом элемента 4 2И-2ИЛИ, вход направления счета первого элемента 12 памяти подклю чен к входу направления счета второго элемента 13 памяти и к выходу компаратора 10, вход предустановки первого элемента 12 памяти соединен с входной шиной 11 команды Пуск, первым входом элемента 21 2И-НЕ и входом предустановки второго элемента 13 памяти, выход первого элемента 12 памяти подключен к первому входу первого элемента 16 сравнения, первому входу третьего элемента 18 сравнения и входу первого дешифратора 19, выход которого соединен с первым входом запрета вычитания первого элемента 12 памяти, выход второго элемента 13 памяти соединен с первым входом второго элемента 17 сравнения, вторым вводом третьего элемента 18 сравнения и входом второго дешифратора 20, выход которого подключен к первому входу запрета вычитания второго элемента 13 памяти, второй вход первого элемента 16 сравнения соединен со вторым входом второго элемента 17 сравнения и выходом суммирующего счетчика 14, счетный вход которого подключен к выходу генератора 15, а вход подключен к выходу элемента 21 2И-НЕ выход первого элемента 16 сравнения соедш1ен с первым входом элемента 4 2И-2ИЛИ, выход второго элемента 17 сравнения соединен с третьим входом элемента 4 2И-2ИЛИ, первый выход третьего элемента 18 сравнения подключен к второму входу запрета вычитания первого элемента 12 памяти, а второй выход третьего элемента 18 сравнения подключен к второму входу запрета вычитания второго элемента 13 памяти. Формирователь 1 парафазных синхросигналов может быть выполнен на базе дифференциального усилителя, а формирователь 3 импульсов на основе ждущего мультивибратора с логической схемой на входе, обеспечивающей его запуск при каждом переходе синусоидального напряжения через нуль. Элемент 4 2И-2ИЛИ - широко распространенная логическая схема. Усилжель 5 - стандартный операционный усилитель с согласующим транзисторным каскадом на выходе. Тиристоры 6 в оптронном варианте могут быть включены по .схеме, представленной на фиг. 3. В качестве датчика 7 тока может использоваться трансформатор тока с согласующим резистором и выпрямителем на выходе. Компаратор 10 может быть построен на основе стандартного операционного усилителя. Один из вариантов структурной схемы элементов 12 и 13 памяти приведен на фиг. 2, содержащий элемент 22 2ИЛИ, элемент 23 НЕ, элемент 24 2И-НЕ, элемент 25 2ИЛИ, ЯЗ-триггер 26, элемент 27 2ИЛИ-НЕ, элемент 28 4 ИЛИ-НЕ и реверсивный счетчик 29. Суммирующий счетчик 14 и генератор 15 - широко распространенные элементы схемотехники. Элементы 16, 17 и 18 сравнения могут бы1ъ выполнены на базе многоразрядных сумматоров. ДеШифраторы 19 и 20 и элементы 21 2И-НЕ, 22 2 ИЛИ, 23 НЕ, 24 2И-НЕ, 25 2 ИЛИ, RSтриггер 26, 27 2ИЛИ-НЕ, 28 4ШШ-НЕ и реверсивный счетчик 29 широко распространенные элементы схемотехники, в качестве которых могут использоваться, например, интегральные микросхемы серии 155. Устройство работает следующим образом. В исходном состоянии на входной шине 11 сигнал имеет нулевой уровень (фиг. 4а). Этот сигнал поступает на вход предустановки элементов 12 и 13 памяти, обеспечивая запись в них кода числа (фиг. 46, и, в) соответствующего количеству импульсов генератора 15, укладывающихся в части полупериода напряжения источника 9 переменного тока, ограниченной начальным углом включения тиристоров 6; одновременно он запрещает счет входных импульсов. Нулевой сигнал с входной шины 11 команды Пуск приходит также на первый вход элемента 21 2И-НЕ, с выхода которого к входу сброса суммирующего счетчика 14 при кладывается единичный сигнал (фиг, 4г), устанавливающий в нем нулевой код (фиг. 4д) и запрещающий счет импульсов (фиг. 4е), поступающих с выхода генератора 15. Нулевой код с выхода суммирующего счетчика 14 приходит на вторые входы элементов 16 и 17 сравнения, на первые входы которых поступают коды чисел с выходов первого и второго элементов 12 и 13 .памяти. На выходах первого и второго элементов 16 и 17 сравнения формируются сигналы нулевого уровня, пока код на их вторых входах меньше кодов на их первых входах. С выходов первого и второго элементов 16 и 17 сравнения нулевые сигналы поступают на первый и третий входы элемента 4 2И-2ИЛИ обеспечивая на его выходе также нулевф сигнал (фиг. 4ж), который через усилитель 5 удер живает тиристоры 6 в закрытом состоянии. Синусоидальное напряжение сети (фиг. 4з), поступающее на формирователь 1 парафазных синхросигналов по шине 2 переменного тока, преобразуется в парафазные синхроимпульсы прямоугольной формы (фиг. 4и, к). Сигнал, п ступающий с первого выхода формирователя 1 парафазньк синхросигналов на вход формирователя 3 импульсов, преобразуется в импульсы нулевого уровня (фиг. 4л), длительность которых не превьппает периода следования тактовы импульсов генератора 15. Упомянутые сигналы осуществляют коммутацию выходных сигналов первого и второго элементов 16 и 17 сравнения, а также используются для вьщеления счетных импульсов-в первом и втором элементах 12 и 13 памяти. При подаче команды Пуск на входную шину 11 команды Пуск приходит единичный сигнал 1 (фиг. 4а), который разрешает счет им g пульсов в первом и втором элементах 12 и 13 памяти и суммирующем счетчике 14. Суммирующий счетчик 14, сбрасьшаемый в нуль в начале каждого полупериода напряжения источника 9 переменного тока импульсом (фиг. 4г), поступающим с выхода формирователя 3 импульсов через второй вход элемента 21 2И-НЕ, вырабатывает сигналы временной кодовой развертки (фиг. 4д), которые поступают с его выхода на вторые входы первого и второго элементов 16 и 17 сравнения. При выравнивании кодов на входах первого и второго элементов 16 и 17 сравнения, а также при дальнейшем возрастании кода на вторых входах этих элементов на их выходах устанавливается единичный сигнал. Единичные сигналы с выходов первого и второго элементов 16 и 17 сравнения поступают, соответственно, на первый и третий входы элемента 4 2И-2ИЛИ, где они коммутируются парафазнымн сигналами, поступающими с выходов формирователя 1 пара-, фазных синхросигналов на второй и четвертый входы элемента 4 2И-2ИЛИ. Единичный сигнал с выхода элемента 4 2И2ИЛИ (фиг. 4ж) обеспечивает через усилитель 5 поочередное включение тиристоров 6. Начальный угол включения тиристоров 6 задается кодом, набранным на входах предустановки реёерсивного счетчика 29 первого и второго элементов 12 и 13 памяти. При токах в нелинейной нагрузке 8 (фиг. 4м), не превышающих определенной величины, заданной в компараторе 10 установкой, на его выходе сигнал имеет нулевой уровень (фш;. 4н). Этот сигнал поступает на вход направления счета перiBoro и второго элементов 12 и 13 памяти, в которых он приходит на первый вход элемента 24 2И-НЕ, на выходе которого формируется единичный сигнал, не оказывающий влияния на RS-триггер 26, к R-входу которого он прикладывается. При единичном сигнале на входе разрешения счета первого и второгоэлементов 12 и 13 памяти импульсы нулевого уровня, поступающие с выхода формирователя импульсов 3 на вход синхронизации первого и второго элементов 12 и 13 памяти, устанавливают RS-триггер 26 в единичное состояние. Единичный сигнал с выхода RS-триггера 26 запрещает поступление через элемент 27 2ИЛИ-НЕ импульсов с выхода элемента 25 2ИЛИ на вход суммирования реверсивного счетчика 29. Напротив, нулевой сигнал с выхода RS-триггера 26 разрешает поступление через элемент 28 4ИЛИНЕ импульсов с выхода элемента 25 2ИЛИ на вход вычитания реверсивного счетчика 29. Счетные импульсы, поступающие на вход вы итания реверсивного счетчика. 29 с частотой напряжения источника 9 переменного тока постепенно уменьшают число, записанное в реверсивном счетчике 29, что сопровождается уменьшением угла включения тиристоров 6 в соответствзоощем полупериоде напряжения источниi ка 9 переменного тока. По мере уменьшения угла включения тиристоров 6 ток (фиг. 4м) в нелинейной нагрузке 8 будет возрастать. При увеличении его сверх установленной величины срабатывает компаратор 10, на выходе; которого формируется единичный сигнал (фиг. 4н), поступающий на вход направления счета пер-вого и второго элементов 12 и 13 памяти. Выходной сигнал компаратора 10 проходит на выход элемента 24 2И-НЕ в том из элементов 12 и 13 памяти, на входе разрешения счета которого в этот момент оказывается единичнь.й сиг нал с выхода формирователя 1 парафазных син хросигналов. Нулевой сигиал, приходящий с выхода Элемента 24 2И-НЕ на R-вход RS-триггера 26, перебрасывает его из единичного состо яния, в которое он периодически устанавливает ся в начале поступления единичного сигнала на вход разрешения счета элемента памяти, в нулевое состояние, при котором запрещается поступление счетиого импульса с выхода элемента 25 2ИЛИ через элемент 28 4ИЛИ-НЕ на вхо вычитания реверсивного счетчика 29 и разрешается его прохождение через элемент 27 2ИЛИНЕ на вход суммирования реверсивного счетчика 29. С увеличением числа, записанного в реверсивном счетчике 29, угол включения тиристоров 6 в соответствующем пол)шериоде возрастает, а ток в нелинейиой нагрузке 8 уменьшается. После уменьшения тока через соответствующий тиристор 6 ниже установленного значения компаратор 10 перестанет переключать RS-триггер 26 из единичного состояния в нулевое, и счетные импульсы начнут поступать на вход вьтитания реверсивного счетчика 29. Прн активной нелинейной нагрузке 8 скорость изменения угла включения тиристоров 6 ограничивается обратной связью по току через датчики 7 тока и компаратор 10. Благодаря обратной связи обеспечивается баланс токов через оба тиристора 6 во всем диапазоне регулирования их угла включения 180-0 . В конце переходного процесса включения тиристоров 6 в реверсивном счетчике 29 первого и второго элементов 12 и 13 памяти устанавливается нулевой код, соответствующий углу включения О после чего дальнейшее поступление импульсов на вход вьгаитания реверсивного счетчика 29 запрещается единичным сигналом с выхода соответствующего дешифратора - 19 или 20, приходящим на третий вход элемента 28 4ИЛИНЕ. При нелинейной нагрузке 8, содержащей индуктивную составляющую, регулирование угла включения тиристоров 6 в диапазоне от 180 ДО угла включения, находящегося в зоне О - 90 , при котором ЭДС со стороны нагрузки 8 становится равной напряжению источников 9 переменного тока, происходит так же, как при активиой нелинейной нагрузке. Дальнейщее же уменьшение угла включения тиристоров 6 приводит к тому, что один из них захватывает начальный участок включения др)того тиристора из-за влияния ЭДС. со стороны нагрузки. В результате этого появляется разбаланс токов через тиристоры 6, величина которого начинает ограничиваться схемой регулирования угла включения тиристоров. При увеличении разбаланса токов до величины, при которсж величина тока через один из тиристоров превысит установленную величину, угол включения соответствующего тиристора начнет увеличиваться. Угол включения другого тиристора будет продолжать уменьшаться, но только до тех пор, пока разность кодов с выходов первого и второго элементов 12 и 13, определяющих угол включения тиристоров 6, не превысит установлеиную величину, контроль чего осуществляет третий элемент 18 сравнения, на входы которого посгупают сигналы с выходов первого и второго элементов 12 и 13 памяти. Третий элемент 18 сравнения выдает на обоих выходах нулевой сигнал, пока разность меж кодовыми сигналами на его входах не превьппает установленной величины. Когда же разность между кодовыми сигналами превысит установленную величину, третий элемент 18 сравнения сформирует единичный сигнал либо на первом выходе (фиг. 4о), если кодовой сигнал на первом входе меньше кодового сигнала на втором входе, либо на втором. выходе (фиг. 4п), если кодовой сигнал на первом входе больше кодового сигнала на втором входе. При единичном сигнале на первом выходе третьего злемента 18 сравнения запрещается поступление счетных импульсов на вход рычитания реверсивного счетчика 29 первого элемента 12 памяти и, следовательно, уменьшетие угла включения одного из тиристоров 6, а при единичном сигнале на втором выходе третьего злемента 18 сравнения запрещается поступление счетных импульсов на вход вычитания реверсивного счетчика 29 второго элемента 13 памяти и, следовательно, уменьшение угла включения другого из тиристоров 6. Благодаря этому обеспечивается автоматтпеское ограничение не только величины тока через тиристоры 6, ио и ограничение разности токов через них, что способствует уменьшению постоянной составляющей тока через источник переменного тока, уменьшение ЭДС со стороны нагрузки и выравниванию загрузки тиристоров по току. При этом напряжение питания нелинейной нагрузки 8 имеет, вид симметричных импульсов (фиг. 4р). Таким образом, данное устройство обеспечивает по сравнению с известными аналогичными решениями повышение надежности при коммутации питания нелинейной нагрузки, содержащей, в частности, индуктивную составляющую, благодаря устранению бросков тока через тиристоры при включении питания нелинейной нагрузки и ограничению на заданном уровне величины тока через тиристоры в каждом из полупериодов напряжения источника переменно го тока за счет постепенного изменения углов включения тиристоров от максимального значения в сторону 0° и регулирования их величи ны и скорости изменения, и, благодаря выравниванию загрузки тиристоров по току путем раздельного регулирования зтлов включения тиристоров и ограничения меньшего из утпоъ включения тиристоров при увеличении сверх установленной величины разности кодов, определяющих их углы включения. Формула изобретения Устройство для управления встречно-параллельно включенными тиристорами, содержащее подключенный к источнику переменного тока формирователь парафазных синхросигналов, формирователь импульсов, вход которого соединен с первым входом формирователя парафазньЬс синхросигналов, элемент 2И-2ИЛИ, уси литель, вход которого соединен с выходом зле мента 2И-2ИЛИ, а выход подключен к управляющим входам тиристоров, датчик тока, вклю ченный последовательно с тиристорами и нелинейной нагрузкой в цепь HCTO4iiHKa переменного тока, компаратор, вход которого соединен с выходом датчика тока, и входную шину команды Пуск, отличающееся тем что, с целью повышения надежности устройства, в него введены два элемента памяти, суммирующий счетчик, генератор, три элемента сравнения, два дешифратора и элемент 2И-НЕ, причем вход формирователя импульсов соединен с входом разрешения счета первого элемен та памяти и вторым входом элемента 2И-2ИЛ 12 а выход формирователя импульсов подключен к входу синхронизации первого и второго элементов памяти и ко второму входу элемента 2И-НЕ, второй выход формирователя парафазных синхросигналов соединен с входом разрешения счета второго элемента памяти и четвертым входом элемента 2И-2ИЛИ, вход направления счета первого элемента памяти подключен к . входу направления счета второго элемента памяти и выходу компаратора, вход предустановки первого элемента памяти соединен с входной шиной команды Пуск, первым входом элемента 2И-НЕ и входом предустановки второго элемента памяти, выход первого элемента памяти подключен к первому входу первого элемента сравнения, первому входуТретьего элемента сравнения и входу первого дешифратора, выход которого соединен с первым входом запрета вычитания первого элемента памяти, выход второго элемента памяти соединен с первым входом второго элемента сравнения, вторым входом третьего элемента сравнения и входом второго дешифратора, выход которого подключен к первому входу запрета вычитания второго элемента памяти, второй вход первого элемента сравнения соединен со вторым входом второго элемента сравнения и выходом. суммир)тощего счетчика, счетный вход которого подключен к выходу генератора, а вход сброса подключен к выходу элемента 2И-НЕ, выход первого элемента сравнения соединен с первым входом элемента 2И-2ИЛИ, выход второго элемента сравнения соединен с третьим входом элемента 2Й-2ИЛИ, первый выход третьего элемента сравнения подключен к второму входу запрета вычитания первого элемента памяти, а второй выход третьего элемента сравнения подключен к второму входу запрета вычитания второго элемента памяти. Источники информации, принятые во внимание при экспертизе L Заявка Японии № 52-13783, кл. 58 GO; кл. Н 03 К 17/72, 1978. 2. Авторское свидетельство СССР по заявке № 2514847/04, кл. Н 03 К 17/72, 1977.

иг. 3

fe

Авторы

Даты

1981-11-23—Публикация

1979-11-30—Подача