рователь 12, дешифратор 13, цифровой индикатор 14.

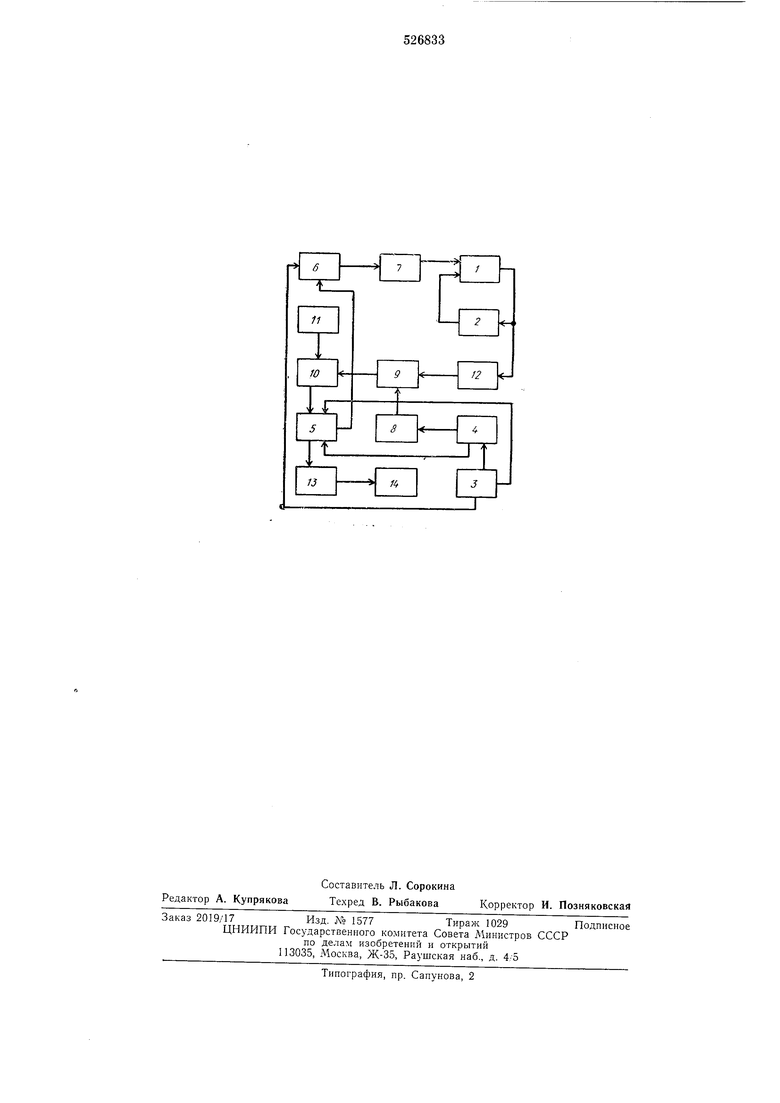

Измеритель пороговых напряжений логических схем содержит последовательно соединенные генератор 11 тактовых импульсов, селектор 10, счетчик 5, дешифратор 13 и цифровой .индикатор 14, а также последовательно соединенные формирователь 12 ,и триггер 9, выход которого подключен к селектору 10. Между входом -и выходом логической схемы 1 включена цепь 2 положительной обратной связи, причем выход логической схемы 1 связап с формирователем 12, а вход этой схемы через буфферпый каскад 7 и управляемый источник 6 двухполярпого линейно-.измепяющегося напряжения соединен с выходом счетчика 5. Одип вход счетч.ика 5 связан с коммутатором 3, выход которого соединен с входом источника 6 двухполярного линейно-изменяющегося напряжения, а генератор 4 сброса соединен со счетчиком 5 л линией 8 задержки, подключенной к входу триггера 9.

Принцип работы измерителя заключается в использовании принципа регенерации. Для этого вход логической схемы I через цепь 2 соединен с ее выходом. В качестве этой цепи используется отрезок коокспального кабеля, который обеспечивает выполнение баланса фаз. Процесс регенерации при выполнении баланса фаз начинается в случае выполнения баланса амплитуд, т. е. когда коэффициент передачи логической схемы больше или равен единице. Коэффициент передачи логической схемы зависит от величины постоянноного напряжения, приложенного к входу схемы.

В исходном состоянии (для определения порогового напряжения логической единицы) к входу логической схемы приложено напряжение, превышающее верхний пороговый уровень. Это обеспечивается при помощи коммутатора 3, который через генератор 4 сброса устанавливает счетчик 5 в исходное состояние, а также переключает источник 6 двухполярного линейно-изменяющегося напряжения в положение, подготавливающее изменение выходного напряжения па его выходе и входе буфферного каскада 7 в сторону уменьшения. Генерация логической схемы отсзтствует. После включения коммутатора 3 через время, равное времени задержки линии 8, на один из входов триггера 9 поступает импульс сброса от генератора 4 сброса, который переводит триггер 9 в положение, открывающее селектор 10. При этом от геператора И на счетчик 5 поступают счетные импульсы. С каждым подсчитанным счетчиком импульсом на определенную величину по линейному закону уменьшается выходное напряжение управляемого источника 6, а синхронно с ним и напряжение на выходе буфферного каскада 7 (входе логической

схемы 1). Такой процесс будет продолжаться до тех нор, пока его величина станет равной верхнему уровню порогового напряжения. Пр.и этом логическая схема начнет генерировать (режим возбуждения жесткий). Первый импульс генерации, сформированный формирователем 12, опрокидывает триггер 9 в положение, закрывающее селектор 10, в результате чего режим изменения остановится. Показания

10 цифрового индикатора 14, соединенного через дешифратор 13 с счетчиком 5, фиксируют величину верхнего порогового уровня.

Измерение нижнего порогового напряжения осуществляется аналогично. Противоположный закон изменения напряжения на входе логической схемы, а также исходное смещен.ие этого напряжения обеспечивает коммутатор 3. Счетчик 5 в начале измерения аналогичным образом устанавливается в исход20 ное состояние.

Для получения высокой точности измерения частота генератора 11 должна быть меньше частоты генерации логической схемы, которая должна быть значительно меньше рабочей

.5 частоты логической схемы. Приращение напряжения на выходе управляемого источника 6, а также с ней связанное кол.ичество разрядов счетчика и диапазон значений пороговых напряжений зависят от заданной точности из0 мерения.

Формула изобретения

Автоматический измеритель нороговых напряжений логических схем, содержащий последовательно соединенные тактовый генератор импульсов, селектор, счетчик, дешифратор и цифровой индикатор и последовательно соединенные формирователь .и триггер, выход которого подключен к селектору, отличающийся тем, что, с целью повышения точности измерений, в пего введены цепь пололсительной обратной связи, выход и вход которой соединены соответственно с выходным

5 и входным зажимами устройства, выходной зажим связап с формирователем, управляемый источник двухполярного линейно-изменяющегося напряжения, вход которого соединен со счетчиком, а выход - через буферный блок

0 с логической схемой, последовательно соединенные ком.мутатор, генератор сброса и линия задержки, выход которой подключен к другому входу триггера, причем коммутатор соединен со счетчиком и с управ.ляемым источником двухполярного лппейно-пзменяющегося напряжения, а генератор сброса соединен со счетчиком.

Источники информации, принятые во вннмание при экспертизе:

1. Авт. св. № 266945, G 01R 31/28, 1969. 2. Авт. св. № 266943, G 01R 31/28, 1969.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Автоматический измеритель пороговых напряжений логических схем | 1985 |

|

SU1372255A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Устройство для диагностики дизельного двигателя внутреннего сгорания | 1981 |

|

SU1002879A2 |

| Устройство регулирования и стабилизации мощности | 1987 |

|

SU1578703A1 |

| Ритмический электромузыкальныйиНСТРуМЕНТ | 1977 |

|

SU798974A1 |

| Вторичные часы | 1986 |

|

SU1525671A1 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ В ЛИНИЮ СВЯЗИ | 2006 |

|

RU2313914C1 |

| Устройство для измерения динамических параметров быстродействующих аналого-цифровых преобразователей | 1987 |

|

SU1522401A1 |

| УСТРОЙСТВО ДЛЯ ИМПЕДАНСОМЕТРИИ | 2001 |

|

RU2196505C2 |

Авторы

Даты

1976-08-30—Публикация

1974-05-12—Подача