Изобретение относится к технике автоматического регулирования и стабилизации мощности переменного тока с дискретным управлением нагрузки целыми волнами и неизменным циклом, с коммутацией в нуле, начальной положительной фазой, изменяемой скважи- ностью импульса, стабилизацией переменного напряжения с помощью изменения импульса и паузы.

Цель изобретения - улучшение качества регулирования.

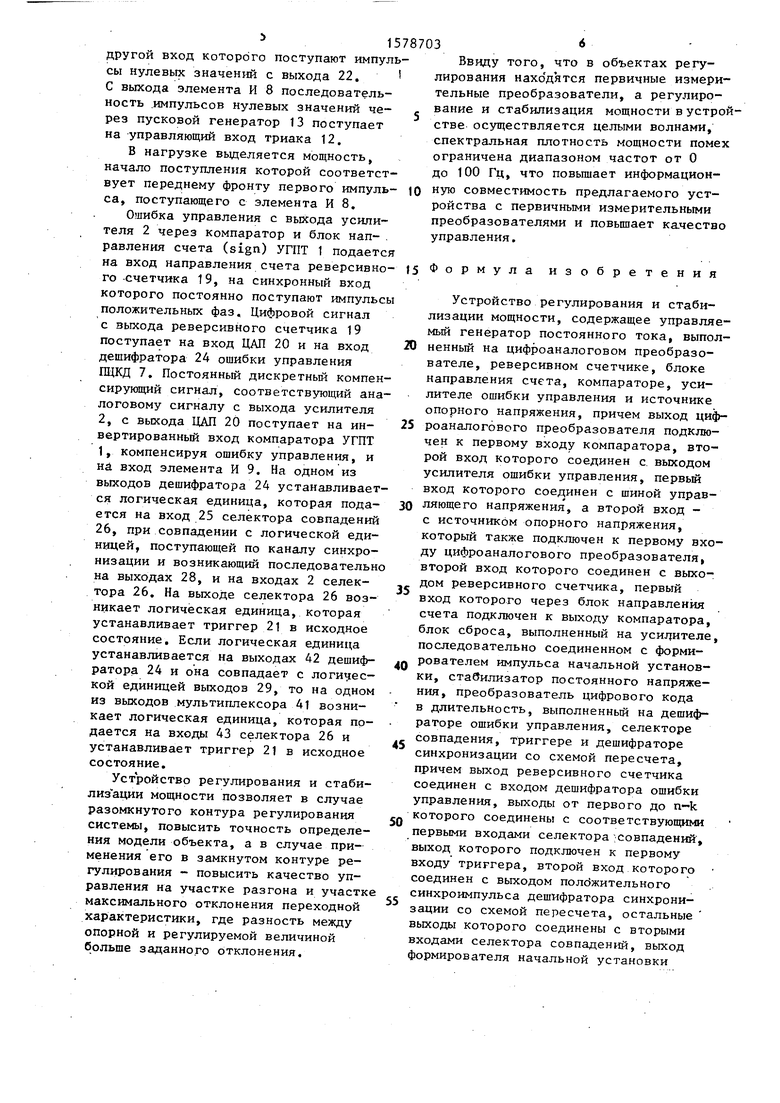

На чертеже изображена блок-схема устройства.

Устройство регулирования и стабилизации мощности содержит управляемый

генератор постоянного тока (УГПТ)1, выполненный на аналого-цифровом пре- . образователе по компенсационному типу с последовательным выравниванием, инвертированный вход усилителя 2 ошибки управления которого соединен с шиной 3 управляющего напряжения, блок сброса 4, детектор фаз и нулевых значений (ДФНЗ) 5, стабилизатор постоянного напряжения 6, преобразователь цифрового кода в длительность (ПЦКД) 7, два элемента И 8 и 9, источник 10 питания переменного напряжения (ИППН), выполненный без сдвига фаз,и подключенный через нагрузку 11 к сети переменного тока триак 12, соединенный

О1 J

00

J

о со

через пусковой генератор 13 и первый элемент И 8 с выходом моностабильного триггерного каскада 14, неинвертирующий вход усилителя 15 блока сброса 4, соединен с выходом усилителя 2, входы формирователя 16 импульса начальной установки блока сброса 4 соединены с выходами 17 и 18 отрицательных и положительных фаз ДФНЗ 5, вход ДФНЗ 5 соединен с выходом ИППН 10, выход 18 положительных фаз соединен со входом реверсивного счетчика 19 УГПТ 1 и с первым входом второго элемента И 9, второй вход которого соединен с выходом цифроаналогового преобразователя ЩАЛ) 20 УГПТ1, третий - с выходом триггера 21 ПЦКД 7, а выход - со входом моностабильного триггерного каскада 10. Выход 22 нулевых значений ДФНЗ 5 соединен с другим входом первого элемента И 8 и со входом детектора синхронизации со схемой пересчета (ДССП) 23. Выход реверсивного счетчика 19 соединен со входом дешиф- ратора ошибки управления 24 ПЦКД 7.

Выходы с 1 до n-к дешифратора 24 соединены с первыми входами 25 селектора совпадений 26. Выход положительных синхроимпульсов 27 ДССП 23 соеди- нен со входом S триггера 21, выходы 28 и 29 ДССП 23 соединены со вторыми входами селектора 26. Выход формирователя 16 импульса начальной установки соединен со входом 30 ДССП 23, второй выход ИППН Ю соединен со вхо- дом стабилизатора 6 постоянного напряжения. Устройство снабжено следующими аналоговыми коммутаторами с памятью (САКП) 31 и 32, включающими соответственно соединенные последовательно следящие усилители 33 и 34, ключи 35 и 36, интеграторы 37 и 38. Усилитель САКП 31 имеет регулируемый коэффициент усиления. Устройство снабжено также формирователем 39 им- пульсов привязки, аналого-цифровым преобразователем отклонения сетевого напряжения (АЦПОСН) 40, мультиплексором 41. Выход стабилизатора 6 постоянного напряжения соединен с усили- телем 34 САКП 32, выход интегратора 38 которого через резистивную матрицу АЦПОСН 40 соединен с инвертирующими входами компаратора АЦ ПОСН 40 (резистивная матрица и компараторы, имеющие инвертируемые и неинвертируемые входы, которые находятся в состав АЦ ПОСН 40 на чертеже не показаны.

j Q 5

0 5

0

Затворы полевых транзисторов ключей 35 и 36 САКП 31 и 32 соединены друг с другом и с выходом формирователя 39, вход которого соединен с положительным выходом 18 ДФНЗ 5, выход ИППН

10соединен со входом усилителя 33. САКП 31, выход интегратора 37 которого соединен с неинвертирующими входами компараторов АЦ ПОСН 40, выход 18 положительных фаз соединен со входом синхронизации АЦ ПОСН 40, выходы которого соединены с управляющими входами мультиплексора-41, информационные входы которого соединены с выходами 29 ДССП 23 и выходами 42 дешифратора ошибки управления 24. Выходы мультиплексора 41 соединены

с первыми входами 43 селектора совпадений 26. Триак 12 через нагрузку

11связан с сетью.

Устройство работает следующим образом.

С выхода ИППН Ю на вход ДФНЗ 5 поступает переменное напряжение. На выходах 18, 17 и 22 ДФНЗ 5 формируются соответственно импульсы положительных и отрицательных фаз и нулевых значений. Импульсы положительных и отрицательных фаз поступают на вход формирователя 16 импульсов начальной установки блока сброса 4. При изменении управляющего напряжения на шине 3 на выходе усилителя 2 возникает ошибка управления, а на выходе усилителя 15 блока сброса 4 возникает ступенчатая функция. По переднему фронту импульса отрицательной фазы формирователь 16 сбрасывает ДССП 23 в ноль, а по переднему фронту следующего импульса положительной фазы производится запуск ДССП 23, при этом импульсы нулевых значений поступают на вход синхронизации ДССП 23. Импульс с выхода 27 поступает на вход триггера 21 и устанавливает на его выходе логическую единицу.

Сигнал с ВЫХОДР триггера 21 поступает на вход элемента И 9, на другие входы которого с выхода 18 поступают импульсы положительных фаз, а на третий вход И 9 поступает положительное напряженке с выхода ЦАП 20. На выходе элементов И 9 формируется последовательность импульсов положительной фазы, которые поступают на моностабильный триггерный каскад 14, последовательность импульсов с которого поступает на элемент И 8, на

51

другой вход которого поступают импулсы нулевых значений с выхода 22. С выхода элемента И 8 последовательность импульсов нулевых значений через пусковой генератор 13 поступает на управляющий вход триака 12.

В нагрузке выделяется мощность, начало поступления которой соответствует переднему фронту первого импульса, поступающего с элемента И 8.

Ошибка управления с выхода усилителя 2 через компаратор и блок направления счета (sign) УГПТ 1 подаетс на вход направления счета реверсивного счетчика 19, на синхронный вход которого постоянно поступают импульс положительных фаз. Цифровой сигнал с выхода реверсивного счетчика 19 поступает на вход ЦАП 20 и на вход дешифратора 24 ошибки управления ПЦКД 7. Постоянный дискретный компенсирующий сигнал, соответствующий аналоговому сигналу с выхода усилителя 2, с выхода ЦАП 20 поступает на инвертированный вход компаратора УГПТ 1, компенсируя ошибку управления, и на вход элемента И 9. На одном из выходов дешифратора 24 устанавливается логическая единица, которая подается на вход 25 селектора совпадений 26, при совпадении с логической единицей, поступающей по каналу синхронизации и возникающий последовательн на выходах 28, и на входах 2 селектора 26. На выходе селектора 26 возникает логическая единица, которая устанавливает триггер 21 в исходное состояние. Если логическая единица устанавливается на выходах 42 дешифратора 24 и она совпадает с логической единицей выходов 29, то на одном из выходов мультиплексора 41 возникает логическая единица, которая подается на входы 43 селектора 26 и устанавливает триггер 21 в исходное состояние.

Устройство регулирования и стаби- мощности позволяет в случае разомкнутого контура регулирования системы, повысить точность определения модели объекта, а в случае применения его в замкнутом контуре регулирования - повысить качество управления на участке разгона и участке максимального отклонения переходной характеристики, где разность между опорной и регулируемой величиной больше заданного отклонения.

Ввиду того, что в объектах регулирования нахо дятся первичные измерительные преобразователи, а регулирование и стабилизация мощности в устройстве осуществляется целыми волнами, спектральная плотность мощности помех ограничена диапазоном частот от О до 100 Гц, что повышает информационную совместимость предлагаемого устройства с первичными измерительными преобразователями и повышает качество управления.

15 Формула изобретения

Устройство регулирования и стабилизации мощности, содержащее управляемый генератор постоянного тока, выполненный на цифроаналоговом преобразо5

0

5

0

5

0

5

вателе, реверсивном счетчике, блоке направления счета, компараторе, усилителе ошибки управления и источнике опорного напряжения, причем выход циф- роаналогового преобразователя подключен к первому входу компаратора, второй вход которого соединен с выходом усилителя ошибки управления, первый вход которого соединен с шиной управляющего напряжения, а второй вход - с источником опорного напряжения, который также подключен к первому входу цифроаналогового преобразователя, второй вход которого соединен с выходом реверсивного счетчика, первый вход которого через блок направления счета подключен к выходу компаратора, блок сброса, выполненный на усилителе, последовательно соединенном с формирователем импульса начальной установки, стабилизатор постоянного напряжения, преобразователь цифрового кода в длительность, выполненный на дешифраторе ошибки управления, селекторе совпадения, триггере и дешифраторе синхронизации со схемой пересчета, причем выход реверсивного счетчика соединен с входом дешифратора ошибки управления, выходы от первого до n-k которого соединены с соответствующими первыми входами селектора совпадений, выход которого подключен к первому входу триггера, второй вход которого соединен с выходом положительного синхроимпульса дешифратора синхронизации со схемой пересчета, остальные выходы которого соединены с вторыми входами селектора совпадений, выход формирователя начальной установки

блока сброса соединен с входом дешифратора синхронизации со схемой пересчета, два элемента И, источник питания переменного напряжения без сдвига фаз, триак, включенный между выводами для подключения сети переменного тока и выводами для подключения нагрузки, управляющий вход триака через последовательно соединенные пусковой гене- ратор и первый элемент И подключен к выходу моностабильного триггерного каскада, неинвертирующий вход усилителя блока сброса соединен с выходом усилителя ошибки управления, детектор фаз и нулевых значений, выходы отрицательных и положительных фаз которого соединены с соответствующими входами формирователя импульса начальной установки, а выход положительных фаз - с вторым входом реверсивного счетчика и с первым входом второго элемента И, второй вход которого соединен с выходом цифроаналогового преобразователя, а третий вход - с выхо- дом триггера, выход второго элемента И подключен к входу моностабильного триггерного каскада, при этом первый выход источника питания переменного напряжения без сдвига фаз подключен к входу детектора фаз и нулевых значений, а второй выход - к входу стабилизатора постоянных напряжений, отличающееся тем, что, с целью улучшения качества регулиро- вания, оно снабжено двумя следящими аналоговыми коммутаторами с памятью, каждый из которых выполнен на последовательно соединенных следящем усилителе, ключе и интеграторе, причем следящий усилитель первого следящего

аналогового коммутатора с памятью выполнен с регулируемым коэффициентом усиления, формирователем импульсов привязки, аналого-цифровым преобразователем отклонения сетевого напряжения, включающего резистивную матрицу и компараторы, а также мультиплексором, при этом третий выход источника питания переменного напряжения без сдвига фаз подключен к входу следящего усилителя первого следящего аналогового коммутатора, выход интегратора которого соединен с неинвертированными входами компараторов аналого-цифрового преобразователя отклонения сетевого напряжения, инвертированные входы которых через резистивную матрицу подключены к выходу интеграторов второго следящего аналогового коммутатора, вход следящего усилителя которого соединен с выходом стабилизатора постоянного напряжения, управляющие входы ключей первого и второго следящих аналоговых коммутаторов объединены и подключены к выходу формирователя импульсов привязки, вход которого соединен с выходом положительных фаз детектора фаз и нулевых значений, куда также подключен вход синхронизации аналого-цифрового преобразователя отклонения сетевого напряжения, выходы которого соединены с управляемыми входами мультиплексора, информационные входы которого соединены с выходами от n-k-1 до п дешифратора синхронизации со схемой пересчета и дешифратора ошибки управления, выходы мультиплексора соединены с оставшимися первыми входами се- Iлектора совпадений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регулирования мощности | 1988 |

|

SU1543394A1 |

| Устройство для регулирования мощности | 1986 |

|

SU1422230A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Динамическое запоминающее устройство | 1988 |

|

SU1596396A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1465914A1 |

| Следящая система | 1985 |

|

SU1290251A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

Изобретение относится к вторичным источникам питания радиоаппаратуры. Целью изобретения является улучшение качества регулирования. Цель достигается тем, что обеспечивается уменьшение возмущений замкнутой системы, вызываемых колебаниями сети, на участках разгона, максимального отклонения переходной характеристики и в случае разомкнутого контура. Для этого в устройстве сравнение переменного напряжения сети с постоянным напряжением производится с помощью формирователя импульсов привязки, который выбирает из синусоиды узкий участок, соответствующий амплитудному значению, на длине которого напряжение можно считать постоянным. Далее амплитудное значение сетевого напряжения сравнивается с помощью двух следящих усилителей с памятью, аналого-цифрового преобразователя сетевого напряжения и мультиплексора с постоянным напряжением, являющимся эквивалентом действующего переменного напряжения. 1 ил.

| Регулятор мощности на тиристорах для однофазного и многофазного управления | |||

| Материалы фирмы Филипс ФРГ.М | |||

| ГПНТБ СССР, пер | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1914 |

|

SU1422A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-07-15—Публикация

1987-06-18—Подача