со

vj

to кэ ел ел

Изобретение относится к технике измерения статических параметров интегральных микросхем, в частности к измерению пороговых напряжений логических схем.

Цель изобретения - повышение быстродействия за счет повышения частоты работы тактового генератора и более быстрой перестройки счетчика в процессе цикла измерений.

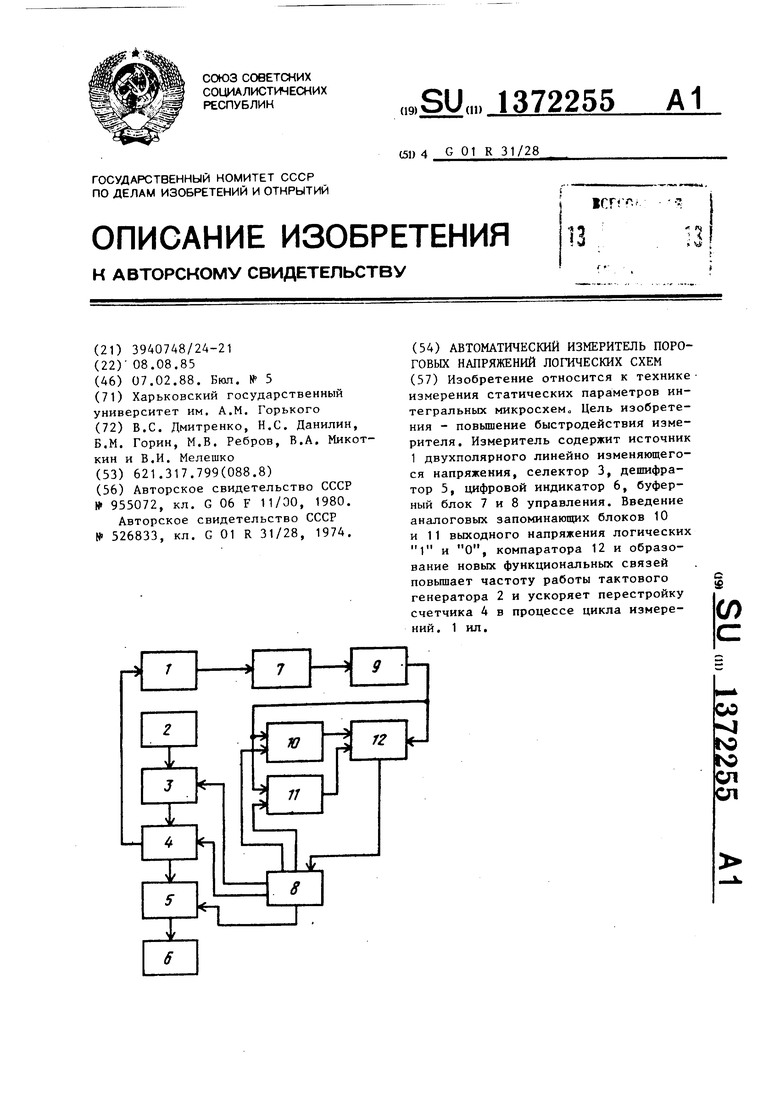

На чертеже изображена структурная схема автоматического измерителя поррговых напряжений логических хем.

Устройство содержит управляемый источник 1 двухполярного линейно изменяющегося напряжения, выполненный на основе цифроаналогового преобразователя типа код-напряжение, например на основе прецизионного 12-разрядного ЦАП 59АПА1; тактовый генератор 2, представляющий собой генератор импульсов; селектор 3, выполненный на основе стандартных логических элементов типа И-НЕ; счетчик 4, представляющий собой реверсивный счетчик (работающий на сложение и вычитание) с возможностью установк начального кода и выполненный на базе цифровых интегральных микросхем, в частности на реверсивных двоично- десятичных счетчиках серии 155; дешифратор 5, выполненный на базе логических элементов и щинных формирователей с тремя состояниями; цифровой индикатор 6, представляющий цифровое табло со схемой управления; буферный блок 7, собранный на усилителе с единичным коэффициентом усиления; блок 8 управления, собранный на базе логических элементов и интегральных схем средней степени интеграции; исследуемую логическую схему 9 (в частности инвертирующие логические микросхемы серии 16А, 564) - объект контроля; аналоговый запоминающий блок 10 выходного напряжения логической единицы (1), реализуемый по типовой схеме устройства выборки - хранения с помощью запоминающего конденсатора, операционного усилителя и ключей на МОП-транзисторах; аналоговый запоминающий блок 11 выходного напряжения логического нуля (О, выполненный аналогично блоку 10; компаратор 12, выполненный в виде функционально законченного

устройства в интегральном исполнении 597САЗ.

Выход актового генератора 2 соединен с первым входом селектора 3, первый вход счетчика 4 - с вьсходом селектора 3, второй вход - с первым выходом блока 8 управления, первый выход - с первым входом дешифратора

5, а второй - с входом управляемого источника 1 двухполярного линейно изменяющегося напряжения, выход которого через буферный блок 7 соединен с объектом контроля 9. Вход циф5 рового индикатора 6 соединен с выходом дешифратора 5.

Первый вход компаратора 12 соединен с выходом объекта 9 контроля и с первыми входами аналоговых запоминаюQ щих блока 11 выходного напряжения логического нуля и блока 10 выходного напряжения логической единицы, второй вход компаратора 12 - с выходом аналогового запоминающего бло5 ка 10 выходного напряжения логической единицы, третий вход - с выходом аналогового запоминающего блока 11 выходного напряжения логического нуля, выход компаратора 12 - с

0 входом блока 8 управления. Второй выход блока 8 управления соединен с вторым входом аналогового запоминающего блока 10 выходного напряжения логической единицы, третий выход - с вторым входом аналогового запоминающего блока 11 выходного напряжения логического нуля, четвертый выход - с вторым входом селектора 4, а пятый выход - с вторым входом де„ шифратора 5

Устройство работает следующим образом.

При запуске устройства из блока 8 управления на второй вход счетчика

5 поступает сигнал установки кода, соответствующего минимальному напряжению логического О на входе исследуемой микросхемы в соответствии с техническими условиями, и команда,

0 переключающая режим работы счетчика 4 на сложение. С второго выхода счетчика 4 заданный код поступает на вход источника 1 двухполярного линейно изменяющегося напряжения, на

5 выходу которого формируется напряжение, адекватное заданному коду.

Полученное напряжение через буферный блок 7, предназначенный для электрического согласования источника 1

3

и логической схемы 9, поступает на вход иЬследуемой логической схемы например логического инвертора. Пр этом схема 9 переходит в устойчиво состояние и на ее выходе появляетс напряжение логической 1, которое поступает на вход аналогового запоминающего блока 10 выходного напряжения логической 1 в устойчивом состоянии. По команде из блока 8 управления это напряжение запоминается в аналоговом запоминающем блоке 10, который затем переводится по команде из блока 8 управления из режи ма записи в режим хранения. При это выходное напряжение логической 1 в устойчивом состоянии логической инвертирующей схемы 9 с выхода блока 10 поступает на второй вход компаратора 12.

Сигналом с четвертого выхода блока 8 управления открывается селектор 3 и сигналы тактового генератора 2 начинают поступать на счетчик 4, причем частота тактового генератора 2 выбирается, исходя из быстродействия измерителя, а точность измерения определяется разрядностью цифроаналогового преобразователя источника 1 напряжения„ С каждым подсчитанным счетчиком импульсом на определенную величину по линейному закону увеличивается выходное напряжение управляемого источника 1 а синхронно с ним и напряжение на выходе буферного блока 7 (т.е. на входе исследуемой логической схемы 9

Текущее значение напряжения логи

ческой 1 с выхода логической схемы 9 поступает на первый вход компаратора 12 и сравнивается с напряжением логической 1, поступающей на второй вход компаратора 12 с аналогового запоминающего блока 10. В момент неравенства этих двух напряжений вырабатывается сигнал, поступающий с выхода компаратора 12 на второй вход селектора 3 и запрещающий прохождение тактовых импульсов с генератора 2 на вход счетчика 4.

Одновременно этот сигнал поступает на вход блока 8 управления, где формируется сигнал на разрешение считывания информации со счетчика, который с пятого выхода блока 8 управления поступает на второй вход дешифратора 5. Показания счетчика 4, адекватные напряжению источника 1

10

20

5

0

5

напряжения и преобразованные в дешифраторе 5 в код цифрового индикатора 6, фиксируют на цифровом индикаторе 6 значение порогового напряжения логического О, после чего с блока 8 управления на второй вход аналогового запоминающего блока 10 поступает сигнал сброса, на второй вход счетчика 4 - сигнал установки кода, соответствующего максимальному напряжению логической 1 на выходе исследуемой логической схемы, и команда, переключающая режим работы счет«1Ика на вычитание.

С выхода счетчика 4 заданный код поступает на вход управляемого источника 1 напряжения, на выходе которого формируется напряжение, переводящее логическую схему 9 в другое устойчивое состояние. При этом напряжение логического О с выхода логической схемы 9 поступает на вход аналогового запоминающего блока 11 выходного напряжения логического О и запоминается по команде из блока 8 управления. После этого аналоговый запоминающий блок 11 переводится в режим хранения и на его выходе по- является напряжение, соответствую 0

0

5

0

5

щее напряжению логического U в устойчивом состоянии микросхемы. Сигналом с четвертого выхода блока 8 управления открывается селектор 3 и тактовые импульсы начинают проходить на вход счетчика 4, работающего в режиме вычитания.

С каждым подсчитанным импульсом напряжение на выходе управляемого источника 1 начинает уменьшаться. Текущее значение напряжения логического О с выхода микросхемы 9 сравнивается компаратором 12 с напряжением, поступающим с аналогового запоминающего блока 11, и в момент неравенства с выхода компаратора 12 снимается сигнал, закрывающий селектор 3 и формирующий в блоке 8 управления сигнал на разрешение считывания информации. Соответствующей значению порогового напряжения логической 1. Показания цифрового индикатора 6, соединенного через открытый дешифратор 5 со счетчиком 4, фиксируют значение порогового напряжения логической 1. В зависимости от программы измерений происходит остановка устройства или переход к новому циклу измерений.

I

Формула изобретени Автоматический измеритель порогвых напряжений логических схем, содержащий тактовый генератор, выход которого соединен с первым входом селектора, счетчик, первый вход корого соединен с выходом селектора, второй вход соединен с первым выходом блока управления, первый выход соединен с первым входом дешифрато

ра, а второй - с входом управляемого источника двухполярного линейно изменяющегося напряжения, выход которого через буферный блок соединен с первой клеммой для подключения объекта контроля, цифровой индикатор, вход которого соединен с выходом дешифратора, отличающийся тем, что, с целью повьшения быстро- действия, в него введены аналоговый запоминающий блок выходного напряжения логического нуля, аналоговый запоминающий блок выходного напряжения логической единицы и компаратор, причем первый вход компаратора соединен с второй клеммой для подключения объекта контроля и с первым входом аналогового запоминающего блока выходного напряжения логического нуля и первым входом аналогового запоминающего блока выходного напряжения логической единицы, второй вход компаратора соединен с выходом аналогового запоминающего блока выходного напряжения логической единицы, третий вход - с выходом аналогового запоминающего блока выходного напряжения логического нуля, выход компаратора соединен с входом блока управления, второй выход блока управления соединен с вторым входом аналогового запоминающего блока выходного напряжения логической единицы, третий выход блока управления соединен с BTopbw входом аналогового запоминающего блока выходного напряжения логического нуля, четвертый выход - с вторым входом селектора, пятый выход - с вторым входом дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи-воспроизведения кода времени | 1985 |

|

SU1269183A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ В ЛИНИЮ СВЯЗИ | 2006 |

|

RU2313914C1 |

| Программируемый источник питания | 1988 |

|

SU1597875A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362175C2 |

| Установка для акустико-эмиссионного контроля | 1986 |

|

SU1452316A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

Изобретение относится к технике измерения статических параметров интегральных микросхем Цель изобретения - повышение быстродействия измерителя. Измеритель содержит источник 1 двухполярного линейно изменяющегося напряжения, селектор 3, дешифратор 5, цифровой индикатор 6, буферный блок 7 и 8 управления. Введение аналоговых запоминающих блоков 10 и 11 выходного напряжения логических 1 и О, компаратора 12 и образование новых функциональных связей повьппает частоту работы тактового генератора 2 и ускоряет перестройку счетчика 4 в процессе цикла измерений. 1 ил. с сл

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Автоматический измеритель пороговых напряжений логических схем | 1974 |

|

SU526833A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-02-07—Публикация

1985-08-08—Подача