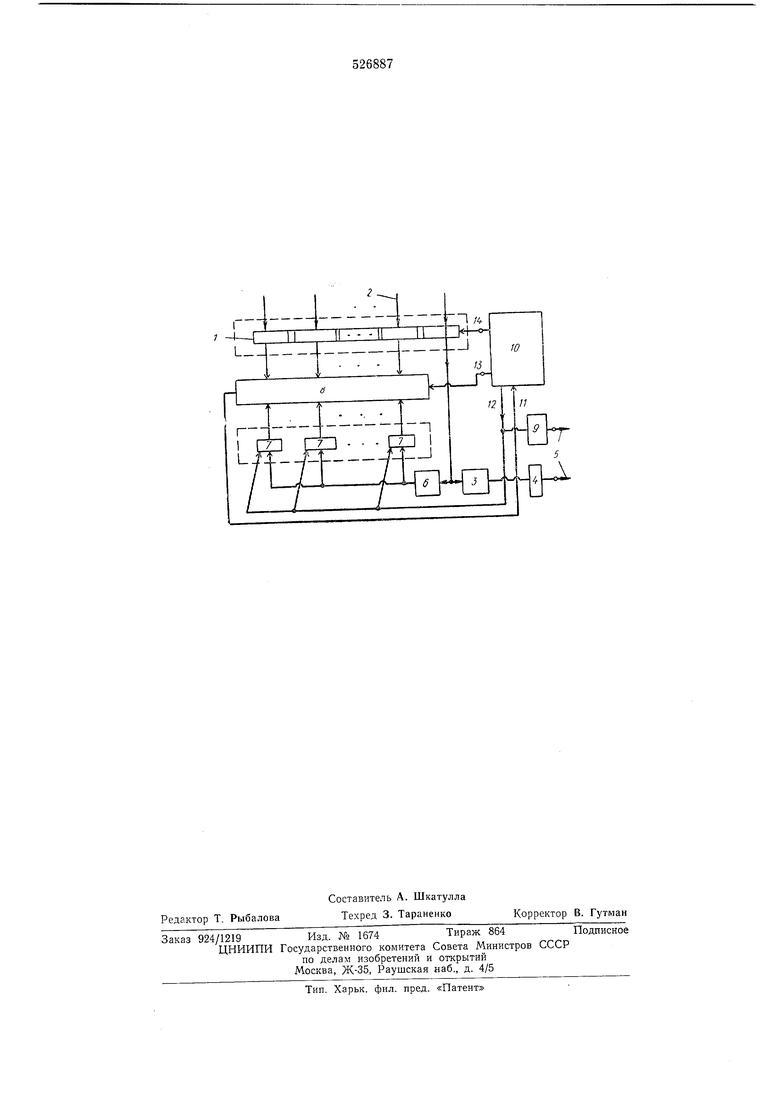

шины 5, блок 6 начальных условий, блок сдвигойых регистров 7, блок 8 срависния, счетчиж 9, блок. 10 удравлення с .входо.м И л выхюда ми 12, 13 и 14.

Входиой регистр 1 предяазкачен для фиксации числа Л, дредставлбнного в СОК озонми вычетами по основанижм РЬ Р-2,---,Рп В коде «1 из т {/1 {а,, сс2, . . . , а,, } где «i rest Л (mod Pi). Регистр / разбит иа п секций. Каждая секция иреднаЗ|Пачеда для фиксации одиого разряда кода СОК, т. е. для фи1ксации одного вычета по основа.иию РЬ и имеет Pi входов (для приема о;; в коде «1 из Pi и Pi 1ВЫХ01ДОВ. Выходы регистра иоразрядпо иодсоединепы к иервым ииформацио;:1ным входам блока араакения 8, иричем выход Каждого регистра подключен к Pi инфорМациЮНиым входа:М блока 8. Выход секции регистра, фиксирующей вычет ио осиованию РП 2 (где /г 1, 2, 3 . ..), имеет РП шин, которые подсоедцнеиы IK входа.м преобразователя 3 кода «1 из т ,в двоичный код и блока 6 иачальиых условий.

Преобразователь кода «1 из /п в двоичиый код служит для цреоб|разоваиия вьгчета числа А по oc; OiBaiHmo /-,, 2, представленлого в коде «1 из Р„, в двоичный код и может быть реализован па основе блока востояьгной памяти емкостью в РП слов, Имеющего РП входов и k выходов. Выходы цреобразователя 3 подсоедннеды к входам регистра 4, выходы которого подключены к выходным ииформационпым шииам 5 съема k младших разрядов искомого двоичяого кода.

Блок лачальиых условий лредназвачен для задания начальных условий на сдвиговые saiMiKiiyTbie регистры 7. Блок 6 МОжет быть реализовав на основе блока лостоЯНной памяти е М Костью в РП слов, имеющего Р„ входов и (PI+Р2 + - + -Pn-i) выходов. Выходы бло«а 6 лодразделяются ла (п-1) группу, и выходы ка.ждой груплы людсоедиляются к ипф ор м а ЦП 01Н,п ы;м в хо д ам со о тв е тс тв у ю щ е г о сдвигового регистра 7.

Блок сдвиго вых регистров 7 иредиазначеи для генерации чисел с щагом, равным Р„, причем генерируе1мые числа представлены в СОК. В состав блока входят п-1 сдвиговых замишутых регистров, функционирующих в коде 1 из Pi, ц формирование очередного числа в СОК сводится к одной операции сдвига, лроводимой одловре-мелно па каждом из регистров 7, причем на регистре сдвиг лроизводится та /,- Р„-Pi разрядов. Каждый из п-1 регистров Имеет Pi входов и Р, выходов, лричем выходы регист1ров лодсоединень к вторым И1нфор1мацио1Н)КЫ|М входам блока сраинения. У п ра1влбние блоком сдвиговых регистров лроизводится ло улравляющему входу, подсоединенно1му к первому .выходу 12 блока уцравлания 10. При лодаче сигнала на управляющий вход ,на каждом из perncTipoB 7 производится сдвиг на Ц разрядов.

Блсяк сраинелия 5 лредназначен для сравнения исходного числа Л, зафиксированного

па регистре /, и числа, сфор.мированного ;ia регистрах 7. Блок 8 лмеет две группы ип форМациониых в.ходов по . . . +Р „входов в каждой грулле, управляющий выход и управляющий вход и может быть реализован иа элементах «И и «ИЛИ. Первая груила илформалиоллых входов блока 8 подсоединена к вы.ходам входного регистра /, вторая группа - к информационным выходам бло1ка сдвиговых регистров, управляющий выход подключен к входу // блока управления 10, а улравляюлдйй вход подключен к второму выходу 13 блока управления. При равенстве кодов, зафиксированных на регистрах, сигнал, .подаваемый на вход блока сравнения, проходит иа его выход. В случае же, когда коды на регистрах / и 7 пе равны, сигнал, подаваемый .на вход блока 8, па его выход не проходит.

Счетчик 9 предназначен для лодсчета импульсов, подаваемых иа управляющий вход .блока сдвиговых регистров, и его вход подсоеди1нен к nepiBOMy выходу 12 блока управления 10, а ВЫХО.Д - к выходным информационным шина.м 5 съема старших разрядов noKOiMoro двоичного кода.

Блок управления 10 имеет три выхода 12, 13, 14 и один вход 11. Па выходы 12, 13, 14 от бло.ка управления соответстве.нно поступают следуюшие сигиалы: сигналы сдвига, подаваемые на управляющий вход блока сдвиговых регистров; сигналы о.проса, подаваемые на управляющий вход блока сравиения; сигнал считывания с регистра 1 вычета числа Л ло основанию РП 2. Па вход // блока управления с управляющего выхода блока сравнения 8 подается сигнал об окончании перевода.

Работает устройство следующим образом. Число Л I с .ь «2- . ., «-„ 1, лредставленлое в СОК своими вычетами а rest Л (mod Р,-) ло основаивям Р, р2, . . . , РП, которое тре.буется преобразовать в двоичный код, поступает на шины 2 и фиксируется на регистре / .в коде «1 из PJ. Первым имлульсо м, лода.ваемым от блока управления ло выходу М, .произво.дится считывание вычета а„ с регистра / (а„-вычет числа Л ло основанию Р„ 2). Считанный вычет а„ лреобразуется преобразователем кода из кода «1 из Р в двоичный .код, предста.вляющий собой k младших двоичных разрядо.в искомого двоичного числа Л.

Действительно, ос„ гез1Л (mod 2-) rest (Ло + Л) mod2 Ль где AI - часть двоичного кода, содержа.щая k младших двоичных разрядов числа Л; Ад - часть двоичного кода числа Л, содержащая старшие двоичнью разряды, начиная с А+1-го разряда; так ка;к Л о делится на У без остатка, а , то rest Л (mod 2) Л

Считанное a,i, поми.мо лреобразователя 5 подается в ядаде «1 из Р„ на блок 6 начальных условий, хранящий в постоянной памяти 2 векторов в СОК .вида В ,2,..., P«-i}.

Каждый .вектор В представляет собой набор вычетов по ослованпЯМ Р, РЧ, ... ,Рп-, который соответствует наиме-ньше.му числу из диапазоиа (О, PI х Рг х . . . х PJ, имеющему своим вычетом а„ .по основанию Я„ 2. После Выборки из блока 6, вектор В фиксируется на регистрах 7, причем каждый вычет фиксируется на соответствующем регистре в коде «1 из PI.

(После фиксации вектора В па регистрах 7 подачей импульса по выходу 13 производится первый опрос блока сра.В1Нбиия. Если код иа регистре 1 со.впадает с ко.дом на регистрах 7, импульс, пройдя бло.:К рра(Вне.ния, фиксирует окончание перевода. Если содержимое регистра / не совпадает с содержимым регистров 7, импульс опроса не пройдет через бло.к сравнения и блок управления .начнет .выдавать импульсы п:о (Выходам 13 и 12 ,с иекоторым сдвигом во времени.

Каж.ды.м очередным кмнульсом, подавае.мым по .выходу 13, производится опрос блока сравнепия, а каждым очередным импульсом, подаваемым от блока управления по выходу 12, произ1во.дится формирование нового числа иа регистрах 7. Формироваиие нового числа сводится К прнба влению величины Рп к каждому вычету ccj по модулю Pi. Операция сложения ПО 1модулю Р,-. реализуется сдвигом на i-M регистре на Р„-Р.; разрядов. Количество имиульсов сдвига (операций сложения) фиксируется счетчиком 9.

МОМеит окончания перевода (исходное число, зафиксировайьное на регистре /, созиало ио .величине со сфор.мирова.пиым числом на регистрах 7) фиксируется блоком сравнения - импульс оцроса, подаваемый по выходу 13, пройдет блок сравиения и поступит на блок управления.

По о.кончании перевода на регпстре 4 зафиксированы младшие k разрядов искомого двоичного кода, а счетчик фиксирует сколько раз в исходном числе содержится величина 2, т. е. счетчиком -фиксируются старшие разряды искомого двоичного кода.

Та.ким образом, введе.ние в устройство блока замкнутых сдвиговых регистров, блока начальных условий и преобразователя кода «1 из т в двопчный код поз воляет существенно увеличить коэффициент использования оборудования устройства за счет исключения запоминающего блока, хранящего полный набор кодов второй информационной системы.

Эффективность предлагаемого устройства видна на следующем К0нкрет1но.,м примере:

если, например, имеется три основания СОК Pi 15, , , то использованием двух сдвиговых .кпнутых регистров, преобразователя кода «1 из «16 iB двоичный код, содержащего в постоянной памяти 16 четырехразрядных двоичных слов, и блока начальных услО|Вий, содержащего в постоянной памяти 16 тридцатидвухразрядиых двоичных слов, удается исключить из устройства зан.оминающнй блок для хранения 4080 щестнадцат ;раз1рядных двоичных слов, чем достигается увеличение коэффициента использования оборудования. Среднее время иреобразования кодов из СОК в двоичный .код предлагаемым преобразователем равно времени выполнения 130 оиерацпй .сдвига, реализуемых блоком сдвиговых регистров.

Формула изобретения

Преобразователь кодов из систе-мы остаточных классов в позиционный код, содержащий входной регистр, входы которого подключе.ны к входным информационным шинам, а выходы всех разрядов, кроме .иервого, соедине.ны с первой группой информационных входов блока .сравнения, блок управления, счетчик и выходной регистр, выходы которых соединены с выходны:ми информационными шинами, о т л и чающийся тем, что, с целью увеличения коэффициента и.спользования оборудования, в него дополнительно введены блок СДВИГОВЫХ регистров, блок начальных условий и преобразователь кода е.дииицы из т в двоичный код, выход которого соединен с входом выходного регистра, а вход соединен с выходом первого разряда входашго регистра и входом блока начальных усло.вий, выход которого соединен с информационны.м входом блока регистров сдвига, управляющий .вход которого соединен с первым выходом блока управления, а информационные выходы подключены к второй группе информационных входов блока сравнения, управляющий выход которого соединен с входом блока управления, а управляющий вход - с вторым выходом блока зп.равления, третий выход которого подключен .к управляющему входу входного регистра, а вход счетчика соединен с первым выходом блока управления.

Источники информации, принятые во вппмание при экспертизе.

1.Авт. св. .YO 328448, G 06 F 5/02, 19.06.70.

2.Патент Японии ° 48-18666, кл. 97/7/С, 1971.

II - -11 пI --

; 4-Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1974 |

|

SU525947A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД | 2013 |

|

RU2513915C1 |

| Преобразователь кода из системы остаточных классов в двоичный код | 1980 |

|

SU947850A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД | 2008 |

|

RU2409840C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1981 |

|

SU1005028A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1980 |

|

SU959062A1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| Преобразователь полиадического кодаВ КОд СиСТЕМы ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU809154A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

Авторы

Даты

1976-08-30—Публикация

1974-12-16—Подача