1

Изобретение относится к области радиоэлектроники и может найти применение при построении цифровых измерителей интервалов времени.

Известен временной селектор целых импульсов, содержащий два триггера с раздельными потенциальиыми входами, причем входы первого из триггеров соединены соответственно с источниками селектируемого и стробирующего сигналов, а выход - с одним из входов второго триггера, выход которого подключен к инвертору.

С целью обеспечения работы селектора при любых величинах выдержек между селектируемым и стробирующим сигналами предлагаемый вре.менной селектор целых импульсов между селектируемым и стробирующим сигналами введены линия задержки и логическая схема умножения, при этом сигнальный вход первого триггера подсоединен к одиому из входов логической схемы умножения иепосредственно, к другому входу которой подключен выход инвертора, и через линию задержки-к другому входу второго триггера, а выход логической схемы умножения является выходом селектора.

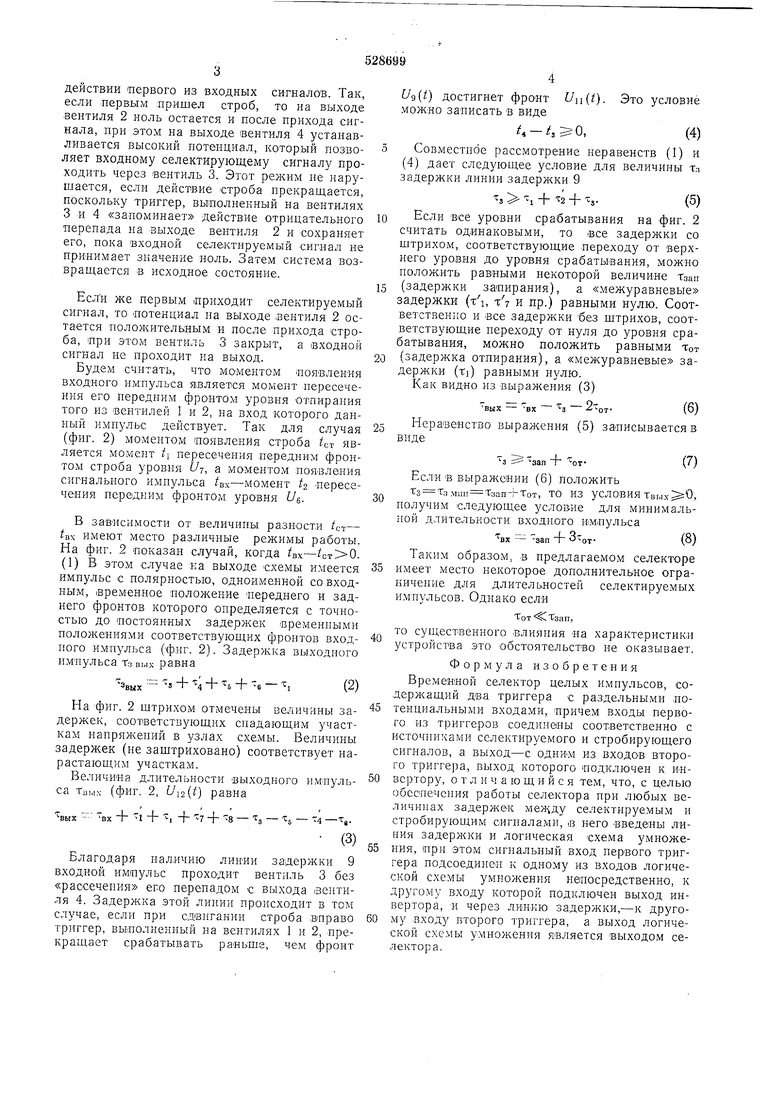

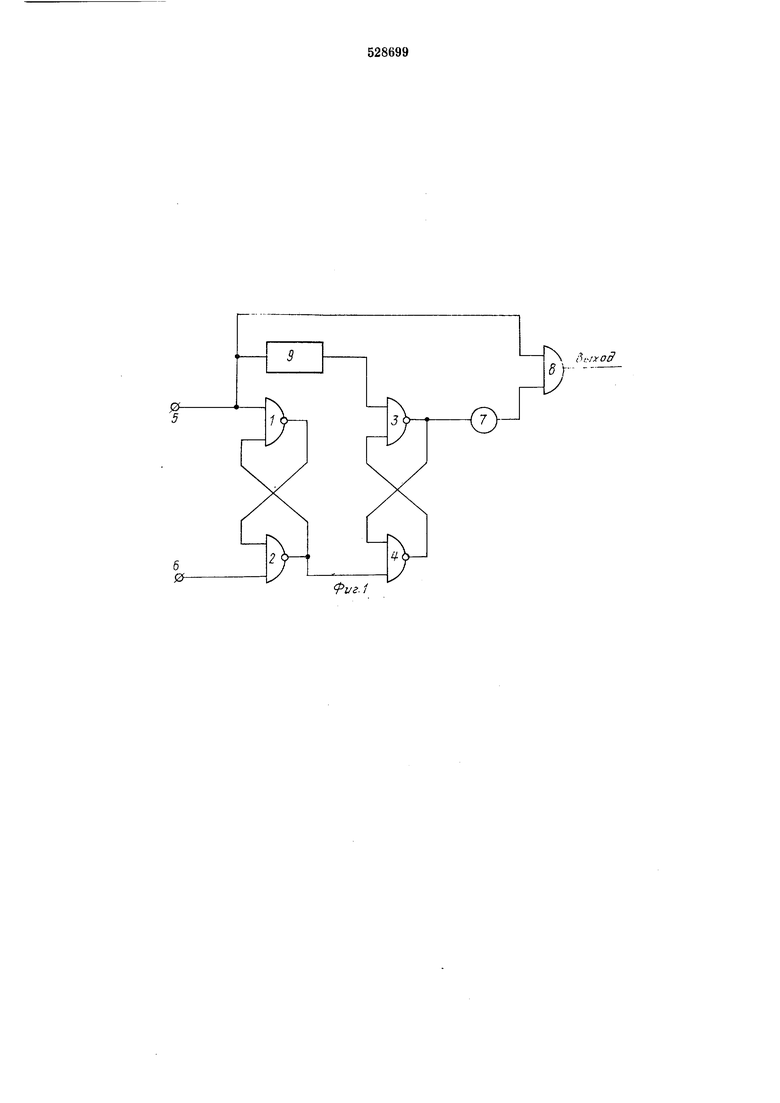

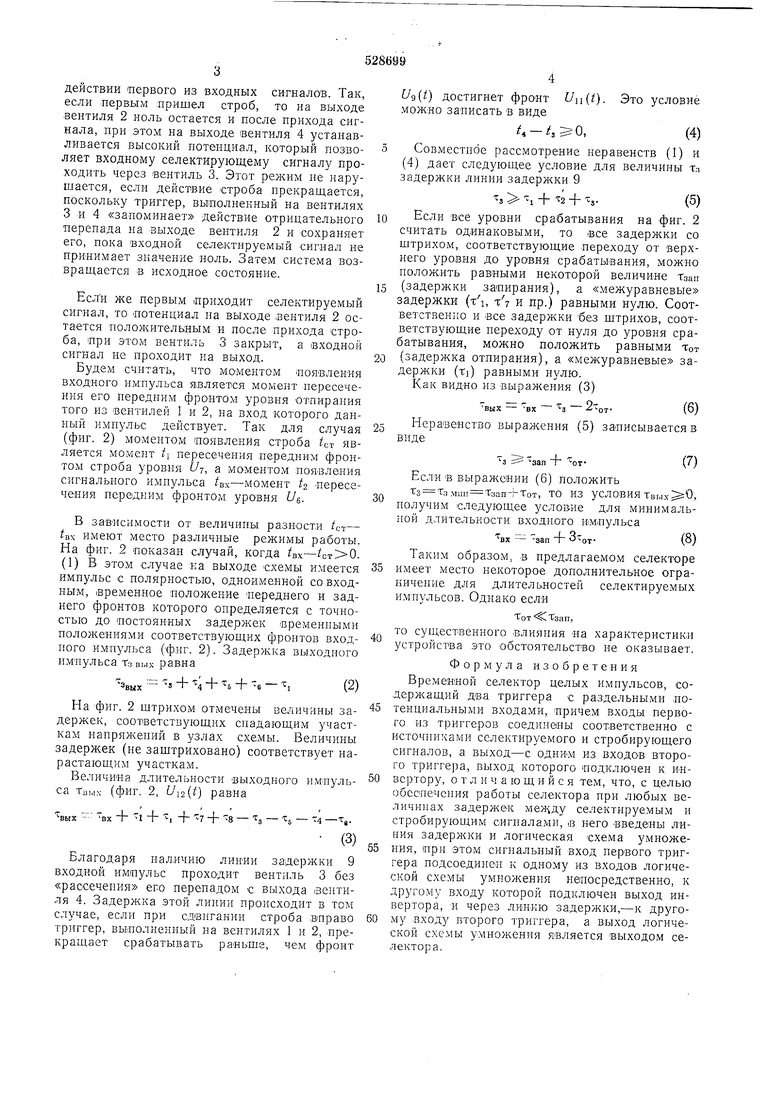

На фиг. 1 представлена функциональная схема предлагаемого временного селектора целых импульсов; на фиг. 2-временные диаграммы, поясняющие его работы.

Предлагаемый временной селектор целых импульсов содержит два триггера на вентилях 1, 2 и 3, 4, причем один из входов первого триггера соединен с источником 5 селектируемого сигнала, а другой вход-с источником 6 стробирующего сигнала. Выход первого триггера соединен с одним из входов второго тр.иггера, выход которого соединен с входом инвертора 7. Сигнальный вход первого триггера, выполненного на вентилях 1 и 2, соединен с одним из входов логической схемы умножения 8 и через линию задержки 9-с другим входом второго триггера, выполненного на вентилях 3 и 4. Выход инвертора 7 подключен к другому входу логической схемы умножения 8, выход которой является выходом селектора.

Работает предлагаемый селектор следующим образом.

При отсутствии сигнала на входах селектора на выходах вентилей 1 и 2 и на выходе вентиля 3 имеются высокие потенциалы.

При поступлении на какой-либо из входов триггера, выполненного на вентилях 1 и 2, входиого сигнала (селектируемого или строба) происходит переключение соответствующего вентиля 1 или 2 в низковольтное состояние. После прихода обоих входных сигналов триггер, выполненный на вентилях 1 и 2, остается в состоянии, которое возникает при

действии первого из входных сигналов. Так, если первым пришел строб, то на выходе вентиля 2 ноль остается и после прихода сигнала, при этом на выходе вентиля 4 устанавливается высокий потенциал, который позволяет входному селектирующему сигналу проходить через вентиль 3. Этот режим не нарушается, если действие строба прекращается, поскольку триггер, выполненный на вентилях 3 и 4 «запоминает действие отрицательного перепада на выходе вентиля 2 и сохраняет его, пока входной селектируемый сигнал не принимает значение ноль. Затем система возвращается в исходное состояние.

Если же первым приходит селектируемый сигнал, то потенциал на выходе вентиля 2 остается положительным и после прихода строба, при этом вентиль 3 закрыт, а 1входной сигнал не проходит на выход.

Будем считать, что моментом появления входного импульса является момент пересечения его передним фронтом уровня отпирания того из вентилей 1 и 2, на вход которого данный импульс действует. Так для случая (фиг. 2) моментом появления строба ст является момент ч пересечения передним фронто.м строба уровня Uj, а моментом появления сигнального импульса гвх-момент /2 пересечения передним фронтом уровня U.

В зависимости от величины разности /ст- имеют место различные режимы работы. На фиг. 2 показан случай, когда . (1) В этом случае на выходе схемы имеется импульс с полярностью, одноименной со входным, временное положение переднего и заднего фронтов которого определяется с точностью до постоянных задержек временными положениями соответствующих фронтов входного импульса (фпг. 2). Задержка выходного импульса Тзвых равна

ЗБЫХ 5 + 4 + 5 + б - 1(2)

На фиг. 2 штрихом отмечены величины задержек, соответствующих спадающим участкам напряжений в узлах схемы. Величины задержек (не заштриховано) соответствует нарастающим участкам.

Величина длительности выходного импульса Гвых (фиг. 2, Ui2(t) равна

внх - вх + 1 + 1 + 7 + - 3 - 5 - 4 -Те (3)

Благодаря наличию линии задержки 9 входной импульс проходит вентиль 3 без «рассечения его перепадом с выхода аентиля 4. Задержка этой линии происходит в том случае, если при сдвигании строба вправо триггер, выполненный на вентилях 1 и 2, прекращает срабатывать раньше, чем фронт

Ug(t) достигнет фронт Uii{t}. Это условие можно записать в виде

25 О,(4)

Совместное рассмотрение неравенств (1) и (4) дает следующее условие для величины тл задержки линии задержки 9

3 + 2 + ,.(5)

Если все уровни сра батывания на фиг. 2 считать одинаковыми, то все задержки со штрихом, соответствующие переходу от верхнего уровня до уровня срабатывания, можно положить равными некоторой величине Тзап

(задержки запирания), а «межуравневые задержки (ть т и пр.) равными нулю. Соответственно и все задержки без штрихов, соответствующие переходу от нуля до уровня срабатывания, можно положить равными Тот

(задержка отпирания), а «межуравиевые задержки (TI) равными нулю. Как видно из выражения (3)

вых - вх от-(w

Неравенство выражения (5) записывается в

виде

з аап + от-(7)

ЕСЛИ В выражении (6) положить

Тз Тз М1Ш Тзап-ЬТот, ТО ИЗ уСЛОВИЯ ,

получим следующее условие для минимальной длительности входного импульса

зап + (8)

Таким образом, в нредлагаемом селекторе имеет место некоторое дополнительное ограничение для длительностей селектируемых импульсов. Однако если

TOT Тзап,

ТО существенного влияния на характеристики устройства это обстоятельство не оказывает.

Формула изобретения Временной селектор целых импульсов, содержащий два триггера с раздельными потенциал ными входами, причем входы первого из триггеров соединены соответственно с источниками селектируемого и стробирующего сигиалов, а выход-с одним из входов второго тригге 1а, выход которого подключен к инвсртору, отличающийся тем, что, с целью обеспечения работы селектора при любых величинах задержек селектируемым и стробирующим сигнала.ми, в него введены линия задержки и логическая схема умножения, при этом сигнальный вход первого триггера подсоединен к одному из входов логической схемы умножения иеиосредственно, к другому входу которой подключен выход инвертора, и через линию задержки,-к другому входу второго триггера, а выход логической схемы умножения является выходом селектора.

б .

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по периоду следования | 1976 |

|

SU660223A1 |

| Устройство для выделения и анализа R-зубцов электрокардиосигнала | 1986 |

|

SU1364298A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ПЕРИОДУ СЛЕДОВАНИЯ | 2009 |

|

RU2415509C1 |

| Селектор периодических импульсных последовательностей | 1984 |

|

SU1195440A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

| СЕЛЕКТОР ИЛ\ПУЛЬСОВ | 1971 |

|

SU305575A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ПЕРИОДУ СЛЕДОВАНИЯ | 1993 |

|

RU2073953C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ПЕРИОДУ ПОВТОРЕНИЯ | 1994 |

|

RU2107386C1 |

| Временной селектор видеоимпульсов для дальномера | 1982 |

|

SU1070495A1 |

| Селектор пар импульсов | 1979 |

|

SU813740A1 |

Авторы

Даты

1976-09-15—Публикация

1973-07-13—Подача