Изобретение относится к области импульсной техники, в частности к селекторам по периоду следования, и может быть использовано в аппаратуре полуактивных головок самонаведения для выделения сигналов на фоне помех.

Известен селектор (патент №2073953, кл. Н03К 5/26 от 04.11.93 г.), содержащий последовательно соединенные блок выделения первого импульса, первый элемент «НЕ», первый элемент «ИЛИ», элемент задержки, первый формирователь строба, второй элемент «ИЛИ», первый и второй элементы «И», последовательно соединенные схему перезапуска, счетчик непопаданий, счетчик попаданий, второй элемент «НЕ», второй формирователь строба и третий элемент «ИЛИ», а также устройство регулируемой задержки. Выход блока выделения первого импульса соединен со вторыми входами формирователя стробов и блока перезапуска, выход первого элемента «НЕ» соединен со вторым входом второго элемента «ИЛИ», выход первого формирователя стробов соединен с третьим входом схемы перезапуска, выход второго элемента «ИЛИ» соединен со вторыми входами счетчика попаданий и устройства регулируемой задержки, выход первого элемента «И» соединен с третьими входами счетчика попаданий и схемы регулируемой задержки, первыми входами схемы перезапуска и блока выделения первого импульса и вторыми входами счетчика непопаданий и первого элемента «ИЛИ». Выход схемы перезапуска соединен с первыми входами счетчика непопаданий и блока выделения первого импульса. Выход счетчика попаданий соединен с четвертым входом схемы перезапуска, первым входом устройства регулируемой задержки и вторым входом второго элемента «И». Выход устройства регулируемой задержки соединен со вторым входом второго формирователя стробов, а выход третьего элемента «ИЛИ» - со вторым входом второго элемента «И».

Недостатком рассмотренного селектора является то, что первый принятый импульс может не принадлежать к искомой последовательности. При этом ни один из полезных импульсов не попадает в заданный интервал и процесс поиска повторяется. Вероятность появления первым импульса из искомой последовательности резко уменьшается при наличии во входном сигнале, кроме помех, последовательностей импульсов, периоды повторения которых близки к заданному. Так, при наличии в спектре входного сигнала N последовательностей вероятность прихода первым импульса из искомой последовательности Р=1/N невелика, что может привести к недопустимо большой длительности процесса поиска последовательности импульсов с заданным периодом повторения.

Наиболее близким по технической сущности к предлагаемому является селектор импульсов по периоду следования (авторское свидетельство №1758864, кл. Н03К 5/26), содержащий линию задержки, блок выделения первого импульса, три элемента «И», триггер, элемент «ИЛИ», элемент задержки, блок формирования стробов, пересчетный блок, причем блок выделения первого импульса, элемент «ИЛИ», элемент задержки, блок формирования стробов, третий элемент «И» соединены последовательно, выход третьего элемента «И» подключен к первому входу пересчетного блока, выходу селектора и вторым входам блока формирования стробов и элемента «ИЛИ», второй вход третьего элемента «И» соединен со входом селектора и первыми входами блока выделения первого импульса, первого элемента «И» и линии задержки, линия задержки, первый и третий элементы «И» соединены последовательно, выход триггера соединен со вторым входом второго элемента «И», а первый вход триггера - с выходом второго элемента «И» и третьим входом элемента «ИЛИ», четвертый вход элемента «ИЛИ» соединен с выходом элемента задержки, второй вход которого подключен ко вторым входам линии задержки, блока выделения первого импульса, триггера и выходу пересчетного блока, второй вход пересчетного блока соединен с выходом, а второй выход - с третьим входом блока формирования стробов. Линия задержки содержит генератор тактовых импульсов, второй и третий триггеры, счетчик импульсов, первый и второй запоминающие блоки и второй элемент ИЛИ, выход которого соединен с выходом линии задержки, а первый и второй входы - с выходами соответственно первого и второго запоминающих блоков, адресные входы которых поразрядно соединены с выходами счетчиков импульсов, входы управления режимом запись-считывание - соответственно с первым и вторым выходами третьего триггера, а информационные входы - с выходом второго триггера, вход установки которого соединен с первым входом линии задержки, второй вход которой соединен с входами сброса первого и второго запоминающих блоков и счетчика импульсов, счетный вход которого соединен с выходом генератора тактовых импульсов и входом сброса второго триггера, а выход переполнения - со счетным входом третьего триггера.

Данный селектор достаточно эффективен при наличии во входном сигнале до 5 последовательностей импульсов на близких частотах, что эквивалентно наличию в поле зрения головки самонаведения 5 облучаемых целей, четыре из которых являются источником помех. При увеличении количества одновременно присутствующих последовательностей импульсов до 16 плотность помех пропорционально увеличивается, что приводит к недопустимому увеличению вероятности ложной тревоги.

Задачей предлагаемого изобретения является повышение надежности функционирования селектора в условиях воздействия помех.

Указанная задача достигается тем, что в селектор импульсов по периоду следования, содержащий генератор, адресный счетчик, запоминающий блок, три триггера, последовательно соединенные первую и вторую схемы «И», третью схему «И», две схемы «ИЛИ» дополнительно введены последовательно соединенные счетчик интервалов дискретизации и первая схема сравнения, делитель частоты, управляемый делитель частоты, счетчик-дешифратор, счетчик периодов, вторая и третья схемы сравнения, сумматор, три триггера и четвертая схема «И», причем выход генератора соединен со входом делителя частоты и первыми входами управляемого делителя частоты и счетчика-дешифратора, второй вход которого соединен с выходом делителя частоты, выход управляемого делителя частоты соединен с первыми входами адресного счетчика, счетчика интервалов дискретизации, счетчика периодов, второго триггера и четвертой схемы «И», а также с вторым входом первой схемы сравнения, первый выход счетчика-дешифратора соединен с первыми входами сумматора и шестого триггера, второй его выход соединен со вторыми входами второй схемы «И», запоминающего блока, адресного счетчика и первого триггера, а третий выход - с первыми входами четвертого и пятого триггеров, выход запоминающего блока соединен со вторыми входами четвертого и шестого триггеров, выход первой схемы «И» дополнительно соединен с первыми входами третьей схемы «И» и запоминающего блока, третий вход которого соединен с выходом сумматора, второй вход которого соединен с выходом адресного счетчика, выход четвертого триггера соединен со вторым входом пятого триггера и первым входом первой схемы «ИЛИ», выход которой соединен с первым входом первой схемы «И», второй вход которой соединен с выходом первого триггера, выход второй схемы «И» соединен со вторым входом счетчика интервалов дискретизации, выход которого через вторую схему сравнения соединен со вторым входом четвертой схемы «И», выход которой соединен с первым входом третьего триггера, а третий вход - с выходом третьей схемы сравнения, выход второй схемы «ИЛИ» соединен со вторыми входами второго триггера и счетчика периодов, ее второй вход соединен с выходом первой схемы сравнения, а первый вход - является входом начальной установки, выход второго триггера соединен со вторыми входами третьего триггера и первой схемы «ИЛИ», третий вход которой соединен с выходом шестого триггера, а четвертый вход соединен с выходом пятого триггера, выход счетчика периодов соединен с первым входом третьей схемы сравнения, выход третьего триггера соединен со вторым входом третьей схемы «И», второй вход управляемого делителя частоты является входом кода селектируемой частоты, второй вход третьей схемы сравнения является входом кода числа периодов анализа, на третий вход первой схемы сравнения и второй вход второй схемы сравнения поступают коды чисел ноль и единица соответственно, первый вход первого триггера является входом селектора, а выход третьей схемы «И» является его выходом.

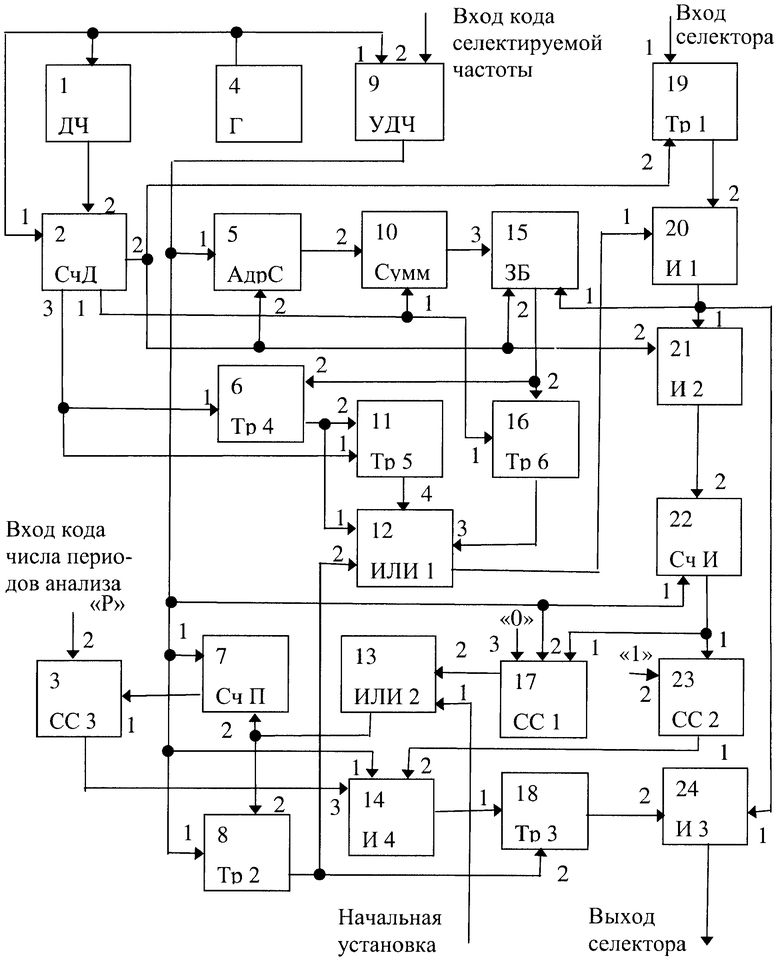

На чертеже приведена структурная электрическая схема селектора, где

1 - делитель частоты (ДЧ),

2 - счетчик-дешифратор (СчД),

3, 17, 23 - схемы сравнения (СС3, СС1, СС2 соответственно),

4 - генератор (Г),

5 - адресный счетчик (АдрСч),

6, 8, 11, 16, 18, 19, - триггеры (Тр4, Тр2, Тр5, Тр6, Тр3, Tp1 соответственно),

7 - счетчик периодов (СчП),

9 - управляемый делитель частоты (УДЧ),

10 - сумматор (Сумм),

12, 13 - схемы «ИЛИ» (ИЛИ1, ИЛИ2 соответственно),

14, 20, 21, 24 - схемы «И» (И4, И1, И2, И3 соответственно),

15 - запоминающий блок (ЗБ),

22 - счетчик интервалов дискретизации (СчИ).

Предлагаемое устройство работает следующим образом.

После подачи питания на устройство на соответствующих входах задастся код селектируемой литерной частоты и код числа периодов анализа. На третьем входе первой схемы сравнения 17 постоянно присутствует код нуля, а на втором входе второй схемы сравнения 23 - код единицы. Сигнал «начальная установка» через вторую схему «ИЛИ» 13 осуществляет сброс счетчика периодов 7 и устанавливает второй триггер 8 - в состояние «1». В свою очередь сигнал с выхода второго триггера 8 осуществляет сброс третьего триггера 18, запрещающего прохождение сигнала через третью схему «И» 24 на выход селектора, а также блокирует прохождение сигнала через первую схему «ИЛИ» 12. При этом на выходе ее постоянно присутствует логическая единица, разрешающая прямое прохождение сигнала с выхода первого триггера 19 на вход запоминающего блока 15 через первую схему «И» 20 - селектор импульсов находится в режиме накопления входных сигналов. Под воздействием импульсов с выхода генератора 4 на выходе управляемого делителя частоты 9 формируются импульсы с периодом повторения, равным периоду повторения селектируемых импульсов, а на выходе делителя частоты 1 - импульсы, определяющие интервал дискретизации входного сигнала селектора. Делитель частоты 1 формирует импульсы, перезапускающие счетчик-дешифратор 2. Счетчик-дешифратор 2 осуществляет счет импульсов генератора 4 по модулю 4, после чего счет останавливается. При этом наличие логической 1 на выходе 3 соответствует состоянию «0» счетчика 2, а наличие импульса на первом и втором его выходах - состоянию «1» и «2» соответственно. Задним фронтом импульсов со второго выхода счетчика-дешифратора 2, задержанным относительно импульсов с выхода делителя частоты 1, первый триггер 19 устанавливается в исходное состояние, а также изменяется состояние адресного счетчика 5, сигнал на выходе которого определяет базовый адрес ячейки запоминающего блока 15, подлежащей обработке. Абсолютный адрес для запоминающего блока 15 с учетом смещения, определяемого сигналом с первого выхода счетчика-дешифратора 2, формирует сумматор 10. Любой из импульсов, поступивший на вход селектора в интервале между импульсами сброса первого триггера 19, устанавливает его в состояние «1». Сигнал со второго выхода счетчика-дешифратора 2, предшествующий сбросу первого триггера 19, переписывает его состояние в ячейку запоминающего блока 15 по базовому адресу. Таким образом, в интервале между появлением импульсов переполнения на выходе управляемого делителя частоты 9 происходит заполнение ячеек запоминающего блока 15 отсчетами сигнала на входе селектора, причем в отсутствии сигнала записывается «0», а при наличии хотя бы одного импульса в интервале дискретизации - «1». Первый, при неактивном состоянии сигнала «начальная установка», импульс с выхода управляемого делителя 9 устанавливает триггер 8 в состояние «0», соответствующее нахождению селектора в режиме фильтрации. В этом режиме разрешается прохождение сигналов через первую схему «ИЛИ» 12, а сигнал, записываемый в ячейку запоминающего блока 15, определяется соотношением:

где D - сигнал, записываемый в запоминающий блок 15 в ячейку с базовым адресом;

I - состояние первого триггера 19 к концу интервала дискретизации;

Qn, Qn-1, Qn+1 - значение сигнала, записанного в запоминающем блоке в ячейку с базовым адресом, а также в смежных с ней ячейках в предыдущих циклах фильтрации сигнала;

Λ, V - символы логического умножения и сложения соответственно.

Учет значений сигналов в смежных с базовой ячейках запоминающего блока 15 позволяет избежать пропусков входного сигнала из-за неравенства частот заданной и поступающей на вход селектора последовательности импульсов при отсутствии синхронизации положения входного импульса относительно середины интервала дискретизации входного сигнала. При этом допустимое рассогласование частот может быть определено по соотношению:

где Тзад, Тс - заданный и поступающий на вход селектора периоды повторения входных импульсов;

Р - число периодов фильтрации входного сигнала, необходимых для достоверного обнаружения входного сигнала;

t - длительность интервала дискретизации входного сигнала.

Для определения состояния базовой и смежных ячеек запоминающего блока 15 в состоянии «0» счетчика-дешифратора 2 сигналом с выхода 3 счетчика-дешифратора 2 в четвертый триггер 6 переписывается содержимое ячейки запоминающего блока по базовому (n) адресу, а в пятый триггер 11 - содержимое четвертого триггера 6. Тем самым содержимое четвертого триггера 6 соответствует содержимому ячейки с номером n, а триггера 11 - содержимому ячейки с номером n-1, определенное в предыдущем интервале дискретизации. В состоянии «1» счетчика-дешифратора 2 сигналом с первого выхода счетчика состояний 2 в шестой триггер 16 переписывается содержимое ячейки с адресом n+1 запоминающего блока 15. В состоянии «2» счетчика-дешифратора 2 сигналом в ячейку с адресом n записывается фильтрованное по соотношению (1) значение входного сигнала, формируемое на выходе первой схемы «И» 20. При записи в запоминающий блок 15 логической 1 интервал дискретизации считается активным. В этом случае, одновременно с записью в запоминающий блок 15, инкрементируется счетчик интервалов дискретизации 22. Если к моменту возникновения импульса переполнения управляемого делителя частоты, являющегося стробирующим для первой схемы сравнения 17, состояние счетчика интервалов дискретизации 22 нулевое (физически это означает отсутствие на входе селектора импульсов заданной частоты) логическая 1 на выходе первой схемы сравнения 17 через вторую схему «ИЛИ» 13 осуществляет установку второго триггера 8 с перезапуском селектора.

По прошествии нескольких литерных периодов, подсчет которых производится счетчиком периодов 7, и при условии наличия в сигнале на входе селектора последовательности импульсов с периодом повторения, близким к заданному, логическая 1 останется только в одной ячейке запоминающего блока 15, содержимое счетчика интервалов дискретизации 22 будет равно 1, приводя тем самым к появлению логической единицы на выходе второй схемы сравнения 23. Если при этом содержимое счетчика периодов 7 повторения литерной частоты превышает Р (число периодов повторения, достаточное для достоверного анализа), на выходе третьей схемы сравнения 3 появляется логическая 1, импульс переполнения на выходе управляемого делителя частоты 9 осуществляет через четвертую схему «И» 14 установку третьего триггера 18 в состояние «1», разрешая тем самым в следующем периоде анализа прохождение импульса с выхода первой схемы «И» 20 через третью схему «И» 24 на выход селектора, информирующего о наличии на входе селектора импульсов с периодом повторения, близким к литерному. Прогнозируемое время появления следующего импульса - интервал дискретизации с номером, определяемым содержимым адресного счетчика 5 в момент появления выходного импульса селектора.

Предлагаемый селектор может быть реализован на микросхемах 533, 564 и 1638 серий, либо с использованием программируемых логических интегральных схем (ПЛИС). Счетчик-дешифратор 2 может быть выполнен на микросхеме типа 565ИЕ8 с укорочением цикла, в качестве триггеров 6, 11, 16, 19 могут быть использованы D-триггеры 564ТМ2, первая схема «ИЛИ» 12 может быть реализована на микросхеме 533ЛР13, вторая - на микросхеме 533ЛЕ1.

Математическое моделирование процесса обнаружения и результаты испытаний, проведенных для случая присутствия на входе селектора одновременно 32 последовательностей импульсов с периодами повторения, отличающимися друг от друга на 100 мкс, показывает, что надежное обнаружение достигается после 4-5 периодов фильтрации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Цифровой вольтметр среднеквадратического значения переменного напряжения | 1988 |

|

SU1652933A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| Электронные вторичные часы с цифровой индикацией | 1983 |

|

SU1170417A1 |

| Устройство для измерения мощности | 1990 |

|

SU1751685A1 |

| Селектор импульсов | 1979 |

|

SU849474A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

Изобретение относится к области импульсной техники, в частности к селекторам импульсов по периоду следования. Техническим результатом является повышение надежности функционирования селектора в условиях воздействия помех. Устройство содержит генератор, адресный счетчик, запоминающий блок, шесть триггеров, четыре схемы «И», две схемы «ИЛИ», счетчик интервалов дискретизации, три схемы сравнения, делитель частоты, управляемый делитель частоты, счетчик-дешифратор, счетчик периодов, сумматор. 1 ил.

Селектор импульсов по периоду следования, содержащий генератор, адресный счетчик, запоминающий блок, три триггера, последовательно соединенные первую и вторую схемы И, третью схему И, две схемы ИЛИ, отличающийся тем, что в него дополнительно введены последовательно соединенные счетчик интервалов дискретизации и первая схема сравнения, делитель частоты, управляемый делитель частоты, счетчик-дешифратор, счетчик периодов, вторая и третья схемы сравнения, сумматор, три триггера и четвертая схема И, причем выход генератора соединен со входом делителя частоты и первыми входами управляемого делителя частоты и счетчика-дешифратора, второй вход которого соединен с выходом делителя частоты, выход управляемого делителя частоты соединен с первыми входами адресного счетчика, счетчика интервалов дискретизации, счетчика периодов, второго триггера и четвертой схемы И, а также с вторым входом первой схемы сравнения, первый выход счетчика-дешифратора соединен с первыми входами сумматора и шестого триггера, второй его выход соединен со вторыми входами второй схемы И, запоминающего блока, адресного счетчика и первого триггера, а третий выход - с первыми входами четвертого и пятого триггеров, выход запоминающего блока соединен со вторыми входами четвертого и шестого триггеров, выход первой схемы И дополнительно соединен с первыми входами третьей схемы И и запоминающего блока, третий вход которого соединен с выходом сумматора, второй вход которого соединен с выходом адресного счетчика, выход четвертого триггера соединен со вторым входом пятого триггера и первым входом первой схемы ИЛИ, выход которой соединен с первым входом первой схемы И, второй вход которой соединен с выходом первого триггера, выход второй схемы И соединен со вторым входом счетчика интервалов дискретизации, выход которого через вторую схему сравнения соединен со вторым входом четвертой схемы И, выход которой соединен с первым входом третьего триггера, а третий вход - с выходом третьей схемы сравнения, выход второй схемы ИЛИ соединен со вторыми входами второго триггера и счетчика периодов, ее второй вход соединен с выходом первой схемы сравнения, а первый вход - является входом начальной установки, выход второго триггера соединен со вторыми входами третьего триггера и первой схемы ИЛИ, третий вход которой соединен с выходом шестого триггера, а четвертый вход соединен с выходом пятого триггера, выход счетчика периодов соединен с первым входом третьей схемы сравнения, выход третьего триггера соединен со вторым входом третьей схемы И, второй вход управляемого делителя частоты является входом кода селектируемой частоты, второй вход третьей схемы сравнения является входом кода числа периодов анализа, на третий вход первой схемы сравнения и второй вход второй схемы сравнения поступают коды чисел ноль и единица соответственно, первый вход первого триггера является входом селектора, а выход третьей схемы И является его выходом.

| Селектор импульсов по периоду следования | 1990 |

|

SU1758864A2 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ПЕРИОДУ СЛЕДОВАНИЯ | 1993 |

|

RU2073953C1 |

| RU 2059338 C1, 27.04.1996 | |||

| JP 62286310 A, 12.12.1987. | |||

Авторы

Даты

2011-03-27—Публикация

2009-09-07—Подача