1

Изобретение относится к области устройств, контролирующих наличие отпирающих импульсов на выходе системы управления статическими преобразователями.

Известны устройства для контроля системы управления преобразователей, в которых контролируется напряжение на переходе «катод - управляющий переход тиристора для обнаружения неисправности силовой части преобразователя (1).

Недостатком этих устройств является электрический контакт с силовой частью.

Известно также устройство для контроля системы управления трехфазного преобразователя, содержащее элементы памяти, соединенные через логические ячейки И с ячейкой ИЛИ. Однако это устройство недостаточно надежно.

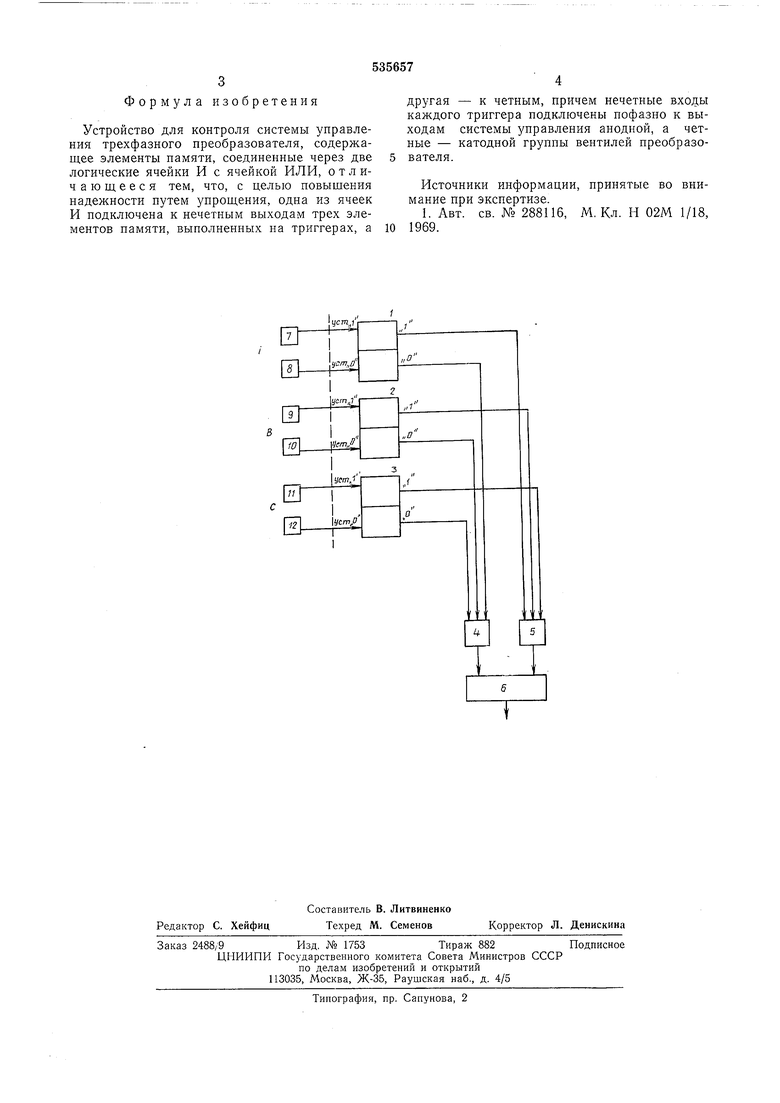

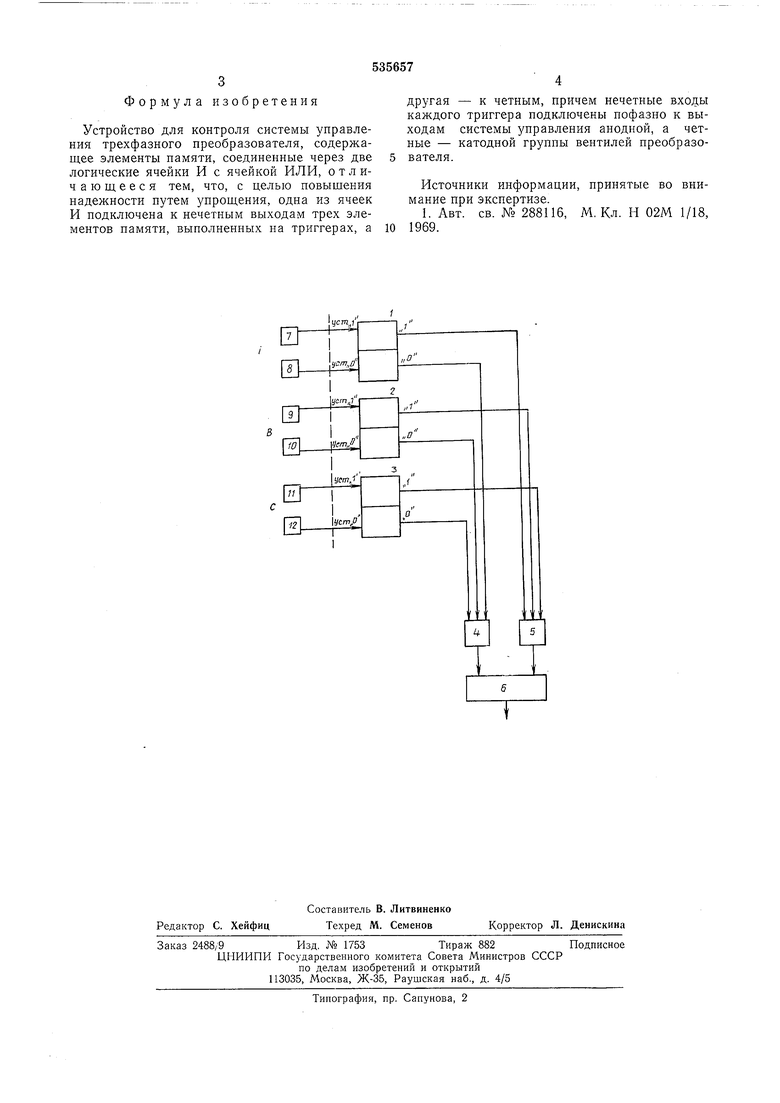

Для повышения надежности путем упрощения в предлагаемом устройстве одна из ячеек И подключена к нечетным выходам трех элементов памяти, выполненных на триггерах, а другая - к четным, причем нечетные входы каждого триггера подключены пофазно к выходам системы управления анодной, а четные - катодной групп вентилей преобразователя.

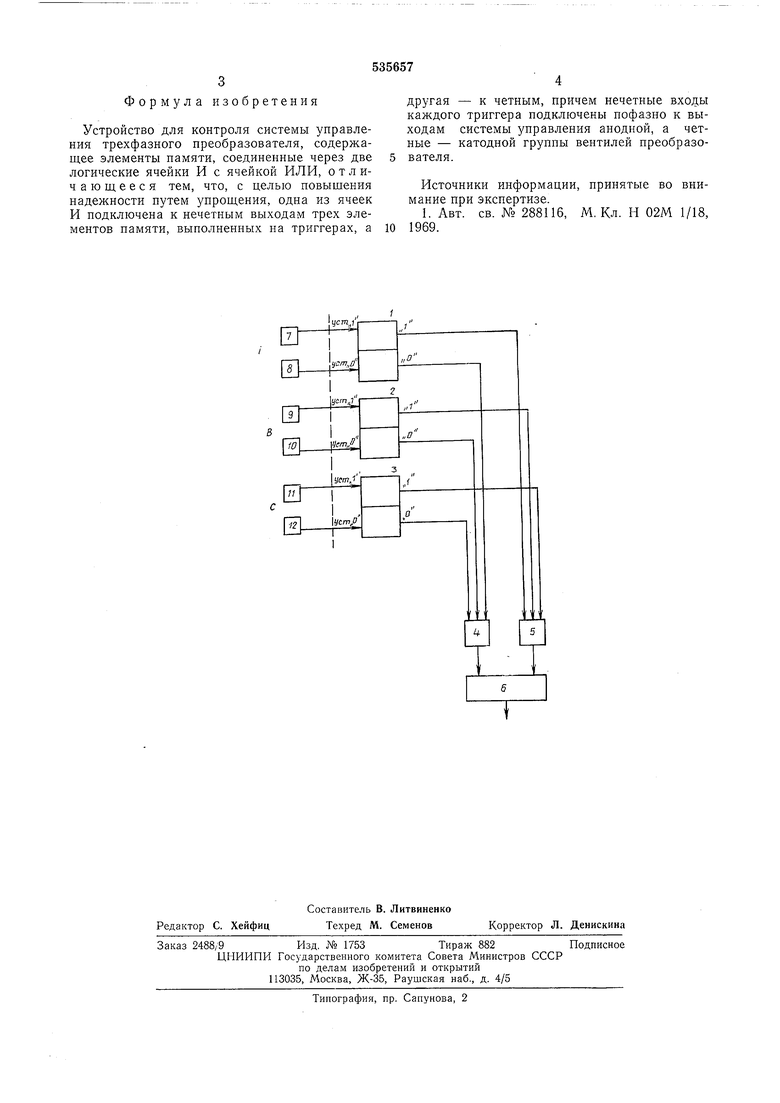

На чертеже представлена блок-схема описываемого устройства, содержап1,его три триггера 1, 2, 3с раздельными входами, логические схемы И 4 и 5, логическую схему ИЛИ

6, выходные элементы контролируемой системы управления 7-12.

Ири исправной системе управления на раздельные входы каждого из триггеров 1, 2, 3 поступают импульсы, сдвинутые на половину периода. Ввиду того, что управляющие импульсы на четных (уст. «О) и нечетных (уст. «1) входах сдвинуты на одну треть периода, сигнал на выходах схем И имеет вид прямоугольных импульсов равной длительности, сдвинутых на одну треть периода. В этом

случае ни в один из моментов времени на входы схем И не поступают одновременно сигналы, соответствующие трем логическим едииицам, и аварийный сигнал на выходе схемы ИЛИ 6 отсутствует.

Исчезновение сигнала, например, на выходе ячейки 7 фазы А, приводит к тому, что триггер 1 не перебрасывается, и на четном выходе триггера («О) остается высокий потенпиал, соответствующий логической единице. В результате этого на входах логической схемы 4 появляются сигналы, соответствующие трем логическим единицам, п на выходе устройства появляется аварийный импульс,

повторяюп1,ийся через перио/т,.

Формула изобретения

Устройство для контроля системы управления трехфазного преобразователя, содержащее элементы памяти, соединенные через две логические ячейки И с ячейкой ИЛИ, отличающееся тем, что, с целью повыщения надежности путем упрощения, одна из ячеек И подключена к нечетным выходам трех элементов памяти, выполненных па триггерах, а

другая - к четным, причем нечетные входы каждого триггера подключены пофазно к выходам системы управления анодной, а четные - катодной группы вентилей преобразователя.

Источники информации, принятые во внимание цри экспертизе.

1. Авт. св. № 288116, М. Кл. Н 02М 1/18, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля системы управления трехфазного статического преобразователя | 1986 |

|

SU1390696A2 |

| Устройство для контроля системы управления трехфазного преобразователя | 1989 |

|

SU1713012A1 |

| Статический возбудитель электрических машин | 1991 |

|

SU1786618A1 |

| Устройство для контроля системы управления трехфазным преобразователем | 1978 |

|

SU682978A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Устройство для отображения диаграммы хода балансовых часов | 1983 |

|

SU1170418A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| Устройство для управления трехфазным тиристорным преобразователем частоты | 1973 |

|

SU534843A1 |

| Преобразователь частоты с непосредственной связью | 1973 |

|

SU516160A1 |

Авторы

Даты

1976-11-15—Публикация

1972-02-02—Подача