Изобретеш1е относится к электротехнике, а именно к управлению вентильными преобразователямИд работаю- щиьда от сети переменного тока, с кс- пользованмем методов цифровой обра- ботки информации5 и может быть использовано в регулируемом электроприводе постоянного тока,

Целью изобретелшя является повышение надежности и устойчивости рабо- ты устройства.

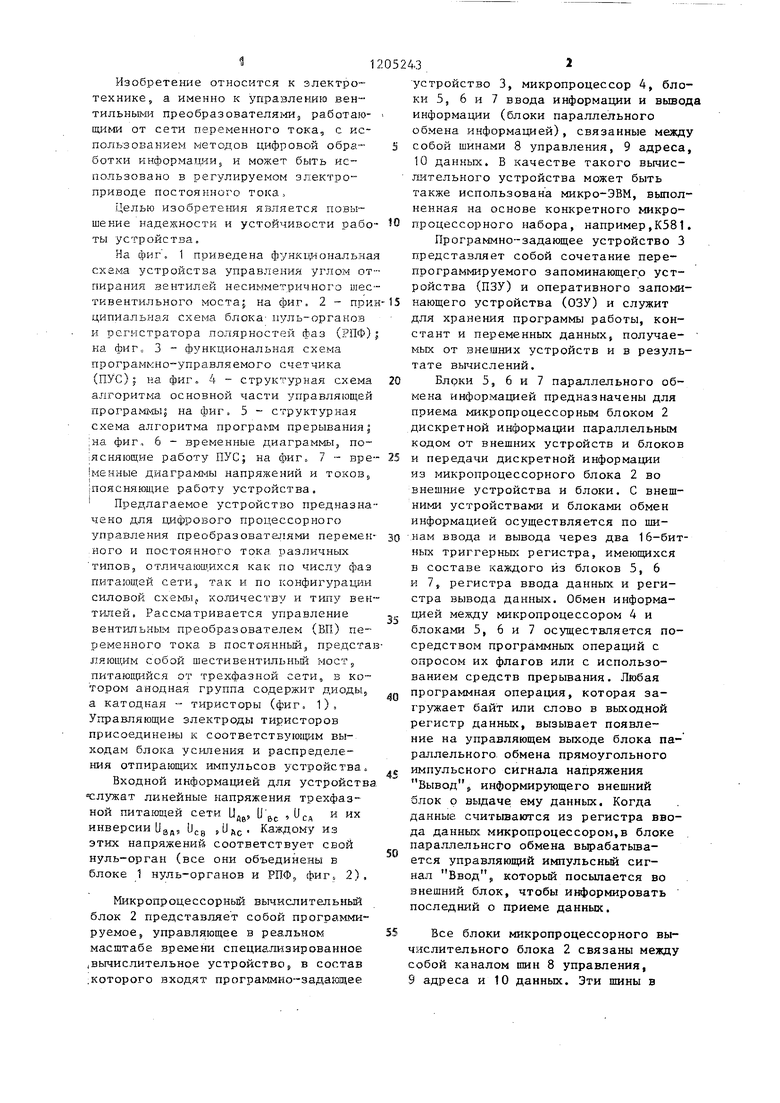

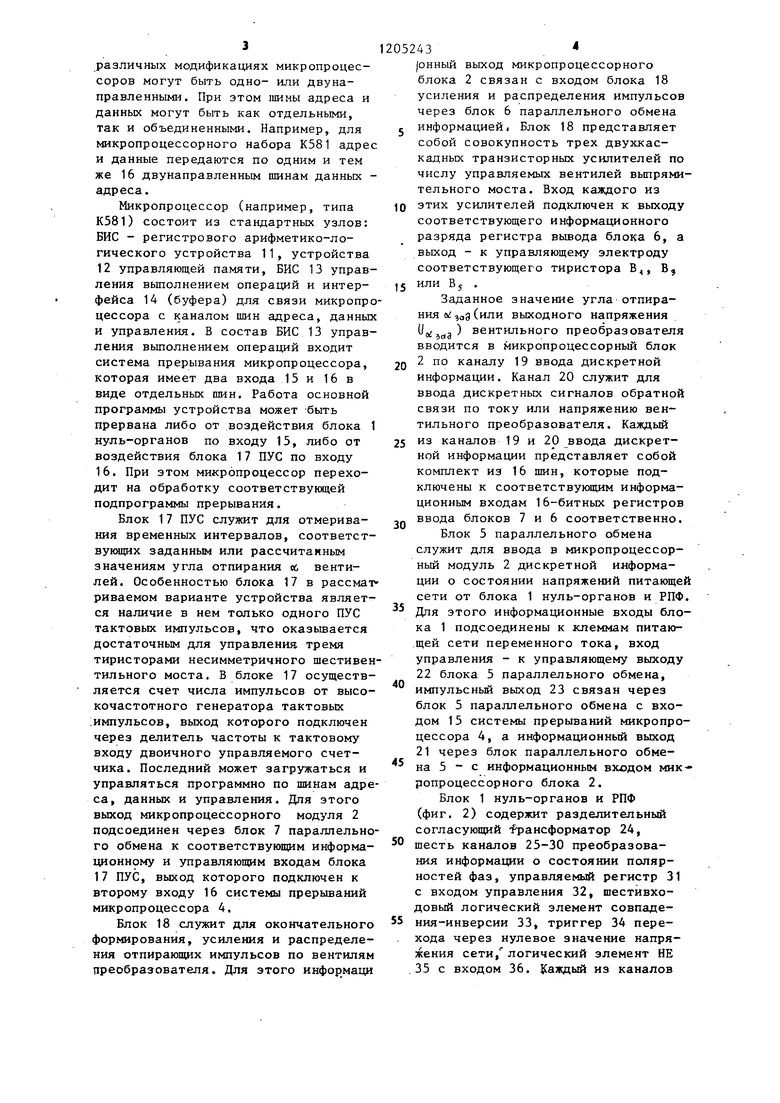

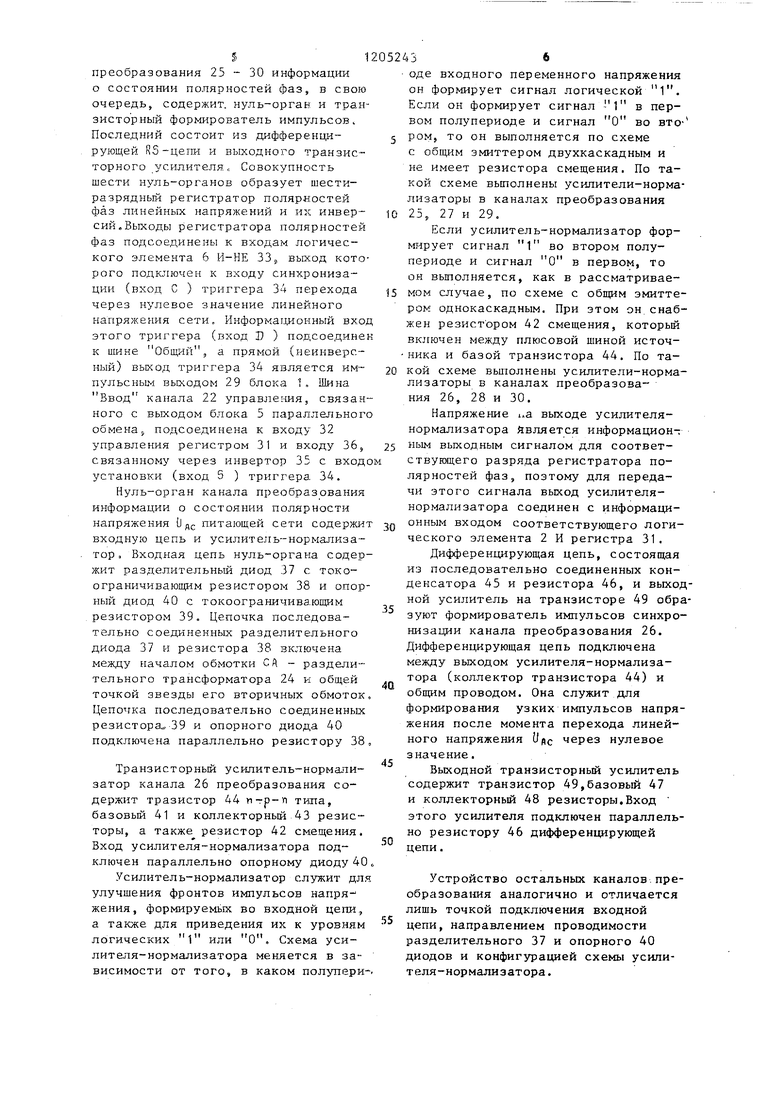

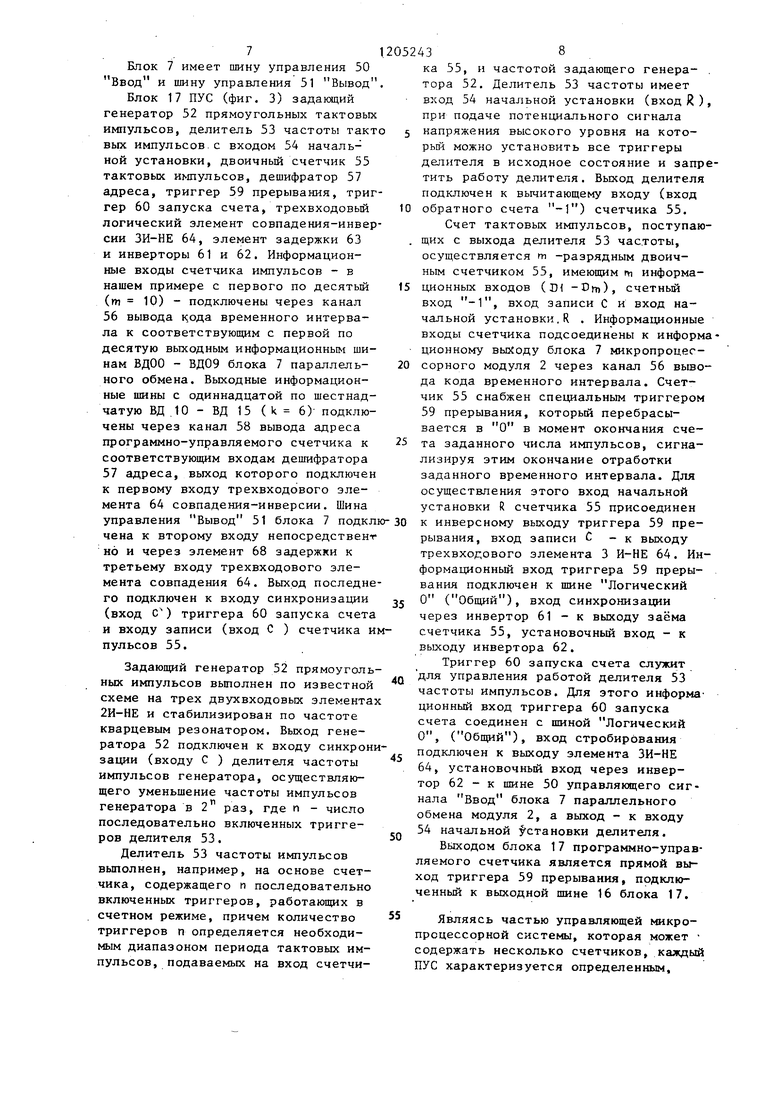

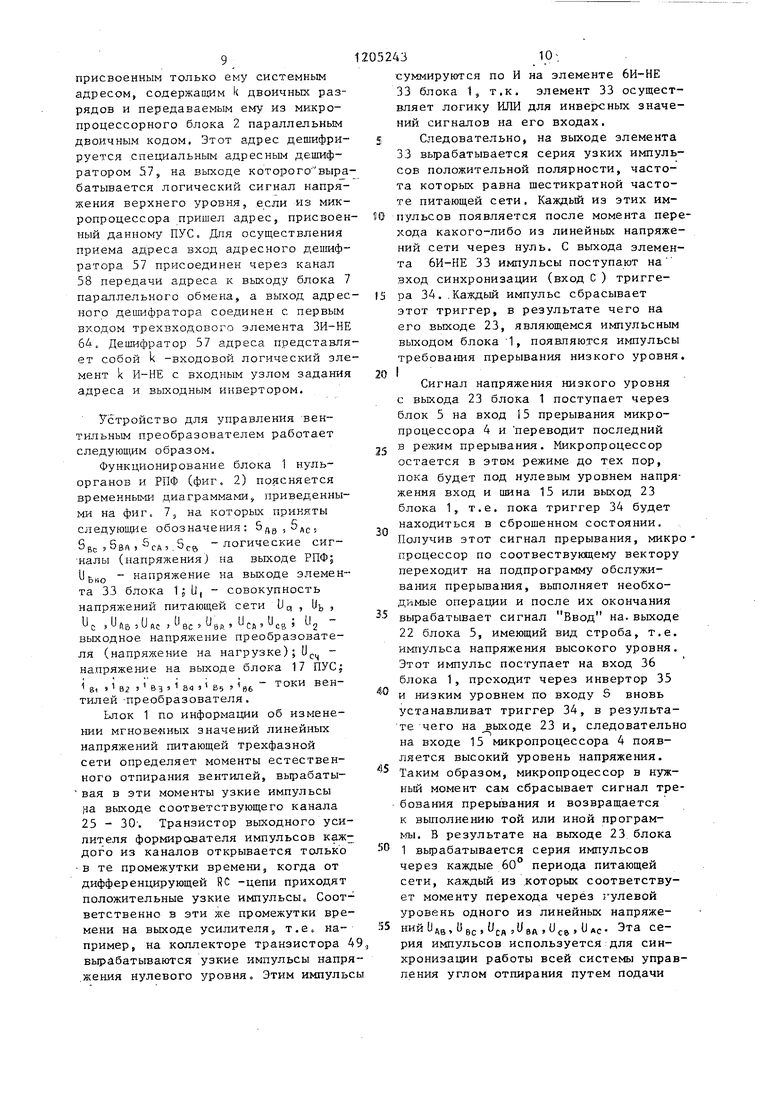

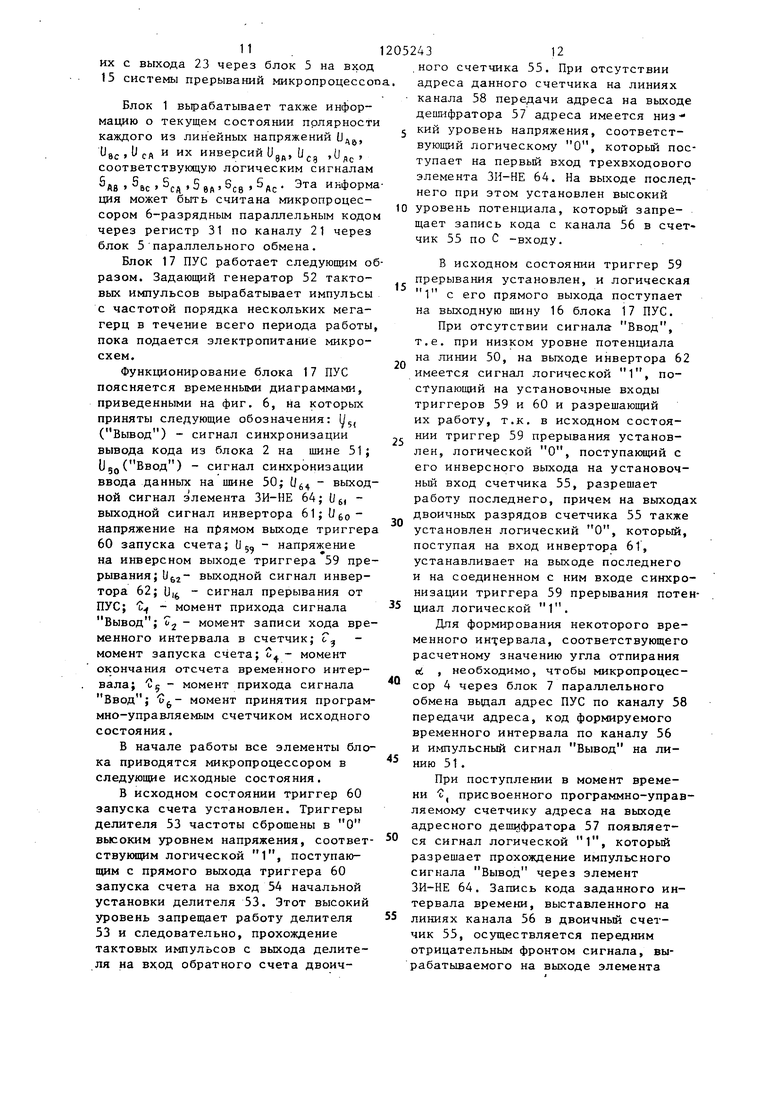

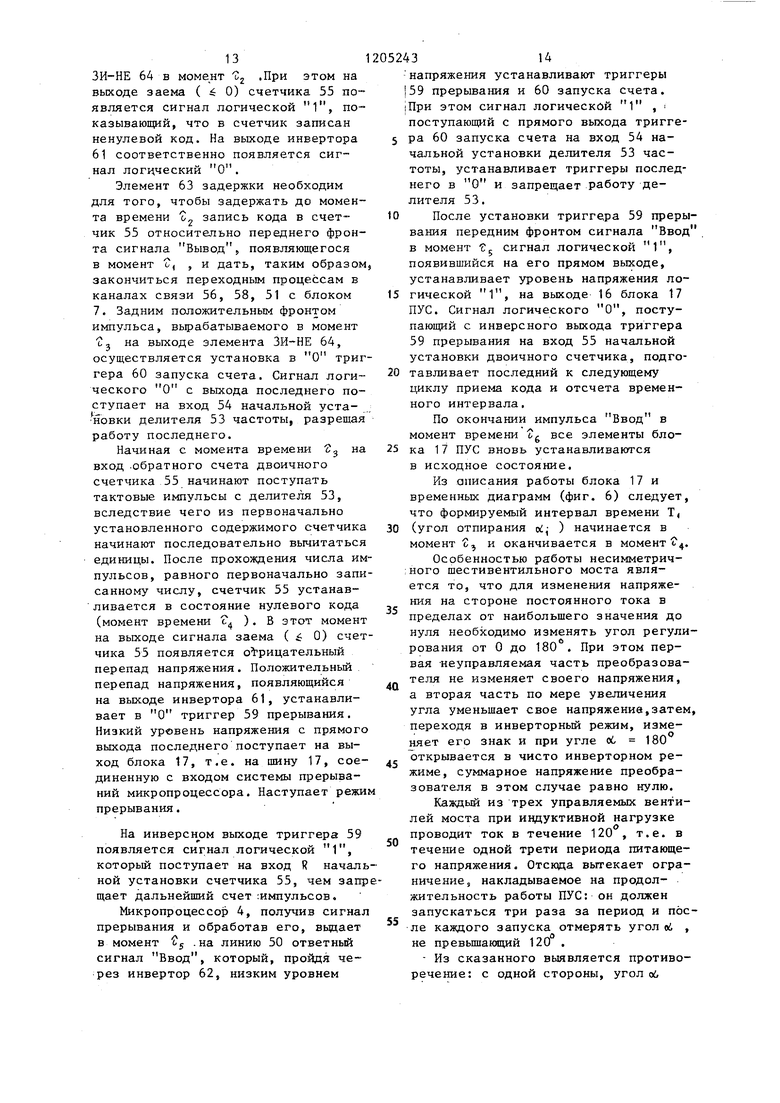

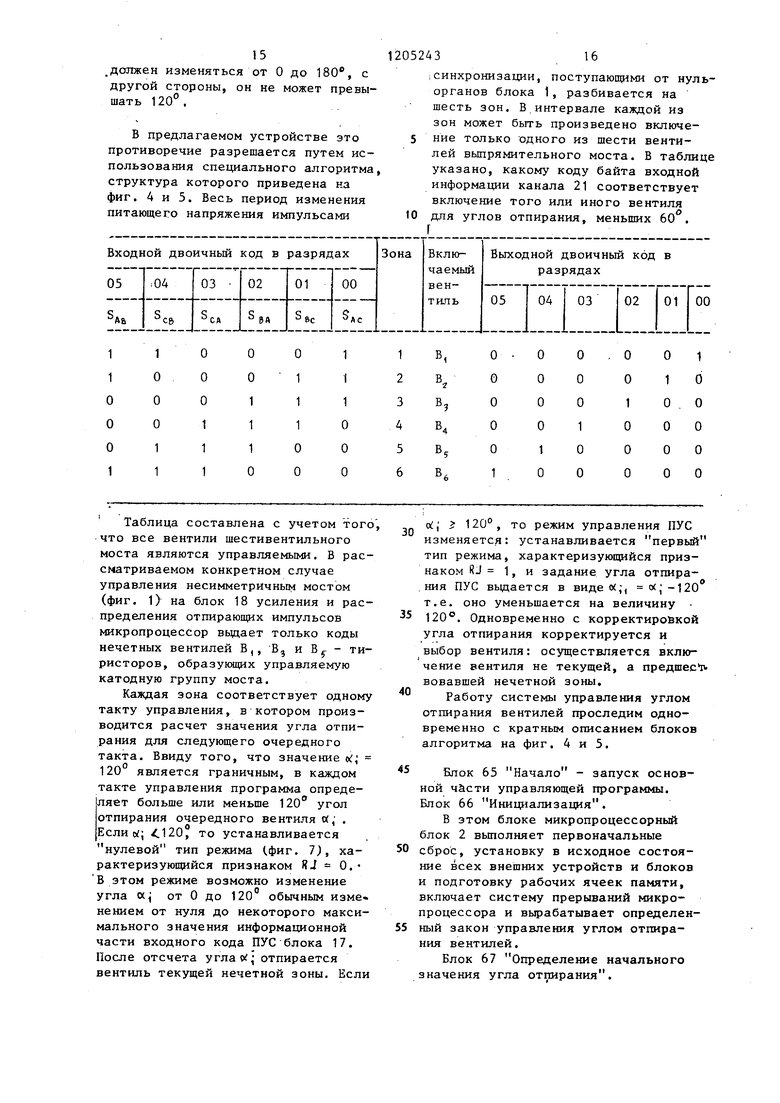

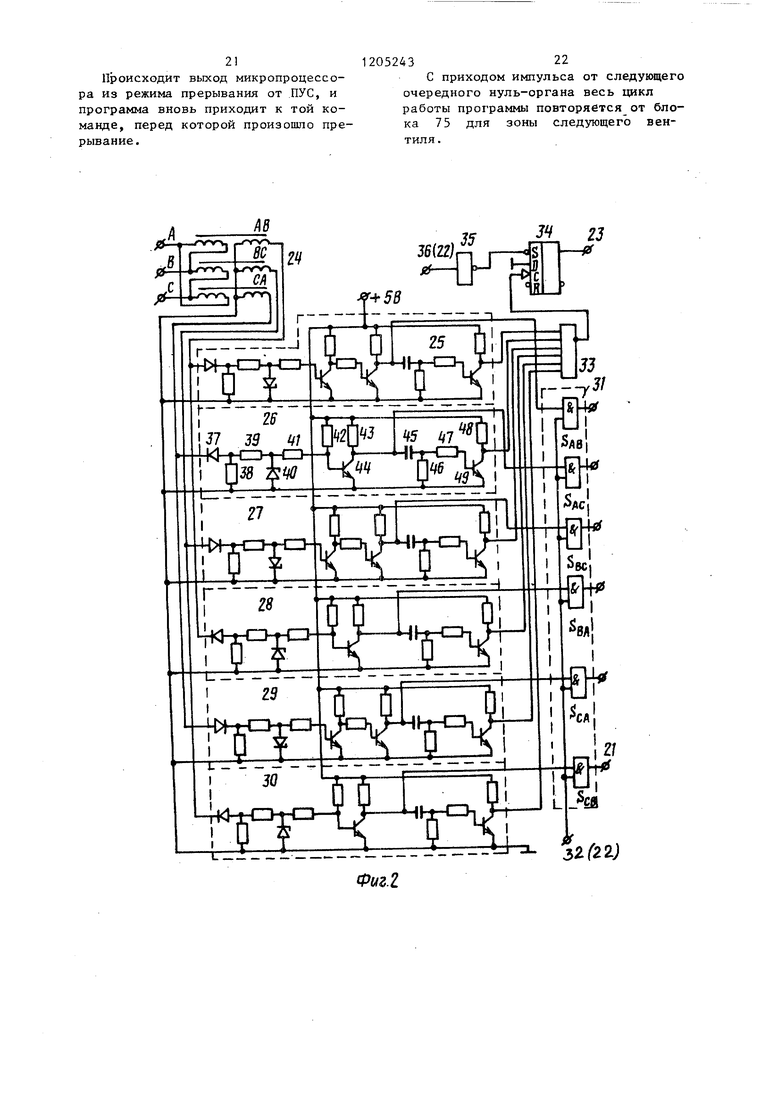

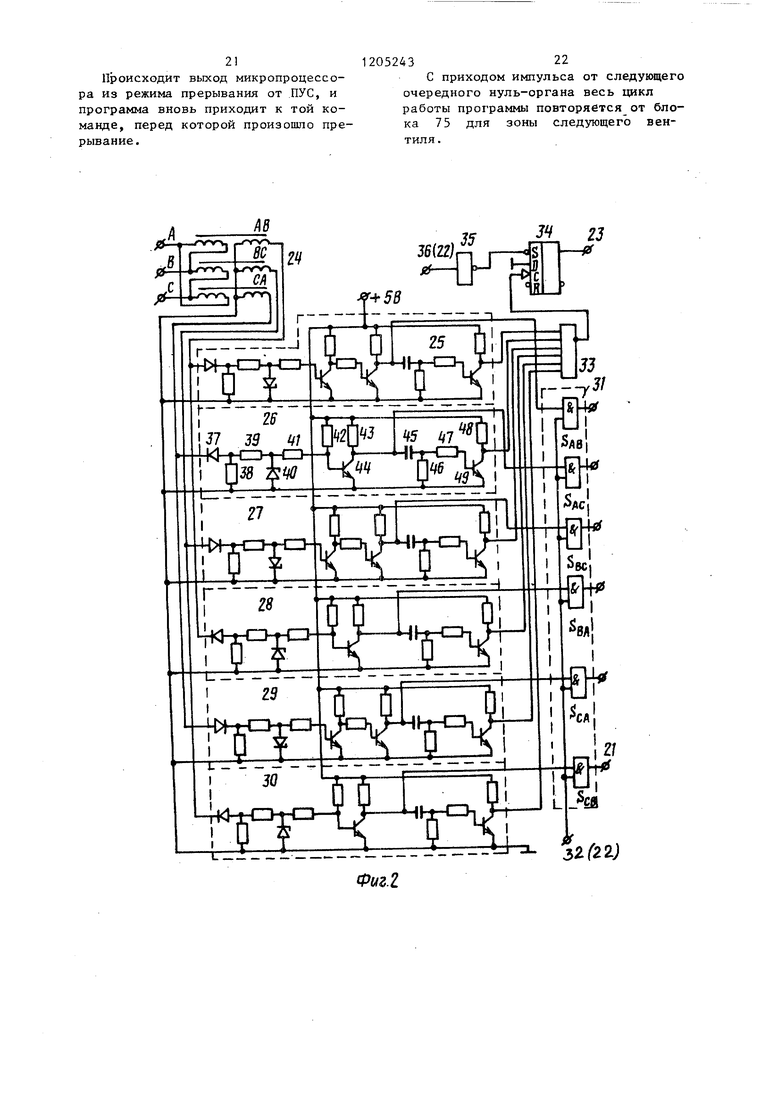

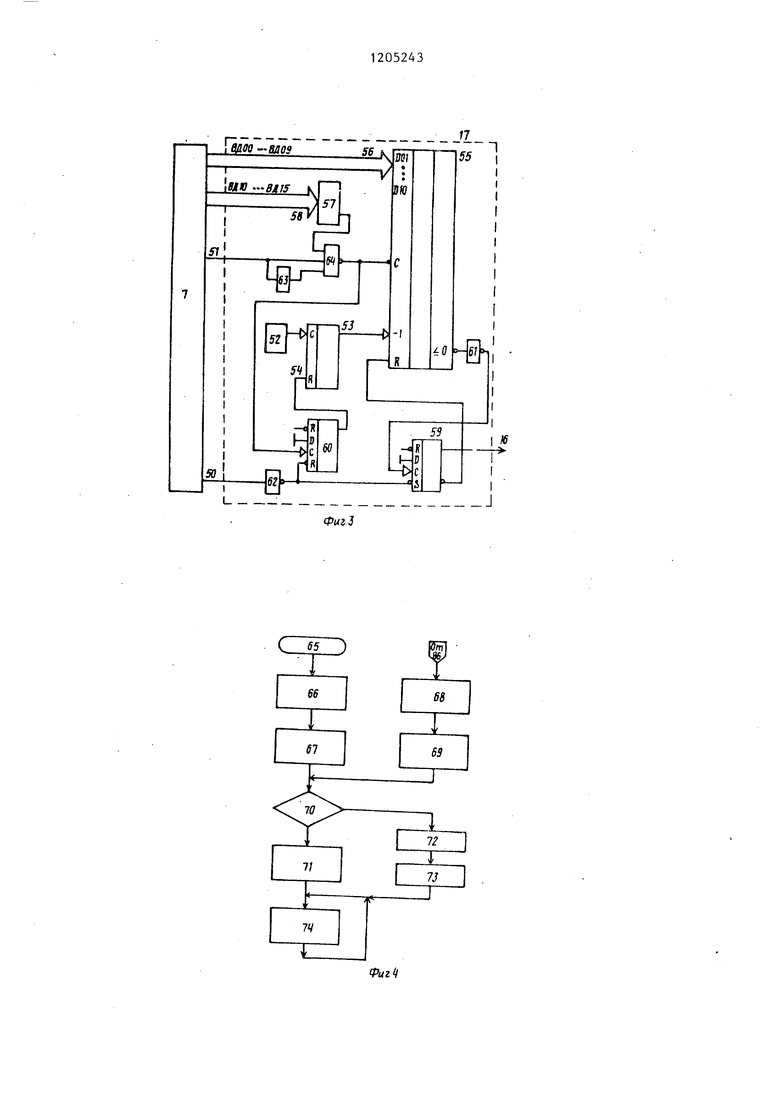

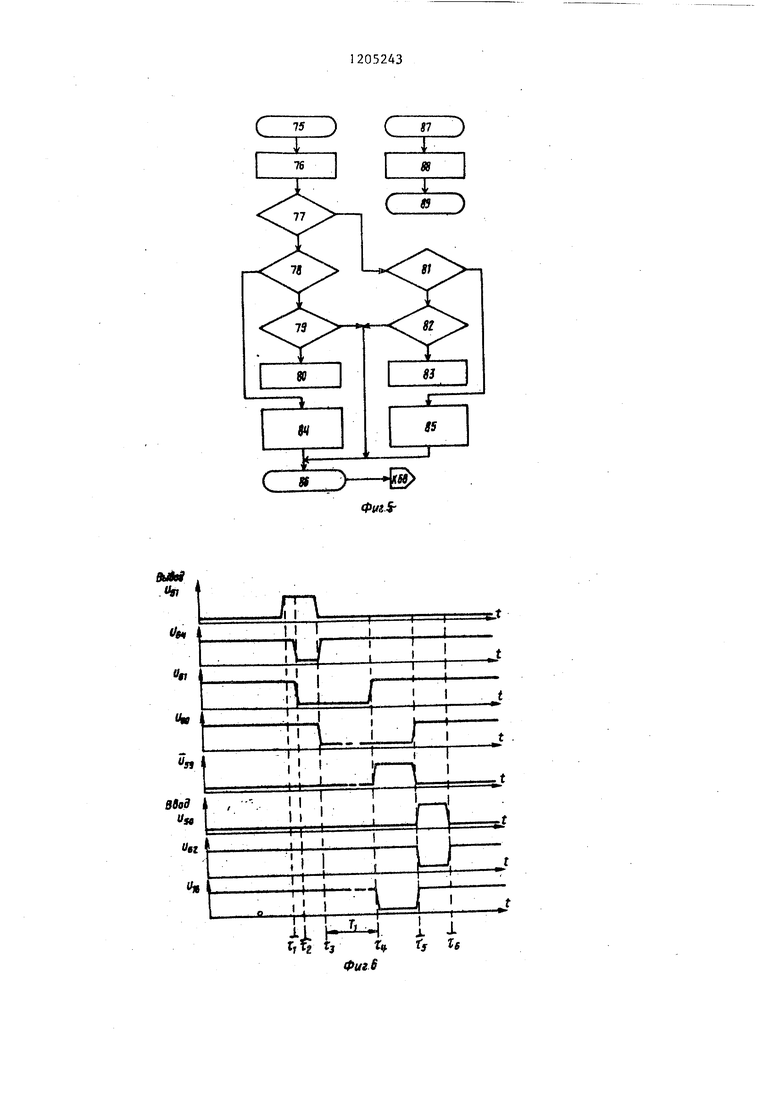

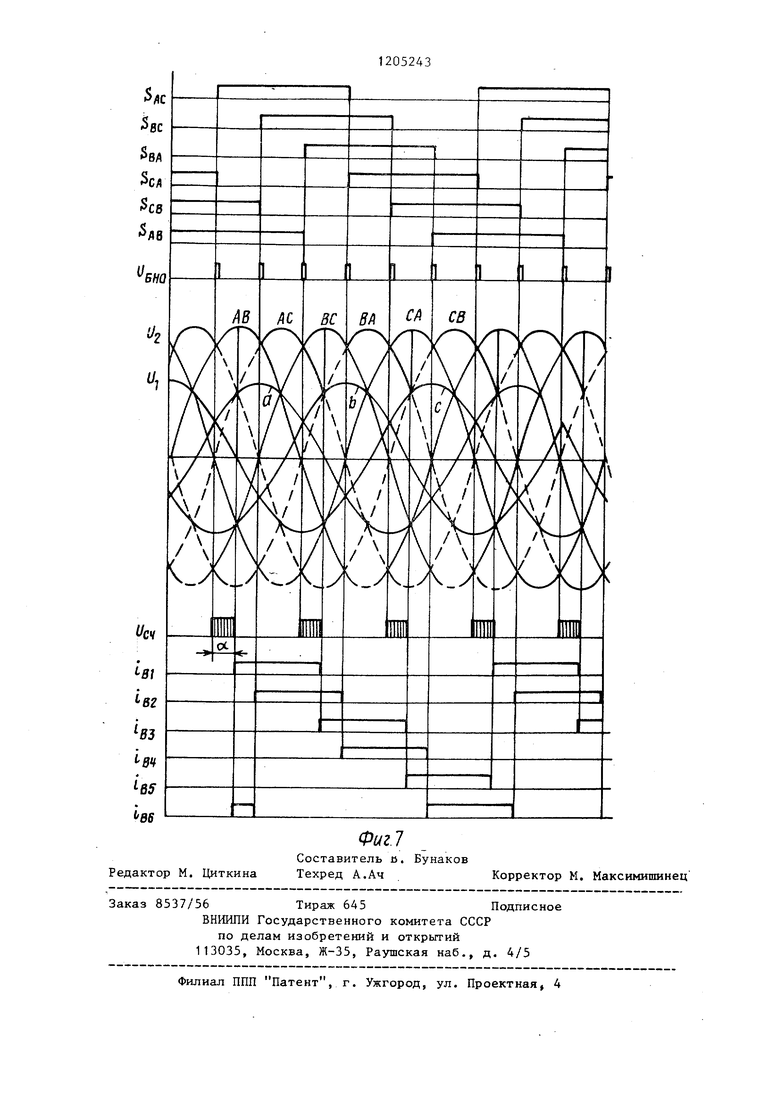

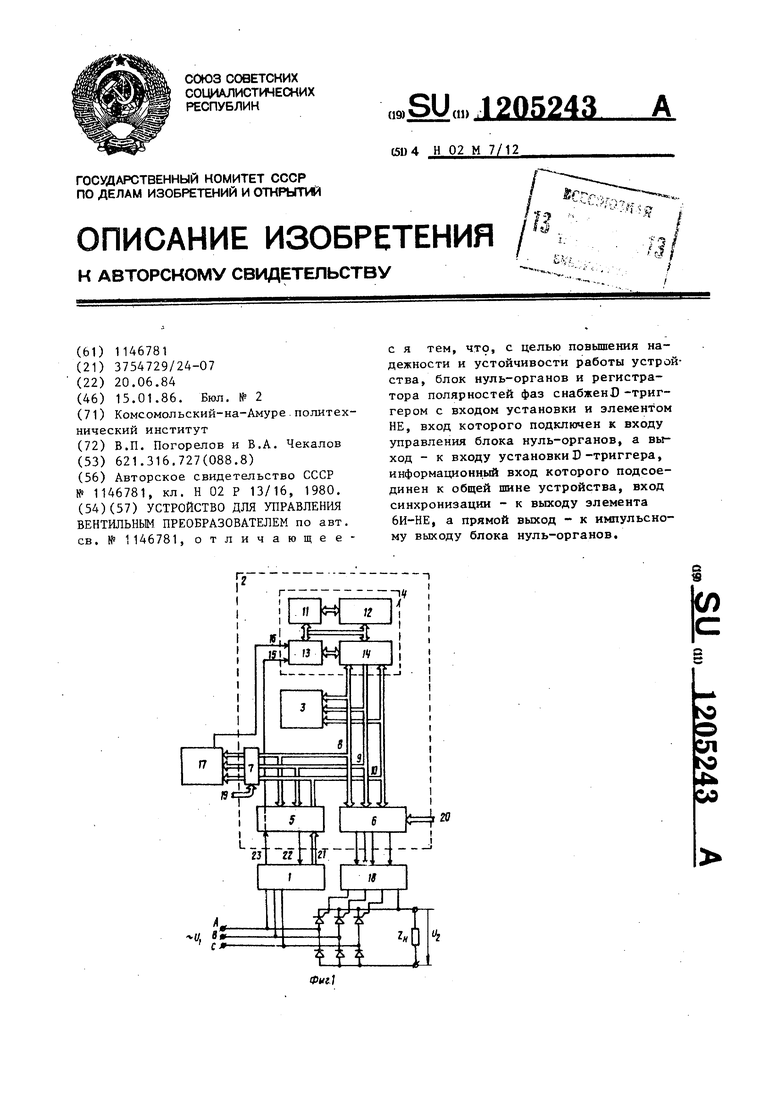

На фиг, 1 приведена функциональная схема устройства управления углом отпирания вентилей несимметричного шес- тивентильного моста; на фиг, 2 - прин ципиальная схема блока- пуль-органов и регистратора полярностей фаз (РПФ) на фиг, 3 - функциональная схема программно-управляемого счетчика (ПУС): на фиг. 4 - структурная схема алгоритма основной части управляющей программЫ| на фиг. 5 - структурная схема алгоритма программ прерывания; на фиг,, 6 - временные диаграммы по- ;ясняющие работу ПУС; на фиг. 7 - вре-

менные диаграм14Ы напряжений и токов.

I

:поясняющне работу устройства, Предлагаемое устройство предназначено для цифрового процессорного управления преобразователшми перемен- ного и постоянного тока различных типов, отличаюш.ихся как по числу фаз питающей сетИд так и по конфигурации силовой схемЫр количеству и типу вентилей. Рассматривается управление вентильным преобразователем (ВП) переменного тока в постоянный представляющим собой шестивентильный мост, питаюп1;ийся от трехфазной сети, в котором анодная группа содержит диоды а катодная - тиристоры (фиг. 1). Управляющие электроды тиристоров присоединены к соответствуюищм выходам блока усиления и распределения отпирающих импульсов устройства,

Входной информацией для устройства «служат линейные напряжения трехфазной питающей сети Цд, Ij j,. , Uc, и их инверсии УЗД, Ucg jLlftc- Каждому из этих напряжений соответствует свой нуль-орган (все они объединены в блоке 1 нуль-органов и РПФ,, фиг, 2),

Микропроцессорньй вычислительньй блок 2 представляет собой программируемое j управляющее в реальном масштабе времени специализированное, .вычислительное устройство, в состав .которого входят nporpaNJMHo-saAaKfflsee

5 0 5

о

5

5

0

S

0

устройство 3, микропроцессор 4, блоки 5, 6 и 7 ввода информации и вьшода информации (блоки параллельного обмена информацией), связанные между собой шинами 8 управления, 9 адреса, 10 данных. В качестве такого вычислительного устройства может быть также использована микро-ЭВМ, вьтол- ненная на основе конкретного микропроцессорного набора, например,К581.

Программно-задающее устройство 3 представляет собой сочетание пере- nporpaMivwpyeMoro запоминающего устройства (ПЗУ) и оперативного запоминающего устройства (ОЗУ) и служит для хранения программы работы, констант и переменных данных, получае- мьк от внешних устройств и в результате вычислений.

Блрки 5, 6 и 7 параллельного обмена информацией предназначены для приема микропроцессорным блоком 2 дискретной информации параллельным кодом от внешних устройств и блоков и передачи дискретной информации из микропроцессорного блока 2 во внешние устройства и блоки. С внешними устройствами и блоками обмен информацией осуществляется по шинам ввода и вывода через два 16-бит- ньгх триггерных регистра, имеющихся в составе каждого из блоков 5, 6 и 7, регистра ввода данных и регистра вывода данных. Обмен информа- пдей между микропроцессором 4 и блоками 5, 6 и 7 осуществляется посредством программных операций с опросом их флагов или с использованием средств прерывания. Любая программная операция, которая за- байт или слово в выходной регистр данных, вызывает появление на управляющем выходе блока параллельного обмена прямоугольного импульсного сигнала напряжения Вывод J информирующего внешний блок о выдаче ему данных. Когда данные считываются из регистра ввода данных микропроцессором,в блоке параллельного обмена вырабатьта- ется управляющий импульсный сигнал Ввод, который посылается во внешний блок, чтобы информировать последний о приеме данных.

Все блоки микропроцессорного вычислительного блока 2 связаны между собой каналом шин 8 управления, 9 адреса и 10 данных. Эти шины в

различных модификациях микропроцессоров могут быть одно- или двунаправленными. При этом 111ИНЫ адреса и данных могут быть как отдельными, так и объединенными. Например, для микропроцессорного набора К581 адрес и данные передаются по одним и тем же 16 двунаправленным шинам данных - адреса.

Микропроцессор (например, типа К581) состоит из стандартных узлов: БИС - регистрового арифметико-логического устройства 11, устройства 12 управляющей памяти, БИС 13 управления вьшолнением операций и интерфейса 14 (буфера) для связи микропроцессора с каналом шин адреса, данных и управления. В состав БИС 13 управления вьшолнением операций входит система прерывания микропроцессора, которая имеет два входа 15 и 16 в виде отдельных шин. Работа основной программы устройства может быть прервана либо от воздействия блока 1 нуль-органов по входу 15, либо от воздействия блока 17 ПУС по входу 16. При этом микропроцессор переходит на обработку соответствунмцей подпрограммы прерывания.

Блок 17 ПУС служит для отмеривания временных интервалов, соответствующих заданным или рассчитанным значениям угла отпирания л вентилей. Особенностью блока 17 в рассматриваемом варианте устройства является наличие в нем только одного ПУС тактовых импульсов, что оказьшается достаточным для управления тремя тиристорами несимметричного шестивен тильного моста. В блоке 17 осуществляется счет числа импульсов от высокочастотного генератора тактовых .импульсов, выход которого подключен через делитель частоты к тактовому входу двоичного управляемого счетчика. Последний может загружаться и управляться программно по шинам адреса, данных и управления. Для этого выход микропроцессорного модуля 2 подсоединен через блок 7 параллельного обмена к соответствуюпщм информационному и управляющим входам блока 17 ПУС, выход которого подключен к второму входу 16 системы прерываний микропроцессора 4.

Блок 18 служит для окончательного формирования, усиления и распределения отпирающих импульсов по вентилям Преобразователя. Для этого информаци

15

20

05243

|онный выход микропроцессорного блока 2 связан с входом блока 18 усиления и распределения импульсов через блок 6 параллельного обмена с информацией, Блок 18 представляет собой совокупность трех двухкас- кадных транзисторных усилителей по числу управляемых вентилей выпрямительного моста. Вход каждого из

10 этих усилителей подключен к выходу соответствующего информационного разряда регистра вывода блока 6, а выход - к управляющему электроду соответствующего тиристора В,, В, или Bj .

Заданное значение угла отпирания л,оЭ (или выходного напряжения а аз вентильного преобразователя вводится в микропроцессорный блок 2 по каналу 19 ввода дискретной информации. Канал 20 служит для ввода дискретньк сигналов обратной связи по току или напряжению вентильного преобразователя. Каждый

25 из каналов 19 и 20 ввода дискретной информации представляет собой комплект из 16 шин, которые подключены к соответствующим информационным входам 16-битных регистров ввода блоков 7 и 6 соответственно.

Блок 5 параллельного обмена служит для ввода в микропроцессорный модуль 2 дискретной информации о состоянии напряжений питающей сети от блока 1 нуль-органов и РПФ. Для этого информационные входы блока 1 подсоединены к клеммам питающей сети переменного тока, вход управления - к управляющему выходу 22 блока 5 параллельного обмена, импульсный выход 23 связан через блок 5 параллельного обмена с входом 15 системы прерываний микропроцессора 4, а информационный выход 21 через блок параллельного обмена 5 - с информационным вводом микропроцессорного блока 2.

Блок 1 нуль-органов и РПФ (фиг. 2) содержит разделительный согласующий рансформатор 24, шесть каналов 25-30 преобразования информации о состоянии полярностей фаз, управляемый регистр 31 с входом управления 32, шестивхо- довый логический элемент совпаде55 ния-инверсии 33, триггер 34 перехода через нулевое значение напряжения сети/ логический элемент НЕ .35 с входом 36. Каждый из каналов

30

35

40

45

50

%12

преобразования 25 30 информации о состоянии полярностей фаз, в свою очередь, содержит, нуль-орган и транзисторный формирователь импульсов. Последний состоит из дифференци-

рующей RS -цегш и выходного транзисторного усилителя., Совокупность шести нуль-органов образует шести- разрядньш регистратор полярностей фаз линейных напряжений и их инвер- сии,Выходы регистратора полярностей фаз подсоединены к входам логического элемента 6 И-НЕ 33j выход которого подключен к входу синхронизации (вход С ) триггера 34 перехода через нулевое значение линейного напряжения сети. Информагдаонный вход этого триггера (вход D ) подсоединен к шине Общий,, а прямой (неинверсный) выход триггера 34 является им- пульснььм выходом 29 блока 1 . Шина Ввод канала 22 управления, связанного с выходом блока 5 параллельного обменаJ подсоединена к входу 32 управления регистром 31 и входу 36, связанному через инвертор 35 с входо установки (вход 5 ) триггера 34.

Нуль-орган канала преобразования информации о состоянии полярности напряжения Ll д питающей сети содержит входную цепь и усилитель-нормализатор. Входная цепь нуль-органа содержит разделительный диод 37 с токо- ограничивающим резистором 38 и опорный диод 40 с токоограничива.ющим резистором 39. Цепочка последовательно соединенных разделительного диода 37 и резистора 38 включена между началом обмотки С А - разделительного трансформатора 24 и общей точкой звезды его вторичных обмоток. Цепочка последовательно соединенных резистора 39 и опорного диода 40 подключена параллельно резистору 38,

Транзисторный усилитель-нормализатор канала 26 преобразования содержит тразистор 44 п-р-п типа, базовый 41 и коллекторный 43 резисторы, а также резистор 42 смещения. Вход усилителя-нормализатора подключен параллельно опорному диоду 40,.

Усилитель-нормализатор служит для улучшения фронтов импульсов напря- женин, формируемьЕХ во входной цепи,, а также для приведения их к уровням логических 1 или Схема усилителя-нормализатора меняется в зависимости от того, в каком полупери-.

оде входного переменного напряжения он формирует сигнал логической 1, Если он формирует сигнал -Ч в первом полупериоде и сигнал О во вто5

5 0 5

о «

5

5

0

5

ром, то он выполняется по схеме с общим змиттером двухкаскадным и не имеет резистора смещения. По такой схеме выполнены усилители-нормализаторы в каналах преобразования 25, 27 и 29,

Если усилитель-нормализатор формирует сигнал 1 во втором полупериоде и сигнал О в первом, то он выполняется, как в рассматриваемом случае, по схеме с общим змиттером однокаскадным. При этом он.снабжен резистором 42 смещения, который включен между плюсовой шиной источ- -ника и базой транзистора 44. По такой схеме выполнены усилители-нормализаторы в каналах преобразования 26, 28 и 30.

Напряжение выходе усилителя- нормализатора йвляется информационным выходным сигналом для соответствующего разряда регистратора полярностей фаз, позтому для передачи этого сигнала выход усилителя- нормализатора соединен с информационным входом соответствующего логического элемента 2 И регистра 31,

Дифференцирующая цепь, состоящая из последовательно соединенных конденсатора 45 и резистора 46, и выходной усилитель на транзисторе 49 образуют формирователь импульсов синхронизации канала преобразования 26. Дифференцирующая цепь подключена между выходом усилителя-нормализатора (коллектор транзистора 44) и общим проводом. Она служит для формирования узких импульсов напряжения после момента перехода линейного напряжения Удс через нулевое значение.

Выходной транзисторный усилитель содержит транзистор 49,базовый 47 и коллекторньй 48 резисторы,Вход этого усилителя подключен параллельно резистору 46 дифференцирующей цепи.

Устройство остальных каналов.преобразования аналогично и отличается лишь точкой подключения входной цепи, направлением проводимости разделительного 37 и опорного 40 диодов и конфигурацией схемы усилителя-нормализатора ,

Блок 7 имеет шину управления 50 Ввод и шину управления 51 Вывод

Блок 17 ПУС (фиг. 3) задакщий генератор 52 прямоугольных тактовых импульсов, делитель 53 частоты такт вьгх импульсов, с входом 54 начальной установки, двоичный счетчик 55 тактовых импульсов, дешифратор 57 адреса, триггер 59 прерывания, триггер 60 запуска счета, трехвходовьй логический элемент совпадения-инверсии ЗИ-НЕ 64, элемент задержки 63 и инверторы 61 и 62. Информационные входы счетчика импульсов - в нашем примере с первого по десятый (т 10) - подключены через канал

56вывода кода временного интервала к соответствующим с первой по десятую выходным информационным шинам ВДОО - ВД09 блока 7 параллель- ного обмена. Выходные информационные шины с одиннадцатой по шестнад- чатую БД ,10 - ВД 15 ( k 6)- подключены через канал 58 вывода адреса программно-управляемого счетчика к соответствующим входам дешифратора

57адреса, выход которого подключен к первому входу трехвходового элемента 64 совпадения-инверсии. Шина управления Вывод 51 блока 7 подкл чена к второму входу непосредственг

но и через элемент 68 задержки к третьему входу трехвходового элемента совпадения 64. Выход последнего подключен к входу синхронизации (вход С) триггера 60 запуска счета и входу записи (вход С ) счетчика ипульсов 55.

Задающий генератор 52 прямоугольных импульсов выполнен по известной схеме на трех двухвходовых элемента 2И-НЕ и стабилизирован по частоте кварцевым резонатором. Выход генератора 52 подключен к входу синхронзации (входу С ) делителя частоты импульсов генератора, осуществляющего уменьшение частоты импульсов генератора в 2 раз, где п - число последовательно включенных триггеров делителя 53.

Делитель 53 частоты импульсов выполнен, например, на основе счетчика, содержащего п последовательно включенных триггеров, работающих в счетном режиме, причем количество триггеров п определяется необходимым диапазоном периода тактовых импульсов, подаваемых на вход счетчика 55, и частотой задающего генера- тора 52. Делитель 53 частоты имеет вход 54 начальной установки (вход R) при подаче потенциального сигнала напряжения высокого уровня на который можно установить все триггеры делителя в исходное состояние и запртить работу делителя. Выход делителя подключен к вычитающему входу (вход обратного счета -1) счетчика 55.

Счет тактовых импульсов, поступающих с выхода делителя 53 частоты, осуществляется m -разрядным двоичным счетчиком 55, имеющим м информационных входов (DI -Оп)), счетный вход -1, вход записи С и вход начальной установки.R . Информационные входы счетчика подсоединены к информционному вызсоду блока 7 микропроцессорного модуля 2 через канал 56 вьшо да кода временного интервала. Счетчик 55 снабжен специальным триггером 59 прерывания, который перебрасывается в О в момент окончания счета заданного числа импульсов, сигнализируя этим окончание отработки заданного временного интервала. Для осуществления этого вход начальной установки R счетчика 55 присоединен к инверсному выходу триггера 59 прерывания, вход записи С - к выходу трехвходового элемента 3 И-НЕ 64. Информационный вход триггера 59 прерывания подключен к шине Логический О (Общий), вход синхронизации через инвертор 61 - к выходу заёма счетчика 55, установочный вход - к выходу инвертора 62.

Триггер 60 запуска счета служит для управления работой делителя 53 частоты импульсов. Для этого информационный вход триггера 60 запуска счета соединен с шиной Логический О, (Общий), вход стробирования подключен к выходу элемента ЗИ-НЕ 64, установочный вход через инвертор 62 - к шине 50 управляющего сигнала Ввод блока 7 параллельного обмена модуля 2, а выход - к входу 54 начальной у становки делителя.

Выходом блока 17 программно-управляемого счетчика является прямой выход триггера 59 прерывания, подключенный к выходной шине 16 блока 17.

Являясь частью управляющей микропроцессорной системы, которая может содержать несколько счетчиков, каждый ПУС характеризуется определенным.

присвоенным только ему системным адресом, содержао им k двоичных разрядов и передаваемым ему из микропроцессорного блока 2 параллельным двоичным кодом. Этот адрес дешифрируется специальным адресным дешифратором 57, на выходе которого выра- батывается логический сигнал напряжения верхнего уровня, если из микропроцессора пришел адрес, присвоенный данному ПУС. Для осуществления приема адреса вход адресного дешифратора 57 присоединен через канал 58 передачи адреса к выходу блока 7 параллельного обмена, а выход адресного дешифратора соединен с первым входом трехвходового элемента ЗИ-НЕ 64. Дешифратор 57 адреса представляет собой k -входовой логический элемент k И-НЕ с входным узлом задания адреса и выходным инвертором.

Устройство для управления вентильным преобразователем работает cлeдyю n м образом.

Функционирование блока 1 нуль- органов и РПФ (фиг. 2) поясняется временными диаграммами, приведенными на фиг. 7, на которых приняты следующие обозначения: flgjSft,,,

SBC , SBA , 5(-д ,

- логические сигналы (напряжения) на выходе РПФ; Ъио напряжение на выходе элемента 33 блока 1;U, - совокупность напряжений питающей сети Ll , Ui, ,

с - ftb и ftc , и вс fjA СА JCB - 2 выходное напряжение преобразователя (напряжение на нагрузке); 11;, - напряжение на выходе блока 17 ПУС;

i 8, «i В2 5 вэ 5 Uo 5 i В5 вб тилей -преобразователя.

Ьлок 1 по информации об изменении мгновенных значений линейных напряжений питающей трехфазной сети определяет моменты естественного отпирания вентилей, вырабаты вая Б эти моменты узкие импульсы fta выходе соответствующего канала 25 - 30. Транзистор выходного усилителя формирователя импульсов каждого из каналов открывается только

в те промежутки времени, когда от дифференцирующей RC -цепи приходят положительные узкие импульсы. Соответственно в эти же промежутки времени на выходе усилителя, т.е. например, на коллекторе транзистора 4 вырабатываются узкие импульсы напря .жения нулевого уровня. Этим импульс

205243Ю-,

суммируются по и на элементе 6И-НЕ 33 блока 1, т.к. элемент 33 осуществляет логику ИЛИ для HHBejptCHbix значений сигналов на его входах.

5Следовательно, на выходе элемента

33 вырабатывается серия узких импульсов положительной полярности, частота которых равна шестикратной частоте питающей сети. Каждый из этих имШ пульсов появляется после момента перехода какого-либо из линейных напряжений сети через нуль. С выхода элемента 6И-НЕ 33 импульсы поступают на вход синхронизации (вход С ) тригге13 ра 34..Каждый импульс сбрасывает этот триггер, в результате чего на его выходе 23, являющемся импульсным выходом блока 1, появляются импульсы требования прерывания низкого уровня.

I

Сигнал напряжения низкого уровня

с выхода 23 блока 1 поступает через блок 5 на вход 15 прерывания микропроцессора 4 и переводит последний

в режим прерывания. Микропроцессор остается в этом режиме до тех пор, пока будет под нулевым уровнем напряжения вход и шина 15 или выход 23 блока 1, т.е. пока триггер 34 будет находиться в сброшенном состоянии. Получив этот сигнал прерывания, микро процессор по соотвествующему вектору переходит на подпрограмму обслуживания прерьшания, выполняет необходимые операции и после их окончания

вырабатьшает сигнал Ввод на. выходе 22 блока 5, имеющий вид строба, т.е. импульса напряжения высокого уровня. Этот импульс поступает на вход 36 блока 1, проходит через инвертор 35

и низким уровнем по входу 5 вновь устанавливат триггер 34, в результате чего на выходе 23 и, следовательно на входе 15 микропроцессора 4 появляется высокий уровень напряжения. Таким образом, микропроцессор в нужный момент сам сбрасывает сигнал требования прерывания и возвращается к вьшолнению той или иной програм- t-ibi. В результате на выходе 23 блока 1 вырабатывается серия импульсов через каждые 60° периода питающей сети, каждый из .которых соответствует моменту перехода через гулевой уровень одного из линейных напряжеHwnUfte,Ue,Uc,UeA,Uc5,,U«c- Эта серия импульсов используется для синхронизации работы всей системы управления углом отпирания путем подачи

их с выхода 23 через блок 5 на вход 15 системы прерываний микропроцессоп

Блок 1 вырабатывает также информацию о текущем состоянии полярности каждого из линейных напряжений (J, UBC , и сА и их инверсий Ug, U, ,1 , соответствующую логическим сигналам

бдв вс сд 5вА 6с9« Ас- Эта информация может быть считана микропроцессором 6-разрядным параллельным кодом через регистр 31 по каналу 21 через блок 5 параллельного обмена.

Блок 17 ПУС работает следующим образом. Задающий генератор 52 тактовых импульсов вырабатывает импульсы с частотой порядка нескольких мегагерц в течеиие всего периода работы, пока подается электропитание микросхем.

Функционирование блока 17 ПУС поясняется временными диаграммами, приведенными на фиг. 6, на которых приняты следующие обозначения: у (Вывод) - сигнал синхронизации вывода кода из блока 2 на шине 51; и50(Ввод) - сигнал синхронизации ввода данных на щине 50; (J - выходной сигнал элемента ЗИ-НЕ 64; О g, - выходной сигнал инвертора 61;1/бо напряжение на прямом выходе триггера 60 запуска счета; tJ 59 напряжение на инверсном выходе триггера 59 прерывания; 1(,2 выходной сигнал инвертора 62; Ui - сигнал прерывания от ПУС; о - момент прихода сигнала Вывод ; момент записи хода временного интервала в счетчик; Г - момент запуска счета; С - момент окончания отсчета временного интервала; момент прихода сигнала (, момент принятия программно-управляемым счетчиком исходного состояния.

в начале работы все элементы блока приводятся микропроцессором в следующие исходные состояния.

В исходном состоянии триггер 60 запуска счета установлен. Триггеры делителя 53 частоты сброшены в О

высоким уровнем напряжения, соответствующим логической 1, поступающим с прямого выхода триггера 60 запуска счета на вход 54 начальной установки делителя 53. Этот высокий уровень запрещает работу делителя 53 и следовательно, прохождение тактовых импульсов с выхода делителя на вход обратного счета двоич

него счетчика 55. При отсутствии адреса данного счетчика на линиях канала 58 передачи адреса на выходе дешифратора 57 адреса имеется низ 5 кий уровень напряжения, соответст- вую1ций логическому О, который поступает на первый вход трехвходового элемента ЗИ-НЕ 64. На выходе последнего при этом установлен высокий

0 уровень потенциала, который запрещает запись кода с канала 56 в счетчик 55 по С -входу.

15

0

5

0

5

Q

5

0

В исходном состоянии триггер 59 прерывания установлен, и логическая 1 с его прямого выхода поступает на выходную шину 16 блока 17 ПУС.

При отсутствии сигнала Ввод, т.е. при низком уровне потенциала на линии 50, на выходе инвертора 62 имеется сигнал логической 1, поступающий на установочные входы триггеров 59 и 60 и разрешающий их работу, т.к. в исходном состоянии триггер 59 прерывания установлен, логической О, поступающий с его инверсного выхода на установочный вход счетчика 55, разрешает работу последнего, причем на выходах двоичных разрядов счетчика 55 также установлен логический О, который, поступая на вход инвертора 61, устанавливает на выходе последнего и на соединенном с ним входе синхронизации триггера 59 прерывания потенциал логической 1.

Для формирования некоторого временного ин тервала, соответствующего расчетному значению угла отпирания о; , необходимо, чтобы микропроцессор 4 через блок 7 параллельного обмена вьщал адрес ПУС по каналу 58 передачи адреса, код формируемого временного интервала по каналу 56 и и fflyльcный сигнал Вывод на линию 51.

При поступлении в момент времени о, присвоенного программно-управляемому счетчику адреса на выходе адресного дешифратора 57 появляет

который

разрешает прохождение импульсного сигнала Вывод через элемент ЗИ-НЕ 64. Запись кода заданного интервала времени, выставленного на линиях канала 56 в двоичный счетчик 55, осуществляется передним отрицательным фронтом сигнала, вырабатываемого на выходе элемента

2 .При этом на

ЗИ-НЕ 64 в момент Z выходе заема ( 6 0) счетчика 55 по является сигнал логической 1, показывающий, что в счетчик записан ненулевой код. На выходе инвертора 61 соответственно появляется сигнал логический О.

Элемент 63 задержки необходим для того, чтобы задержать до момента времени о запись кода в счетчик 55 относительно переднего фронта сигнала Вывод, появляющегося в момент ( , и дать, таким образом закончиться переходным процессам в каналах связи 56, 58, 51 с блоком 7. Задним положительным фронтом импульса, вырабатываемого в момент clj на выходе элемента ЗИ-НЕ 64, осуществляется установка в О триггера 60 запуска счета. Сигнал логического О с выхода последнего поступает на вход 54 начальной уста- новки делителя 53 частоты, разрешая работу последнего.

Начиная с момента времени 2 на вход .обратного счета двоичного счетчика 55 начинают поступать тактовые импульсы с делителя 53, вследствие чего из первоначально установленного содержимого счетчика начинают последовательно вычитаться единицы. После прохождения числа импульсов, равного первоначально записанному числу, счетчик 55 устанавливается в состояние нулевого кода (момент времени Р ). В этот момент на выходе сигнала заема ( 0) счетчика 55 появляется о рицательный перепад напряжения. Положительньй перепад напряжения, появляющийся на выходе инвертора 61, устанавливает в О триггер 59 прерывания. Низкий уровень напряжения с прямого выхода последнего поступает на выход блока 17, т.е. на шину 17, соединенную с входом системы прерываний микропроцессора. Наступает режи прерывания.

На инверсн эм выходе триггера 59 появляется сигнал логической 1, который поступает на вход R начальной установки счетчика 55, чем запрщает дальнейший счет :импульсов.

Микропроцессор 4, получив сигнал прерывания и обработав его, вьщает в момент .на линию 50 ответньй сигнал Ввод, который, пройдя через инвертор 62, низким уровнем

напряжения устанавливают триггеры |59 прерывания и 60 запуска счета. |При этом сигнал логической 1 , поступающий с прямого выхода тригге- ра 60 запуска счета на вход 54 начальной установки делителя 53 частоты, устанавливает триггеры последнего в О и запрещает работу делителя 53.

После установки триггера 59 прерывания передним фронтом сигнала Ввод в момент Dj сигнал логической 1, появившийся на его прямом выходе, устанавливает уровень напряжения логической 1, на выходе 16 блока 17 ПУС. Сигнал логического О, поступающий с инверсного выхода триггера 59 прерывания на вход 55 начальной установки двоичного счетчика, подготавливает последний к следующему циклу приема кода и отсчета временного интервала.

По окончании импульса Ввод в момент времени 1) все элементы блока 17 ПУС вновь устанавливаются в исходное состояние.

Из описания работы блока 17 и временных диаграмм (фиг. 6) следует, что формируемый интервал времени Т,

(угол отпирания od,- ) начинается в момент , и оканчивается в моменте .

Особенностью работы несимметрич- :ного шестивентильного моста является то, что для изменения напряжения на стороне постоянного тока в

пределах от наибольшего значения до нуля необходимо изменять угол регулирования от О до 180 . При этом первая -неуправляемая часть преобразователя не изменяет своего напряжения, а вторая часть по мере увеличения угла уменьшает свое напряжение,затем, переходя в инверторный режим, изменяет его знак и при угле об 180 открывается в чисто инверторном режиме, суммарное напряжение преобразователя в этом случае равно нулю.

Каждый из трех управляемых вентилей моста при индуктивной нагрузке проводит ток в течение 120 , т.е. в течение одной трети периода питающего напряжения. Отсщца вытекает ограничение, накладываемое на продолжительность работы ПУС: он должен запускаться три раза за период и после каждого запуска отмерять угол oi , не превьш1аклций 120 .

- Из сказанного выявляется противо- речение: с одной стороны, угол об

151205243

я от О до 180, с он не может превы

iси ор ше зо ни ле ук ин вк дл

В предлагаемом устройстве это противоречие разрешается путем использования специального алгоритма, структура которого приведена на фиг. 4 и 5. Весь период изменения питающего напряжения импульсами

Таблица составлена с учетом того что все вентили шестивентильного моста являются управляемыми. В рассматриваемом конкретном случае управления несимметричным мостом (фиг. 1) на блок 18 усиления и распределения отпирающих импульсов микропроцессор вьщает только коды нечетных вентилей В,, Б, и В - тиристоров, образукяцих управляемую катодную группу моста.

Каждая зона соответствует одному такту управления, в котором производится расчет значения угла отпирания для следующего очередного такта. Ввиду того, что значение ч( 120 является граничным, в каждом такте управления программа определяет больше или меньше 120 угол отпирания очередного вентиля и, . Если 4.120, то устанавливается нулевой тип режима (,фиг. 7), характеризующийся признаком RJ - 0. В этом режиме возможно изменение угла «j от О до 120° обычным изме« нением от нуля до некоторого максимального значения информационной части входного кода ПУС блока 17. После отсчета угла с отпирается вентиль текущей нечетной зоны. Если

16

iсинхронизации, поступающими от нуль- органов блока 1, разбивается на шесть зон, В.интервале каждой из зон может быть произведено включение только одного из шести вентилей вьшрямительного моста. В таблице указано, какому коду байта входной информации канала 21 соответствует включение того или иного вентиля для углов отпирания, меньших бо.

Г

0

5

0

5

0

5

120°, то режим управления ПУС изменяется: устанавливается первый тип режима, характеризующийся признаком RJ 1, и задание угла отпира- . НИН ПУС выдается в виде ot;, «;-120 т.е. оно уменьшается на величину - 120°. Одновременно с корректировкой угла отпирания корректируется и выбор вентиля: осуществляется включение вентиля не текущей, а предшес г вовавшей нечетной зоны.

Работу системы управления углом отпирания вентилей проследим одновременно с кратным описанием блоков алгоритма на фиг. 4 и 5.

Блок 65 Начало - запуск основной части управляющей программы. Блок 66 Инициализация.

В этом блоке микропроцессорный блок 2 вьтолняет первоначальные сброс, установку в исходное состояние всех внешних устройств и блоков и подготовку рабочих ячеек памяти, включает систему прерываний микропроцессора и вырабатывает определенный закон управления углом отпирания вентилей.

Блок 67 Определение начального значения угла отпирания.

отпирания, например, в двоичном коде считывается микропроцессором через блок 7 параллельного обмена по ка- налу 19, корректируется в соответствии с сигналом обратной связи, вводи мым по каналу 20, в соответствии с выбранным законом управления и подготавливается к вьщаче его на информационный вход ПУС блока 17. В примере программы, приведенном ниже, начальное значение угла отпирания задано константой в ячейке памяти AL Р.

Блок 68 Прием входной информации .

Программа работает циклически, по тактам, с периодом, равным 60 . Импульсами синхронизации, проходящими от нуль-органов блока 1,осуществляется прерывание основной программы шесть раз за период. В каждом такте программа считывает по каналу 19 заданное значение выходной координаты (напряжения или тока на выходе,ВП). Пусть ВП работает в режиме регулирования напряжения остоянного тока: на активно-индуктивной нагрузке (J i . В этом случае по каналу 19 считывается заданное значение выходного напряжения и. По каналу 20 с датчика считывается сигнал обратной связи, т.е. техно- Ьогическая информация о контролируемом .параметре. В нашем случае таким параметром является фактическое среднее значение выходного напряжения (.

Блок 69 Расчет следующего значения угла отпирания.

По известными g рассчитывается в соответствии с выбранным законом регулирования значение угла отпирания o(J для следующего вентиля.

Блок 70 Определение типа режима.

Производится анализ величины рас- ч тного значения угла отпирания, т.е. решается вопрос Л 120°.

Если 120 то программа переходит к блоку 71, если «; 120 , то программа переходит к блоку 72.

Блок 71 Установка признака режима О., Так как расчетное значение угла oi; . 120, то имеет место нулевой режим и устанавливается признак этого режи1 а; в ячейку памяти R5 записывается 0.

жима

1.

Так как расчетное значение угла , то имеет место первый ре- жим и программа устанавливает признак этого режима: в ячейку памяти RJ записывается 1.

Блок 73 Корректировка угла отпирания .

В связи с тем, что имеет место режим 1, производится корректировка значения угла отпирания и . Вычисляется значение

15

ц

-0 - 120

которое будет преобразовано в двоичный код задания ПУС.

Блок 74 Ожидание прерывания.

20

Так как все расчетные и подготовительные операции проведены, то дается команда разрешить прерыва- ,ние микропроцессора и ожидать прерывания .

Блок 75 Прерывание от нуль- органов.

При достижении напряжением какой- либо из фаз питающей сети точки естественного отпирания блок 1

30 нуль-органов и РИФ вырабатывает импульс напряжения нулевого уровня на своем выходе 23 по прерыванию, чем воздействует через блок параллельного обмена 5 на вход 15 системы

5 прерываний микропроцессора. Начищается выполнение подпрограммы Прерывание от нуль-органов.

Блок 76 Прием кода от РИФ. Микропроцессор вырабатывает

0 ,сигнал Ввод и принимает код от

РПФ блока 1 через регистр ввода блока 5 по информационному каналу 21. По сигналу Ввод поступающему на вход 36 блока 1, устанавливается

5 триггер 34, что соответствует снятию сигнала требования прерывания от нуль-органов блока 1.

Блок 77 Режим 1.

Микропроцессор анализирует содержимое ячейки Rj- признака типа режима и, если оно равно О, переходит к блоку 78, а если оно равно 1, то переходит к блоку 81.

Блок 78 Зоны 1, 3, 5 вентилей. 5 Микропроцессор анализирует код состояния полярностей фаз и по нему определяет, зона какого вентиля имеет место в данный момент для режи0

ia 0. Если Идет зона нечетного вентиля, то программа переходит к блоку 84, если зона четного вентиля - то к блоку 79.

Блок 79 Зоны 2, 4, 6 вентилей. Микропроцессор анализирует код состояния полярностей фаз для режима О и по нему определяет, зона какого вентиля имеет место в данный момент. Если идет зона четного вентиля то программа переходит к блоку 86,

если из зон.не идентифици- , рована, то к блоку 80.

Блок 80 Аварийное состояние О.

Так как микропроцессором не была идентифицирована зона ни одного из вентилей, это значавт,.что принятьм код от РПФ не совпадает с эталонными кодами зон, следовательно, имеются нарушения в работе аппаратуры. Воз- можность выхода программы на блок 80 позволяет организовать такие функции системы: диагностику состояния аппаратуры; автоматический поиск неиспраного узла; выдачу на печать или экран дисплея сообщений обслуживающему персоналу; выполнение переключений, аварийное отключение; включение сигнализации и др.

В приведенном примере программы предусмотрен только Аварийный останов О.

Блок 81 Зона 1, 3, 5 вентилей.

Этот блок аналогичен блоку 78, но работает при наличии режима 1. Если микропроцессор распознал, что в данный момент имеет место зона нечетного вентиля, то программа переходит к блоку 85, если же зона четного вентиля, то к блоку 82.

Блок 82 Зона 2, 4,,6 вентилей.

Микропроцессор анализирует код состояния полярностей фаз для режима 1, и по этому коду определяет, зона какого вентиля имеет место в данный момент времени. Если идет зона четного вентиля, то программа переходит к блоку 86, если же ни одна из зон не идентифицирована, то к блоку 83.

Блок 83 Аварийное состояние 1.

Блок аналогичен блоку 80 с той лишь разницей, что состояние наступает в режиме 1.

Б приведенном примере программы предусмотрен только Аварийный останов 1.

Блок 84 Выбор очередного век- тиля режима О, подлежащего включению. Запуск ПУС.

5 О

|5 20 25

5

30

5

0

5

0

Блок работает, если имеет место зона 1, 3 или 5 вентиля в режиме 0. В ячейку памяти выделяемого на управляющие электроды тиристоров кода с именем СОЭ записывается код из таблицы соответственно 1, 3 или 5 вентиля, подлежащего включению в данной или следующей зоне. Затем формируется и вьщается код задания для ПУС и сигнал Вывод, после получения которогосчетчик 55запускается.

Блок 85 Выбор очередного вентиля режима 1, подлежащего включению. Запуск ПУС.

Блок работает, если имеет место зона 1, 3 или 5 вентиля в режиме 1, В ячейку памяти выдаваемого на управляющие электроды тиристоров кода с именем СОГ записывается код из таблицы соответственно 5, 1 или 3 вентиля, подлежащего включению в данной зоне. Затем формируется и вьщается код задания для ПУС и сигнал Вывод, после получения которого счетчик 55 запускается.

Блок 86 Выход из прерывания на расчет угла отпирания.

Осуществляется выход микропроцессора из режима прерывания от нуль- органов, и программа переходит к блоку 68, т.е. на прием входной информации и затем расчет следующего значения угла отпирания.

Блок 87 Прерывание от ПУС.

После запуска счетчик блока 17 начинает суммировать тактовые им- пульсы, приходящие от генератора 52, и после отсчета интервала времени, соответствующего рассчитанному углу отпирания, в момент обнуления воздействует через вход 16 на систему прерываний микропроцессора 4. Процессор прерывает свою работу и переходит на подпрограмму Прерывание от ПУС. Затем сигналом Ввод производится сброс триггера прерывания в блоке счетчика 17.

Блок 88 Включение выбранного вентиля.

В соответствии с кодом выбранного ранее в блоках 84 или 85 вентиля микропроцессор вьщает через регистр вьшода данных блока 6 в блок 18 усиления и распределения импульсов сигнал напряжения на включение выбранного вентиля, формирует импульс включения и затем снимает его.

Блок 89 Выход из прерывания.

21120524322

Происходит выход микропроцессо-С приходом импульса от следующего

ра из режима прерывания от ПУС, иочередного нуль-органа весь цикл

программа вновь приходит к той ко-работы программы повторяется от бломанде, перед которой произошло пре-ка 75 для зоны следующего венрывание.тиля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорное устройство для управления вентильным преобразователем | 1985 |

|

SU1356155A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1991 |

|

RU2077415C1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ПРОСТРАНСТВЕННОГО ПОЛОЖЕНИЯ ЦЕЛЕЙ НА ЭКРАНЕ ИНДИКАТОРА | 1988 |

|

SU1841101A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для вычисления временных интервалов микропроцессорных систем | 1980 |

|

SU960781A1 |

ЯК

+551

I f f4 а-II ч

J5

23

32 Га 2;

Фиг.2

Znnr

CjLiD

Редактор М. Циткина

Фиг 7

Составитель ь. Бунаков

Техред А.АчКорректор М. Максимишинец

8537/56Тираж 645Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-01-15—Публикация

1984-06-20—Подача