(54) ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Удлинитель импульсов | 1978 |

|

SU744944A1 |

| Делитель частоты | 1975 |

|

SU518870A1 |

| Устройство для измерения периодов следования импульсов при контроле перемещения магнитного носителя | 1989 |

|

SU1647644A1 |

| Устройство для контроля продолжительности работы электродвигателя подъемно-транспортного средства | 1988 |

|

SU1608715A1 |

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Формирователь импульсов | 1979 |

|

SU853787A1 |

| Делитель частоты с любым целочисленным коэффициентом деления | 1981 |

|

SU953736A2 |

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1390595A1 |

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

Изобретение относится к импульсной технике и может быть использовано в пересчетных устройствах вычислительной техники.

Известны делители частоты, выполненные на потенциальных элементах 1, 2j.

Известен делитель частоты, содержащий триггеры включенные по схеме двоичного счетчика, формирователь, логические элементы И-НЕ, НЕ и элемент задержки 1.

Однако такой делитель содержит избыточные формирователь и элемент задержки, что усложняет схему устройства и снижает быстродействие.

Известен также делитель частоты, который по своей технической сущности и достигаемому результату наиболее близок к изобретению 2J. Он содержит выходной элемент И-НЕ, последовательно включенные Т-триггеры еа основе Д-триггера, каждый из которых состоит из R 5триггера и трех элементов И-НЕ, причем ВЫХОД первого элемента И-НЕ первого Т-триггера соединен со входом третьего

элемента И-НЕ второго Т-триггера, выход первого элемента И-НЕ которого подключен ко входу третьего элемента И-НЕ третьего Т-триггера, в таком делителе частоты с дополнительными связями выходной сигнал вырабатывается с задержкой во времени относительно переднего фронта счетного импульса, что снижает быстродействие устройства и ограничивает его применение.

Цель изобретения-повышение быстродействия делителя частоты.

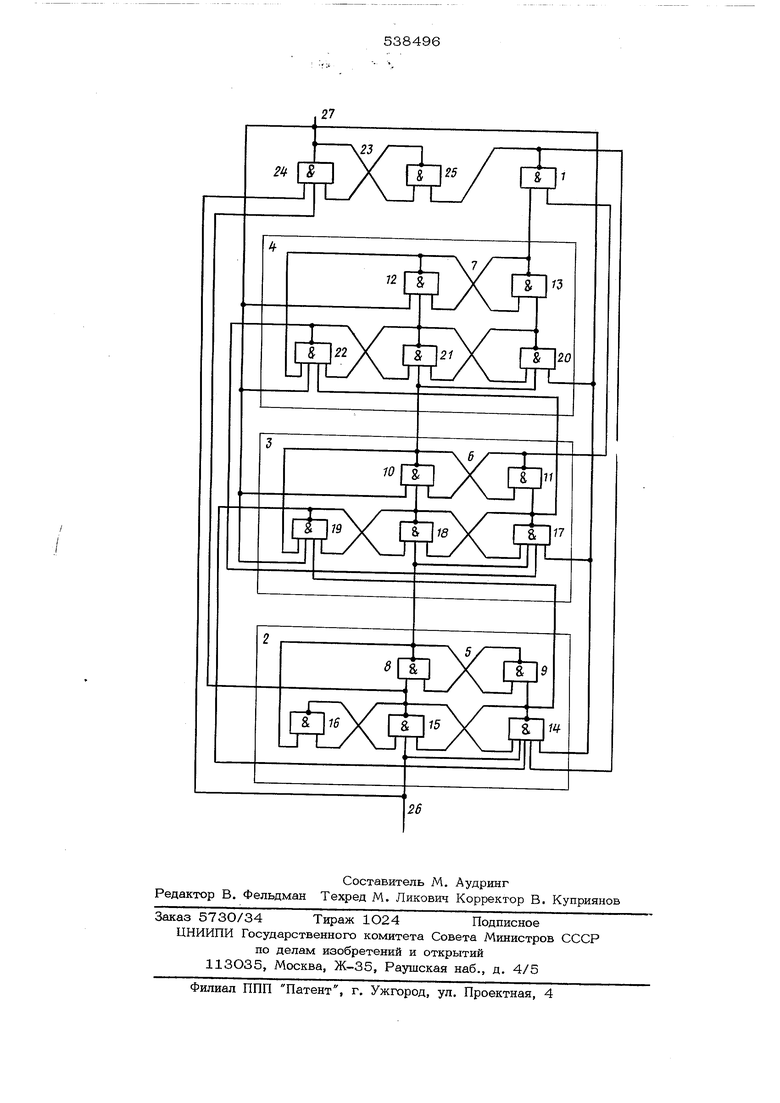

Указанная цель достигается тем, что в делитель частоты, содержащий выходной элемент И-НЕ, последовательно включенные Т-триггеры на основе Д-триггера, каждый из которых составлен из R - 5 триггера и трех элементов И-НЕ, введен триггер-формирователь , первый нулевой выход которого подключен к входной шине второй нулевой выход - к выходу второго элемента И-НЕ первого Т-триггера, при этом первые запрещающие входы первых элементов И-НЕ Т-триггеров объединены л подключены к выходной щине, к нулевым входам второго и третьего Т-триггеров, к запрещающим входам третьих элементов И-НЕ второго и третьего Т-триггера и к нулевому выходу триггера-формирователя, единичный вход которого соединен со вторым запрещающим входом первого элемента И-НЕ и с выходом выходного элемента И-НЕ, входы которого подключены к единичным выходам второго и третьего Т-триггеров. На чертеже представлена структурная электрическая схема делителя частоты. Делитель частоты содержит выходной элемент И-НЕ 1, последовательно включенные Т-триггеры 2,3 и 4 на основе Д-триггера, каждый из которых составлен из R - 5 триггера 5,6 и 7 на элементах И-НЕ 8-9, 10-11 и 12-13 и тре элементах И-НЕ 14, 15, 16; 17, 18, 19 и 20, 21, 22, триггер-формирователь 23 выходных сигналов на логических элементах И-НЕ 24, 25, один из нулевых входов триггера-формирователя 23 подключен к входной щине 26 устройства, а другой нулевой вход этого триггера подключен к выходу элемента И-НЕ 15 - Т-триг гера 2, дополнительный вход запрета эле мента И-НЕ 14 этого триггера подключен к выходной шине 27 устройства, к дополнительным нулевым входам R - 5 триггеров 6 и 7 и входам запрета элементов И-НЕ 17 и 19, 20 и 22 Т-триггеров 3 и 4 и к нулевому выходу ( на элементе И-НЕ 24) триггера-формирователя 23 вы ходных сигналов, единичный вход триггера-формирователя 23 и другой дополнительный вход запрета элемента И-НЕ 14 Т-триггера 2 подключены к выходу выход ного элемента И-НЕ 1, входы которого подключены к соответствующим единичным выходам (на элементе И-НЕ 11 и 13) Т-триггеров 3 и 4. Делитель частоты работает следующим образом. За исходное состояние принимается при сутствие низкого уровня потенциалов на входах элемента И-НЕ 1 и соответственно на выходах элементов И-НЕ 9, 11, 13; 15, 18, 21 и 25. При этом на выходах элемента И-НЕ 1 и элементов И-НЕ 8, 10, 12, 14, 16, 17, 20, 22 и 24, а также на входной шине 26 и выходной шине 27 устройства будут высокие уровни потенциа лов. При поступлении на входную щину 26 устройства низкого уровня потенциала на выходе элемента И-НЕ 15 Т-триггера 2 устанавливается высокий уровень потенциа ла, а на выходе элемента И-НЕ 16- низкий уровень потенциала. Е следующий момент времени при появлении на входной шине 26 устройства высокого уровня потенциала на выходе элемента И-НЕ устанавливается низкий уровень потенциала, от чего R - S триггер 5 Т-триггера 2 переходит в рабочее состояние, при котором на его элементах И-НЕ 9 и 8 присутствуют соответственно высокий и низкий уровни потенциалов, а элемент И-НЕ 16 Т-триггера 2 устанавливается в исходное состояние. При этом элементы И-НЕ 18 и 19 Т-триггера 3 срабатывают, а на их выходах соответственно будут высокий и низкий уровни потенциалов. В момент появления следующего низкого уровня потенциала первого счетного импульса элемент И-НЕ 14 Т-триггера 2 устанавливается в исходное состояние. При поступлении на входную шину 26 устройства входного импульса на выходе элемента И-НЕ 15 Т-триггера 2 вырабатывается инверсный счетный импульс, R - 5 триггер 5 переходит в исходное состояние, на выходе элемента И-НЕ 17 устанавливается низкий уровень потенциала, отчего срабатывает К - S триггер 6 на выходах элементов И-НЕ 11 и 1О которых будут соответственно высокий и низкий уровни потенциалов. Одновременно на выходах элементов И-НЕ 21 и 19 Т-триггеров 4 и 3 устанавливаются высокие уровни потенциалов, после чего на выходе элемента И-НЕ 22 появляется низкий уровень потенциала. По окончании поступления второго счетного импульса Т-триггер 2 подготовлен к счету следующего импульса, а Т-триггер 3 находится в рабочем состоянии. При поступлении на входную щину 26 устройства четвертого счетного импульса Т-триггер 4 срабатывает, при этом на выходе его элемента И-НЕ 20 будет низкий уровень потенциала, на выходах элементов И-НЕ 13 и 12 R - 5 триггера 7 соответственно высокий и низкий уровни потенциалов, а на выходе элемента И-НЕ 22 - высокий уровень потенциала. При пересчете щести счетных импульсов срабатьюают Т-триггеры 3 и 4, отчего на выходе элемента И-НЕ 1 появляется низкий уровень потенциала, а на выходе элемента И-НЕ 25 триггера-формирователя 23 устанавливается высокий уровень потенциала. Таким образом, устройство подготовлено к формированию выходного пересчетного импульса. При поступлении высокого уровня потен циала следующего счетного импульса на в ходе элемента И-НЕ 24 триггера-формирователя 23, н соответственно на выходной шине 27 устройства появляется низкий уровень потенциала, затем элементы И-НЕ 10-11, 17-19 и 12-13, 20-22 Т-триггеров 3 4,, а также выходной элемент 1 устанавливаются в исходное состояние. Таким образом, передний фронт выходного импульса появляется на выходной шине 27 устройства с задержкой только на время срабатывания одного элемента И-НЕ 24 триггера-формирователя 23, а не на время последовательного срабатывания пяти элементов , которое образуется при работе указанного прототипа. После окончания поступления пересчетного импульса на выходной шине 27 устройства, а также на выходах элементов И-НЕ 24 и 25 триггера-формирователя 23 устанавливаются исходные уровни потенциа лов. Формула изобретения Делитель частоты, содержащий выходной элемент И-НЕ, последовательно вклю ченные Т-триггеры на основе Д-триггера каждый из которых состоит из R - Sтриггера и трех элементов И-НЕ, причем выход первого элемента И-НЕ первого Т-триттера соединен со входом третьего элемента И-НЕ второго Т-триггера, выход первого элемента И-НЕ которого подключен ко входу третьего элемента И-НЕ третьего Т-триггера, отличающийс я тем, что, с целью повышения быстродействия, в него введен триггер-формирователь, первый нулевой выход которого подключен к входной шине, второй нулевой выход - к выходу второго элемента И-НЕ первого Т-ориггера, при этом первые запрещающие входы первых элементов И-НЕ Т-триггеров объединены и подключены к выходной шине, к нулевым входам второго и третьего Т- риггеров, к запрещающим входам третьих элементов И-НЕ второго и третьего Т-триггеров и к нулевому выходу триггера-формирователя, единичный вход которого соединен со вторым запрещающим входом первого элемента И-НЕ и с выходом выходного элемента И-НЕ, входы которого подключены к единичным выходам второго и третьего Т-триггеров. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 352403, кл.Н 03 К 23/О2 от 21.12.70г. 2.Авторское свидетельство СССР №324713,кл.Н 03 К 23/02 от31.03.69г. (прототип).

Авторы

Даты

1976-12-05—Публикация

1975-10-13—Подача