(54) ШЛИТЕ ЛЬ ЧАСТОТЫ С ЛЮБЫМ

ЦЕЛОЧИСЛЕННЫМ КОЭФФИЦИЕНТОМ Изобретение относится к импульсной технике, в частности к делителям частоты, может быть использовано в автоматике, вычислительной технике и радиотех нике. По основному авт. св. № 843246 известен делитель частоты с любым цело численным коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной, а выходы разрядов, кроме первого и второг подключены ко входам дешифратора, регистр сдвига и элементы И, первые входы которых и первый С-вход регистра сдвига объединены и подключены к входной шине, второй С-вход регистра сдвига подключен к выходу первого элемента И, вторым входом соединенного с выходом первого разряда счетчика импульсов а вход регистра сдвига соединен с выходом дешифратора, D -входы о&ьединены к подключены к выходу второго разряда счетчика итипульсоЕ, а выход первого разряда регистра сдвига подключен к ДЕЛЕНИЯ Второму входу второго элеметга И, выход которого соединен с установочным входом счетчика импульсов l . Недостаток известного устройства ограниченные функциональные возможное ти, так как оно he может быть использовано в составе более сложных устройств, робота которых должна быть синхронизирована отдельным запускающим сигналом в случае, когда запускающий сигнал имеет значительную длительность а моментом синхронизации должен быть момент появления его переднего фронта. Целью нзобрютения является расширение функциональных возможностей делителя частоты с любым целочисленным коэффициентом деления, путем обеспечения синхронизации работы с передним фронтом запускающего сигнала, а также формирования укороченного сигнала по переднему фронту запускающего скгнала, Поставленная цель достигается тем, что в делитель частоты с любым целочисленным коэффициентом деления введены D- риггер и дополнительный эле мент И, первый вход которого соединен с выходом последнего разряда регистра сдвига и С-входом D-триггера, второй вход - с D - и R -входами D -триггера, и дополнительной входной шиной, третий вход - с выходом D-триггера, а выход с дoпoлнитeльнымV-входом регистра сдвига и стробирующим входом дешифра тора.

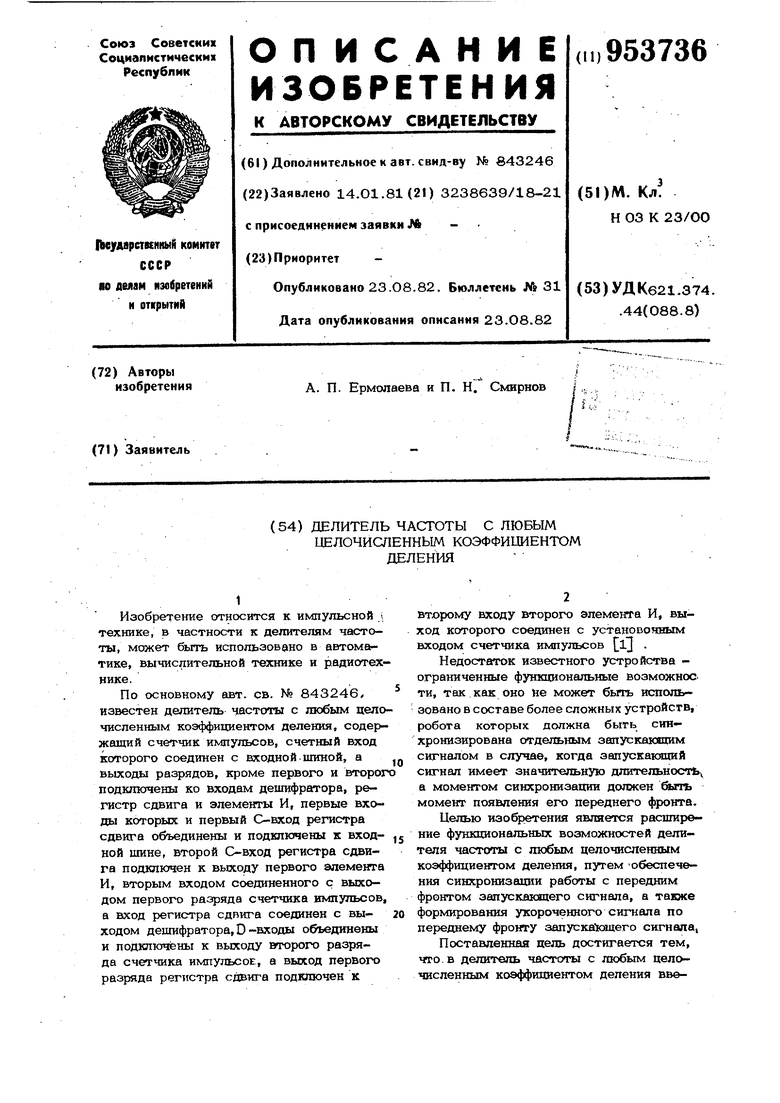

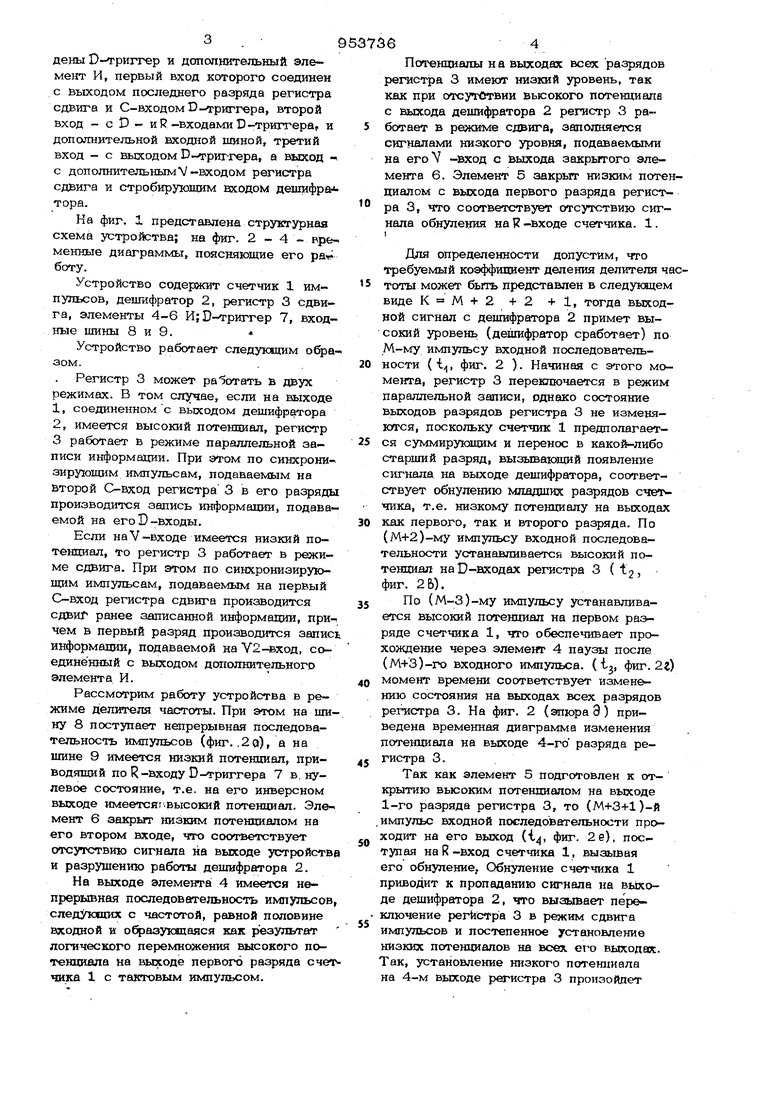

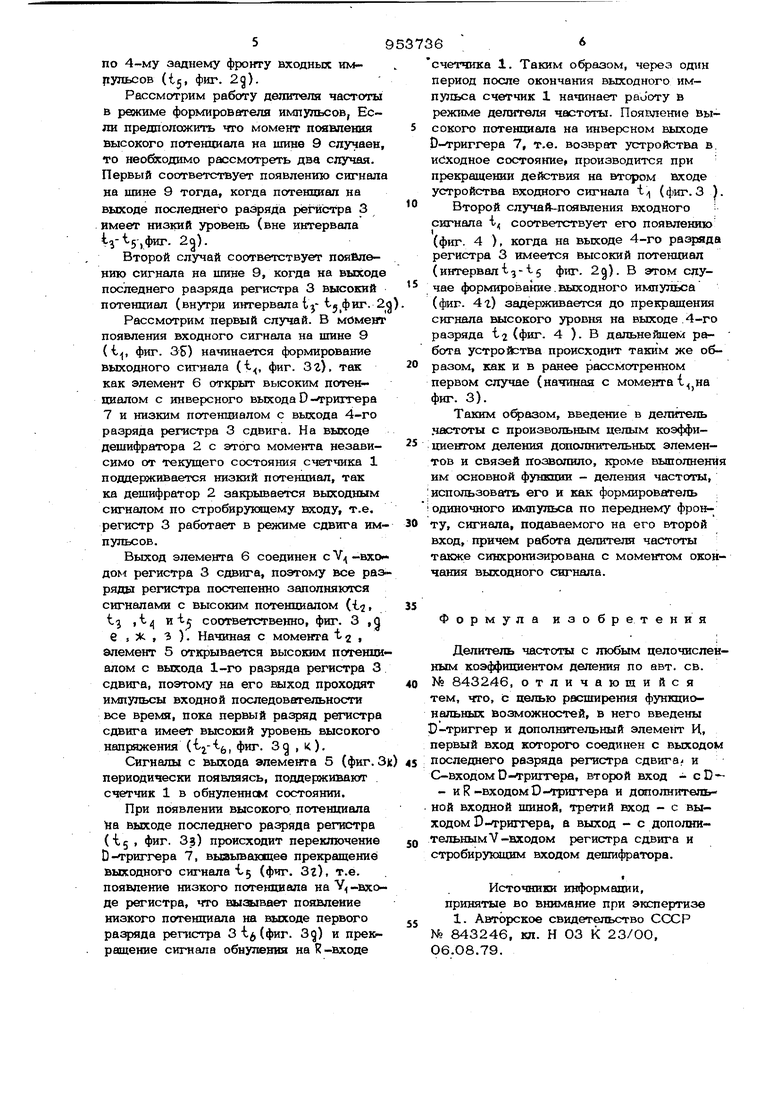

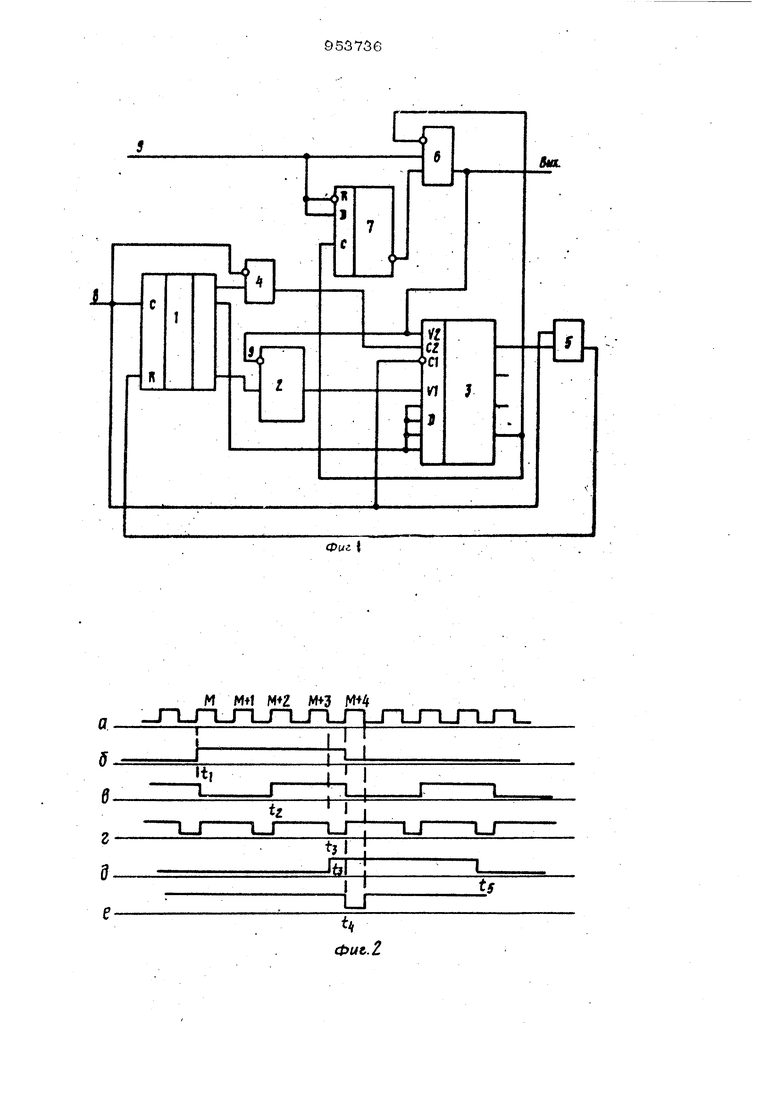

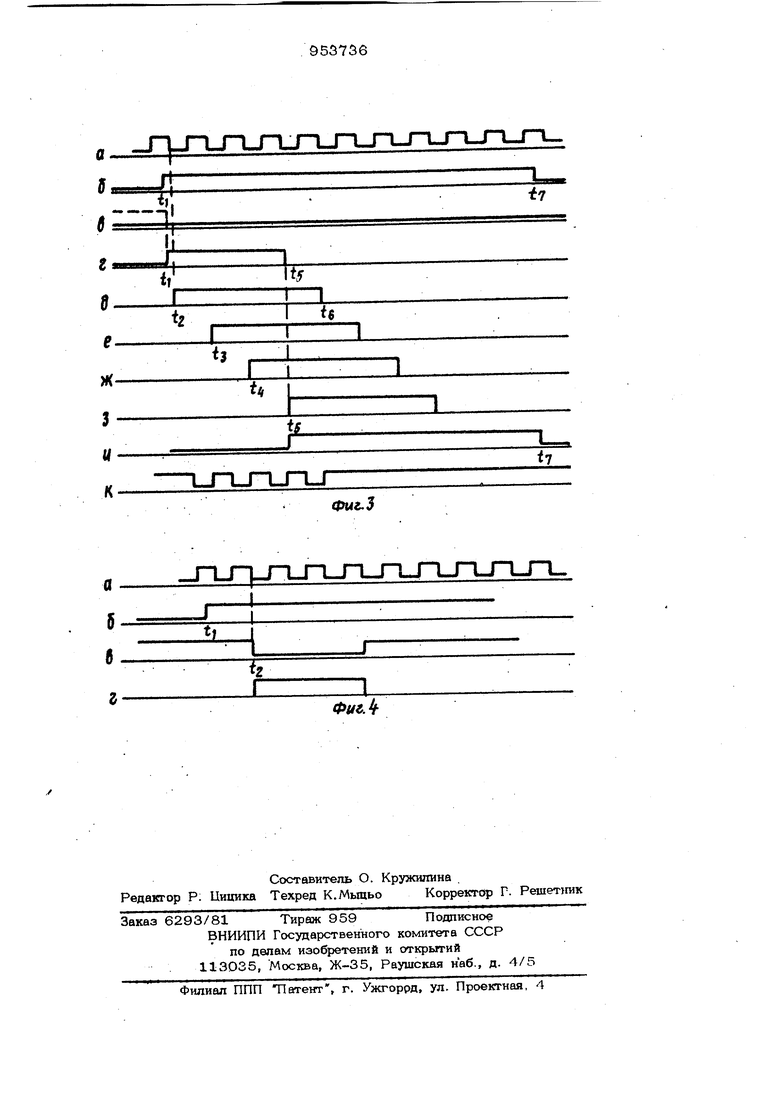

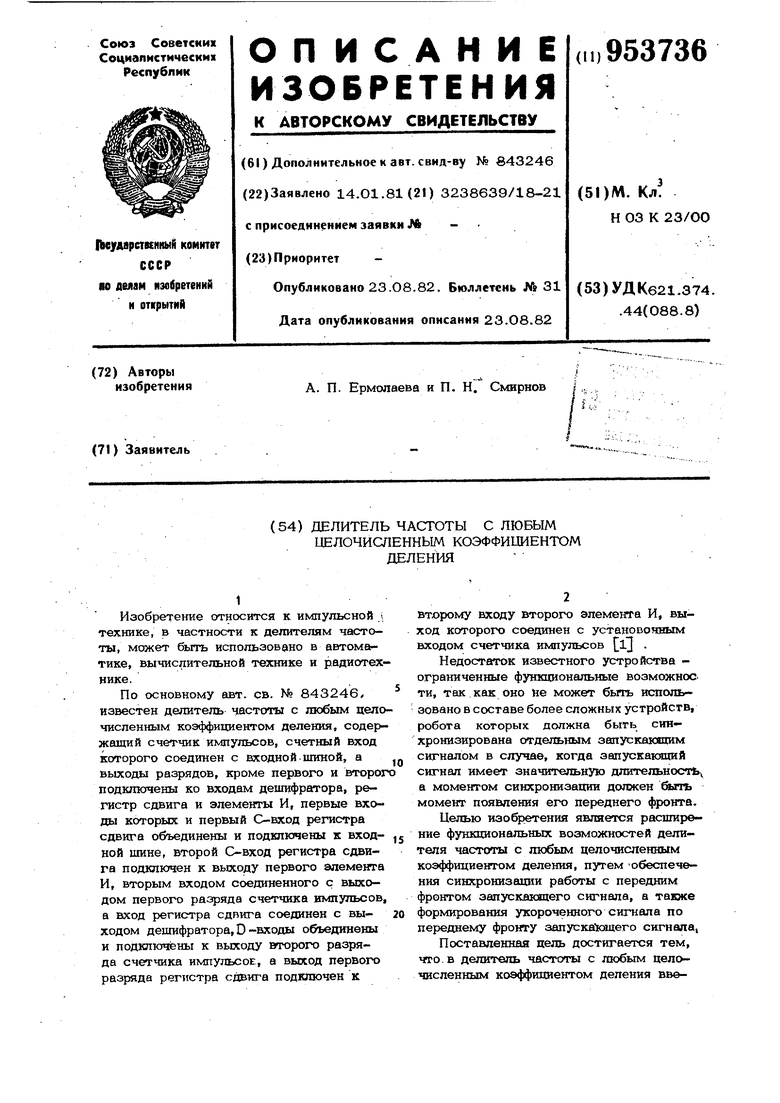

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - 4 - временные диаграммы, поясняющие его ра,боту.

Устройство содержит счетчик 1 импульсов, дешифратор 2, регистр 3 сдвига, элементы 4-6 И;С- риггер 7, входдате шины 8 и 9.

Устройство работает следующим образом.

Регистр 3 может работать в двух режимах. В том , если на выходе

1,соединенном с выходом дешифратора

2,имеется высокий потенциал, регистр 3 работает в режиме параллельной записи информации. При этом по синхронизируюшим импульсам, подаваемым на второй С-вход регистра 3 в его разряды производится запись информации, подаваемой на его D-входы.

Если наV-входе имеется низкий потендиал, то регистр 3 работает в режиме сдвига. При этом по синхронизируюпотм импульсам, подаваемым на первый С-вход регистра сдвига производится сдвиг ранее записанной информации, причем в первый разряд производится запис информации, подаваемой на У2-вход, соединённый с выходом дополнительного элемента И.

Рассмотрим работу устройства в режиме д елителя частоты. При этом на шину 8 поступает непрерывная последовательность импульсов (фиг. .2в), а на шине 9 имеется низкий потенциал, приводящий по R-ВХОДУ D--триггера 7 в. нулевое состояние, т.е. на его инверсном выходе имеетсят.высокий потенциал. Элемент 6 закрыт низким потенциалом на его втором входе, что соответствует отсутствию сигнала на выходе устройств и разрушению работы дешифратора 2.

На выходе элемента 4 имеется непрерывная последовательность импульсов следующих с частотой, равной половине входной и образующаяся как рнезультат логического перемножения высокого потенциала на выходе первого разряда счетчика 1 с тавгговым импульсом.

Потенциалы на выходах всех разрядов регистра 3 имеют низкий уровень, так как при отсутствии высокого потенциала с выхода дешифратора 2 регистр 3 работает в режиме сдрига, заполняется сигналами низкого уровня, подаваемыми на eroV -вход с выхода закрытого элемента 6. Элемент 5 закрыт низким потенциалом с выхода первого разряда регистра 3, что соответствует отсутствию сигнала обнуления на R-входе счетчика. 1. 1

Для определенности допустим, что требуемый коэффициент деления делителя час5 тоты может быть представлен в следующем виде + 2 +2 +1, тогда выходной сигнал с дешифратора 2 примет высокий уровень (дешифратор сработает) по М-му импуттьсу входной последователь0 ности (i, фиг. 2 ). Начиная с этого момента, регистр 3 переключается в режим параллельной записи, однако состояние выходов разрядов регистра 3 не изменяются, поскольку счетчик 1 предполагает5 ся суммируюшим и перенос в како -либо старший разряд, вызьюаюший появление сигнала на выходе дешифратора, соответствует обнулению младших разрядов счет чика, т.е. низкому потенциалу на выходах

0 как первого, так и второго разряда. По (М+2)-му импульсу входной последовательности устанавливается высокий потенциал наП-В(Ходах регистра 3 ( t2, фиг. 26).

5 По (М-З)-му импульсу устанавливается высокий потенциал на первом разряде счетчика 1, что обеспечивает прохождение через элемент 4 паузы после (М+3)-1Ч) входного импульса. (ij, фиг. 2i)

0 момент времени соответствует изменению состояния на выходах всех разрядов регистра 3. На фиг. 2 (эпюра 9) приведена временная диаграмма изменения потенциала на выходе 4-го разряда ре5 гистра 3.

Так как элемент 5 подготовлен к открытию вьюоким потенциалом на выходе 1-го разряда регистра 3, то (М+3+1)-й .импульс входной последовательности проходит на его выход (i, фиг. 2е), поступая на R-вход счетчика 1, вызывая его обнуление, Обнуление счетчика 1 приводит к пропаданию сигнала на выходе дешифратора 2, что вызывает пере клю дание регистра 3 в режим сдвига импульсов и постепенное установление низких потенциалов на всех его выходах. Так, установление низкого потенпиала на 4-м выходе регистра 3 произойдет ПО 4-му заднему фронту входных импупьсов (t, фиг. 2д). Рассмотрим работу делителя частоты в режиме формирователя импульсов, Если предположить что момент появления высокого потенциала на шине 9 случаен то необосодимо рассмотреть два случая. Первый соответствует появлению сигнал на шине 9 тогда, когда потенциал на выходе последнего разряда регистра 3 имеет низкий уровень (вне интервала .,фиг. 2). Второй случай соответствует появлению сигнала на шине 9, когда на выходе последнего разряда регистра 3 высокий потенциал (внутри интервала tj-tJ фиг. 2 Рассмотрим первый случай. В момент появления входного сигнала на шине 9 (i;(, фиг. 35) начинается формирование выходного сигнала (t, фиг. 3z). так как элемент 6 открыт высоким потенциалом с инверсного выхода D -триггера 7 и низким потенциалом с выхода 4-го разряда регистра 3 сдвига. На выходе дешифратора 2 с этого момента независимо от текущего состояния счетчика 1 поддерживается низкий потенциал, так ка дешифратор 2 закрывается выходным сигналом по стробирукяцему входу, т.е. регистр 3 работает в режиме сдвига им пульсов. Выход элемента 6 соединен с V -вхо дом регистра 3 сдвига, поэтому все раз ряды регистра постепенно заполняются сигналами с высоким потенциалом (t, t.3 Л соответственно, фиг. 3 ,g е , ж , 3 ). Начиная с момента t , элемент 5 открывается высоким потенци алом с выхода 1-го разряда регистра 3 сдвига, поэтому на его выход проходят импульсы входной последовательности все время, пока первый разряд регистра сдвига имеет высокий уровень высокого напряжения (. Фиг. 3 , к). Сигналы с выхода элемента 5 (фиг. З периодически появляясь, поддерживают счетчик 1 в обнуленном состоянии. При появлении высокого потенциала на выходе последнего разряда регистра (ig фиг. Зз) происходит переключение D-триггера 7, вызывающее прекращение выходного сигнала is (фиг- Зг), т.е. появление низкого потенциала на V -входе регистра, что выбывает появление низкого потенциала на выходе первого р&зряца регистра 3 i (фиг. Зд) и прекращение сигнала обнуления на R-входе счетчика 1. Таким , через один период после окончания выходного импульса счетчик 1 начинает раиоту в режиме делителя частоты. Появление высокого потенциала на инверсном выходе D-триггера 7, т.е. возврат устройства в. исходное состояние производится при прекращении действия на втором входе устройства входного сигнала t (фиг. 3 ). Второй случай-появления входного сигнала i соответствует его появлению (фиг. 4 ), когда на выходе 4-го разряда регистра 3 имеется высокий потенциал (интервалi3 5 Ф. 2д). В этом случае формирование. выходного импульса (фиг. 4г) задерживается до прекращения сигнала высокого уровня на выходе 4-го разряда tj (фиг. 4 ). В дальнейшем работа устройства происходит таким же образом, как и в ранее рассмотренном первом случае (начтааая с момента фиг. 3). Таким образом, введение в делитель .частоты с произвольным целым коэффициентом деления дополнительных элементов и связей позволило, кроме выполнения им основной функции - деления частоты, использовать его и как формирователь одиночного импутгьса по переднему фронту, сигнала, подаваемого на его второй вход, причем работа делителя частоты также синхронизирована с моментом окончания выходного сигнала. Формула изобретения Делитель частоты с любым целочисленным коэффициентом деления по авт. св. № 843246, отличаюши йся тем, что, с целью расширения функциональных возможностей, в него введены Р-триггер и дополнительный элемент Н, первый вход которого соединен с выходом последнего разряда регистра сдвига/ и С-входомО-/триггера, второй вход . cD- и R-входом О-диггера и дополнительной входной шиной, третий вход - с выходом D- рипгера, а выход - с дополнительнымУ-входом регистра сдвига и стробирукяцим входом дешифратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 843246, кл. Н 03 К 23/00, 06.08.79. М М+3 М+4

t5

Т б

.

Фиг. 5

f

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с любым целочисленнымКОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843246A1 |

| Делитель частоты с любым целочисленным коэффициентом деления | 1981 |

|

SU953735A2 |

| Делитель частоты | 1980 |

|

SU921095A1 |

| Делитель частоты следованияиМпульСОВ | 1979 |

|

SU839066A1 |

| Устройство для задержки импульсов | 1980 |

|

SU921066A1 |

| Устройство для задержки импульсов | 1980 |

|

SU951677A1 |

| Цифровой измеритель скважности прямоугольных импульсов | 1990 |

|

SU1725152A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1986 |

|

SU1368993A1 |

| Устройство для генерирования функций | 1979 |

|

SU851424A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

Фиг,Л

Авторы

Даты

1982-08-23—Публикация

1981-01-14—Подача