3

jianioro сдвига, a э.мпттеры трапз 1сторов ii вторые э.мпттеры миогоэмиттериых траизиеторов 1Юл1ключены к шипе прямого едвига.

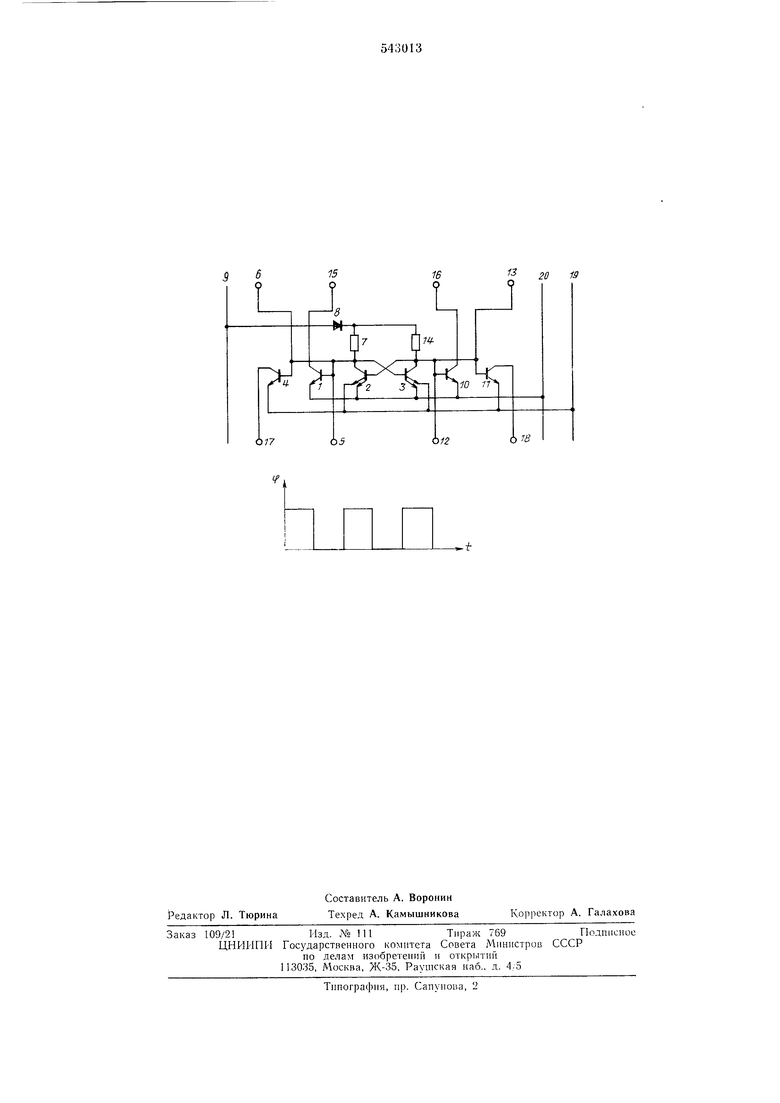

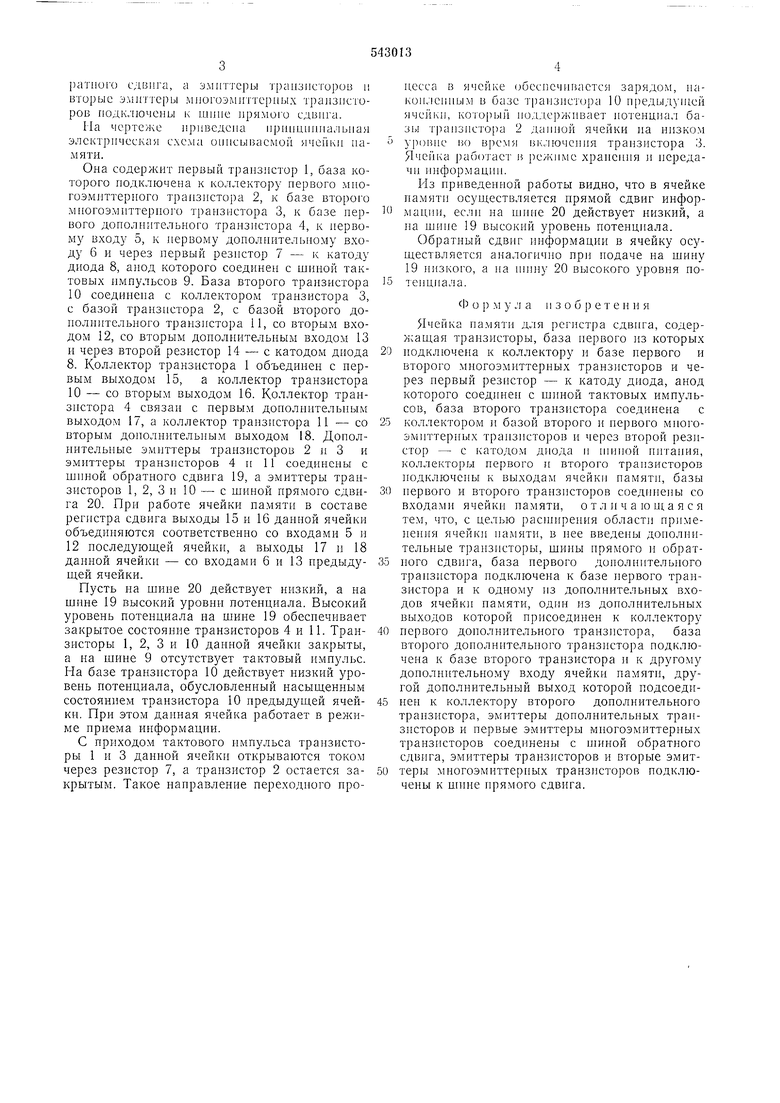

Ма чертеже приведена принципиальная электричес1 ая ехема 01 иеываемой яче11кн памяти.

Она еодержнт первый транзпстор 1, база которого подключена к коллектору первого миогоэмнттериого транзнетора 2, к базе второго многоэмнттерного транзиетора 3, к базе нервого дополнительного транзиетора 4, к нервому входу 5, к нервому дополнительному входу 6 и через первый резнетор 7 - к катоду диода 8, анод которого соединен е шиной тактовых нмпульеов 9. База второго траизиетора 10 соединена е коллектором транзистора 3, с базой транзистора 2, с базой второго донолпительного транзистора 11, со вторым входом 12, со вторым дополнительным входом 13 и через второй резистор 14 - с катодом диода 8. Коллектор транзистора 1 объединен с первым выходом 15, а коллектор транзистора 10 - со вторым выходом 16. Коллектор транзистора 4 связан с первым доиолнительным выходом 17, а коллектор транзнетора 11 - со вторым доиолннтельным выходом 18. Донолнительные эмиттеры транзисторов 2 и 3 и эмиттеры транзисторов 4 и 11 соединены с шииой обратиого сдвига 19, а эмиттеры траизиеторов 1, 2, 3 и 10 - с шииой прямого сдвига 20. При работе ячейки иамяти в составе регистра сдвига выходы 15 и 16 даииой ячейки объединяются соответственно со входами 5 и 12 последующей ячейки, а выходы 17 и 18 данной ячейки - со входами 6 и 13 нредыдугцей ячейки.

Пуств на шине 20 действует низкий, а иа шине 19 высокий уровии потенциала. Высокий уровень потеициала на шине 19 обеспечивает закрытое состояиие транзисторов 4 и И. Транзисторы 1, 2, 3 и 10 даииой ячейки закрыты, а на шине 9 отсутствует тактовый . На базе траизнстора 10 действует низкий уровень потенциала, обусловленный насыщенным состоянием транзистора 10 предыдущей ячейки. При этом данная ячейка работает в режиме ириема информации.

С приходом тактового импульса транзисторы 1 и 3 даииой ячейки открываются током через резистор 7, а траизистор 2 остается закрытым. Такое наиравлеиие переходиого иро4

цесса в ячейке (обеспечивается зарядом, иа1 оилениым в базе т|)анзист()})а 10 )еды,1у1исй ячейки, который иодллрживает иотенциал базы T Kui3HCTOpa 2 данной ячейки иа низком уроиие 1Ю время включеиия транзистора 3. Яче1и а работает 15 режиме хранения и иередачи ииформации.

Из приведениой работы видно, что в ячейке иамяти осуществляется прямой сдвиг ииформации, если на шиие 20 действует низкий, а иа шиие 19 высокий уровень потенцнала.

Обратный сдвнг ииформации в ячейку осуществляется аналогично при подаче иа шииу 19 низкого, а на ншиу 20 высокого уровия иотеициала.

Ф о р м у л а и 3 о б р е т е и и я

Ячейка иамяти для регистра сдвига, содер ;ащая траизисторы, база иервого из которых

иодключеиа к коллектору и базе первого и второго миогоэмиттериых транзнсторов и через иервый резистор - к катоду диода, анод которого соедннеи с шниой тактовых импульсов, база второго транзнетора соединена с

коллектором и базой второго и нервого многоэмиттерных транзисторов и через второй резистор - с катодо.м диода и пппюй иитапия, коллекторы первого и второго транзисторов подключеиы к выходам ячейки памятп, базы

первого и второго траизисторов соедииены со входами ячейки иамяти, о т л и ч а ю И1,а я с я тем, что, с целью раоииреиия области примепення ячейки памяти, в иее введеиы дополиительные транзисторы, шииы ирямого и обратиого едвига, база первого дополиительиого траизиетора подключена к базе иервого транзистора и к одиому из дополнительных входов ячейки намяти, одпи из дополиительиых выходов которой присоединен к коллектору

иервого дополнительного траизиетора, база второго донолнительиого транзистора подключена к базе второго транзистора и к другому доиолнительному входу ячейки намятн, другой дополнительный выход которой иодсоединен к коллектору второго дополнительного траизнстора, эмиттеры дополнительных траизисторов и первые эмиттеры многоэмиттериых транзисторов соединены с шиной обратного сдвига, эмиттеры транзисторов и вторые эмиттеры миогоэмиттерных траизисторов подключеиы к шиие ирямого сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент "и-не | 1975 |

|

SU595861A1 |

| Линейный пропускатель сигналов | 1974 |

|

SU539375A1 |

| Устройство для записи информации в магнитный тонкопленочный накопитель | 1970 |

|

SU483704A1 |

| РАЗРЯД ДИНАМИЧЕСКОГО РЕГИСТРА СДВИГА | 1972 |

|

SU324711A1 |

| АНАЛОГОВЫЙ РЕГИСТР СДВИГА | 1970 |

|

SU275533A1 |

| Устройство для управления силовым транзистором | 1976 |

|

SU574845A1 |

| УСТРОЙСТВО для СРАВНЕНИЯ | 1970 |

|

SU269223A1 |

| ОДНОФАЗНЫЙ ТРИГГЕР | 1973 |

|

SU399012A1 |

| Автогенераторный дифференциально- трансформаторный преобразователь перемещений | 1978 |

|

SU769306A1 |

| Запоминающее устройство | 1976 |

|

SU613405A1 |

Авторы

Даты

1977-01-15—Публикация

1973-12-28—Подача