1

Изобретение относится к области микроэлектроники и может найти применение в интегральных схемах (ИС) запоминающих устройств (ЗУ).

Известны ЗУ, содержаш,ие матрицу элементов памяти и разрядные усилители считывания, в которых коллекторы транзисторов усилителей считывания соединены шинами считывания 1. Такая коллекторная связь обеспечивает наиболее нростую схему ЗУ.

Наиболее близким техническим решением к изобретению является ЗУ, содержаш,ее матрицу элементов памяти, разрядные усилители считывания, выполненные на двух транзисторах, эмиттеры которых соединены с разрядными шинами матрицы, а базы - с уиравляюш,ими шинами и шины считывания.

Недостаток известных ЗУ и ИС большой информационной емкости состоит в относительно невысоком быстродействии, связанном с длительным процессом перезаряда емкостей в узлах объединения коллекторов траизисторов усилителей считывания.

Цель изобретения - повышение быстродействия ЗУ.

Эта цель достигается тем, что оно содержит развязывающие элементы, например диоды, причем ко.клекторы первого и второго транзисторов усилителей считывания объединены в группы п подключены к катодам соответствующих диодов, аноды которых соединены с шинами считывания.

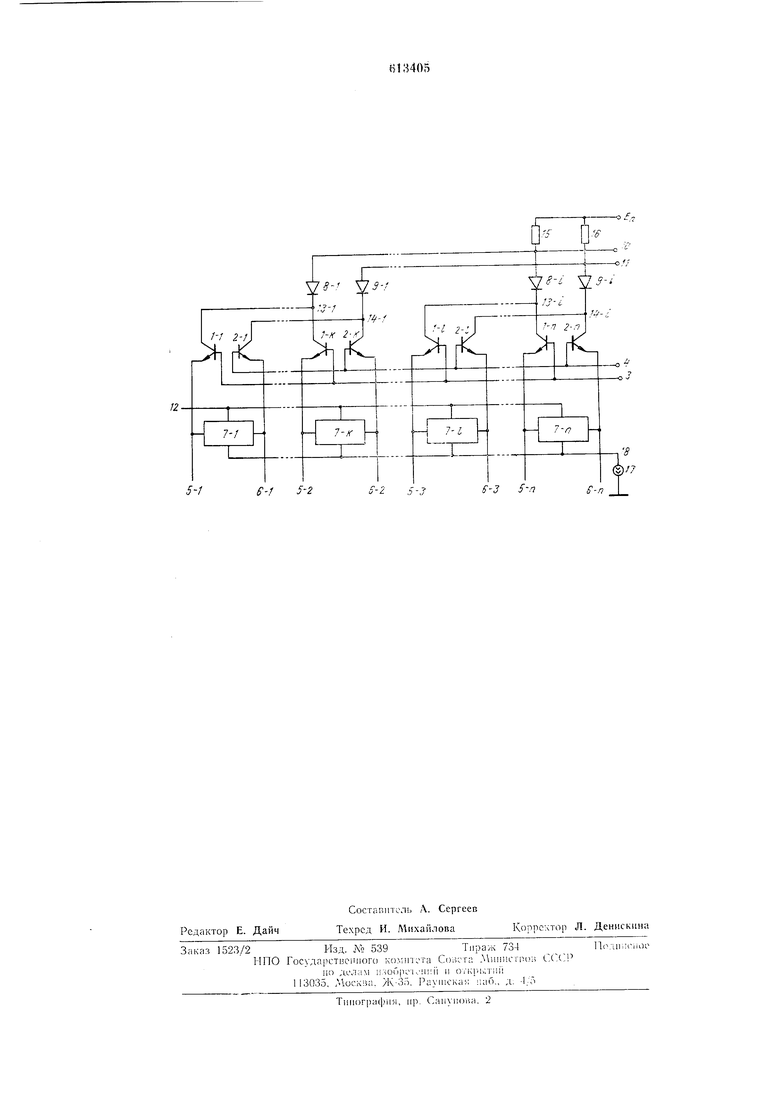

На чертеже представлена схема предлагаемого ЗУ.

Устройство содержнт разрядные усилители сч1ггывания (на чертеже не обозначены), вьпкхшенные на двух транзнсторах 1 - 1 и 2-1, 1-2 и 2-2... 1-я и 2-п, базы которых соединены сжду собой соответственно управляющими шинами 3 и 4, а эмиттеры иодсоеднис-ны к соответствующим разрядным шинам 5-1 и 6-1, 5-2 н 6-2... 5-п п {)- -п лкпрпцы (на чертеже не обозначено) э:1сменто15 памяти 7-1, 7-2... 7-п, развязывающие дгюды 8-1 п 9-1, 8-2 п 9-2... 8-L и 9-/, аноды которых соединяются с шинами считывания 10 п 11 соответственно.

На чертеже показана одна строка п-разрядной ,1атриць, состоящая из элементов иамяти 7-1... 7-п, которые соединяются с cooTBCTCTByioLHiiMH разрядными шинами 5 и 6 и с шиной строки 12. Кол.чекторы Tj)ai;3ncTOpOi; объединены в груииы ио к коллокто Ю15. К общим кол.чекторным узлам 13-1 и 4-1, 13--2 н , 13-i...l4-i каждой группы подключены катоды соответствующих диодов 8 и 9. Резпстроы 15 и

16, одни выводы которых соединены с шииами 10 и II сооП5етствен1Ю, а другие подключены к общей шнне источника ннтаиия Е„, обесиечива от режнм работы усилителей считывания. Источник тока 17, подключенный к шине 18 строкн элементов намяти, обеснечивает режим питания строки.

ЗУ работает следующим образом.

В режиме хранения информации через транзисторы 1 и 2 токи не протекают. Поэтому потенциалы щин 10 и 11, являющихся выходами сигнала считывания, равны высокому уровню напряжения и равны между собой. При считывании информации потенциалы баз транзисторов I и 2 на шинах 3, 4 равны и выше потенциала базы включенного транзистора в невыбранном элементе памяти. Потенциал базы включенного транзистора выбранного элемента памяти выше, а потенциал базы выключенного транзистора ниже потенциала баз транзисторов 1, 2. Будем считать для определенности, что хранению логической «1 соответствует такое состояние элемента, при котором транзистор элемента памяти, связанный с шиной 5, выключен, а транзистор, связанный с шиной 6, включен. Пусть, например, элемеит памяти хранит «I и разрешается выборка информации из 1 разряда. При этом в разрядные щины 5-1 и 6-1 поступают разрядные токи. В этом случае при считывании, когда потенциал щины 12 повышается, разрядный ток шины 6-1 переключается в транзистор элемента памяти 7-1. Поэтому транзистор 2-1 выключен и, поскольку через транзисторы 2-2... 2-п других разрядов токи не протекают, диоды 9-1... 9-2 выключеиы и иа шине 11 высокий уровень ианряжеиия. С другой стороны, разрядный ток шины 5-1, являющийся током считывания, переключается в транзистор 1 - 1 и соответствующий диод 8-1 включается. Через другие транзисторы 1 токи не протекают. Ток, протекающий через диод 8-I и резистор 15,

приводит к поинжению иотенциала И1ииы

10.Разиост) иотсициалов шин 10 и 11 представ.чяет сигпал считаппой ин()ормацпи. Аналогично происходит считывание логического «О, при этом разность потенциалов шин 10 п 1 имеет иротивоположный знак. Поскольку коллекторные узлы 13-1 и 14- 1руппы, связанной с выбираемым разрядом, развязаны от коллекторных узлов

других групп диодами 8 и 9, имеющими малые значения емкостей, емкости узлов этих групп практически пе влпяют на скорость перезаряда узлов 13 и 14 выбираемого раз ряда. Введеиие развязывающих диодов приводит к небольшому усложнению схемы ЗУ и впосит паразитные емкости в шины 10 и

11.Однако, поскольку число диодов значительно меньше числа транзисторов усилителей считывания, в схеме обеспечивается

существенный выигрыш по быстродействию. Конкретное значение числа транзисторов лтилителей считывания, объединяемых в группу k, определяется в соответствии с требованиями к ИС ЗУ.

Фо р м у л а и 3 о о р е т е п и я

Запоминающее устройство, содержащее матрицу элементов памяти, разрядные усилители считывания, выполнеииые на двух

транзисторах, эмиттеры которых соединены с разрядными шинами матрицы, а базы - с управляющими шинами, и щины считывания, отличающееся тем, что, с целью увеличения быстродействия устройства, оно

содержит развязывающие элементы, например диоды, причем коллекторы иервого и второго траизисторов усилителей считывания об-ьединены в груииы и подключены к катодам соответствующих диодов, аноды

которых соединены с шипами считывания.

Источники информации, принятые во в} имание при экспертизе

1. Пате1гг США Хо 3919566 кл. 307-235, 1975.

-7 p-i V7 a. .

0 V

/7 WJ

S3 5-п

5-3

-/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Запоминающее устройство | 1983 |

|

SU1238156A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Запоминающее устройство | 1975 |

|

SU613404A1 |

| Запоминающее устройство | 1979 |

|

SU799002A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

Авторы

Даты

1978-06-30—Публикация

1976-07-27—Подача