и коммутатор подключены к соответствующим входам первого элемента задержки.

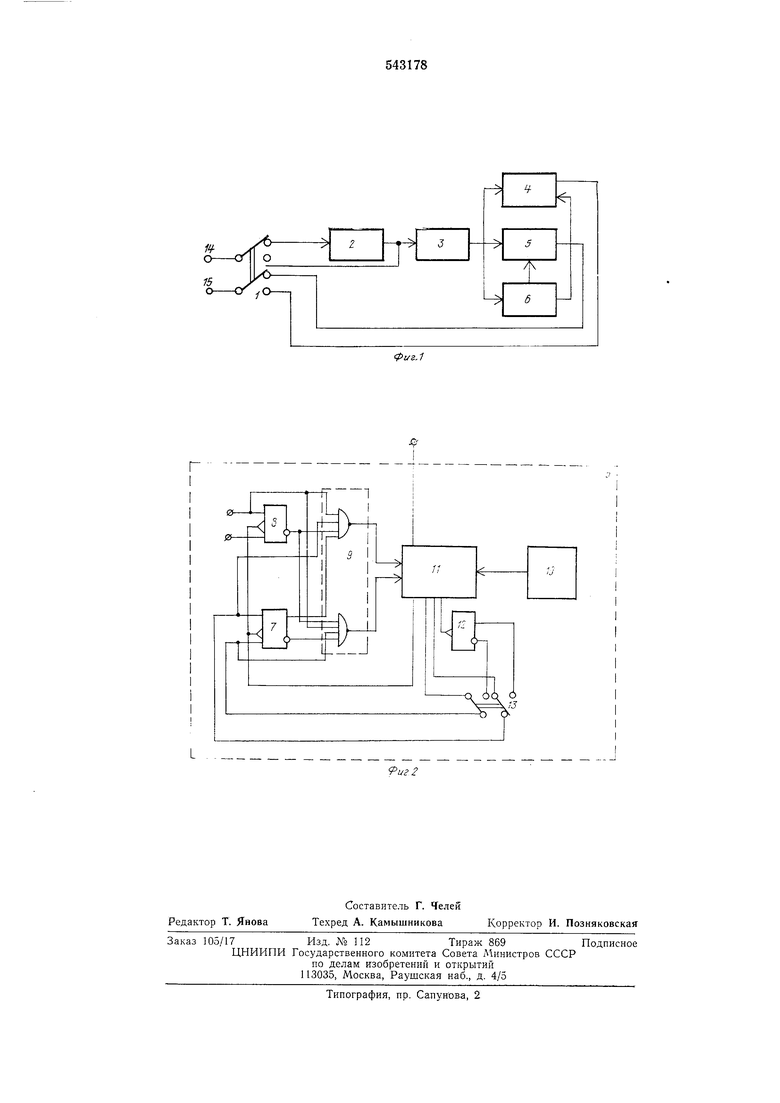

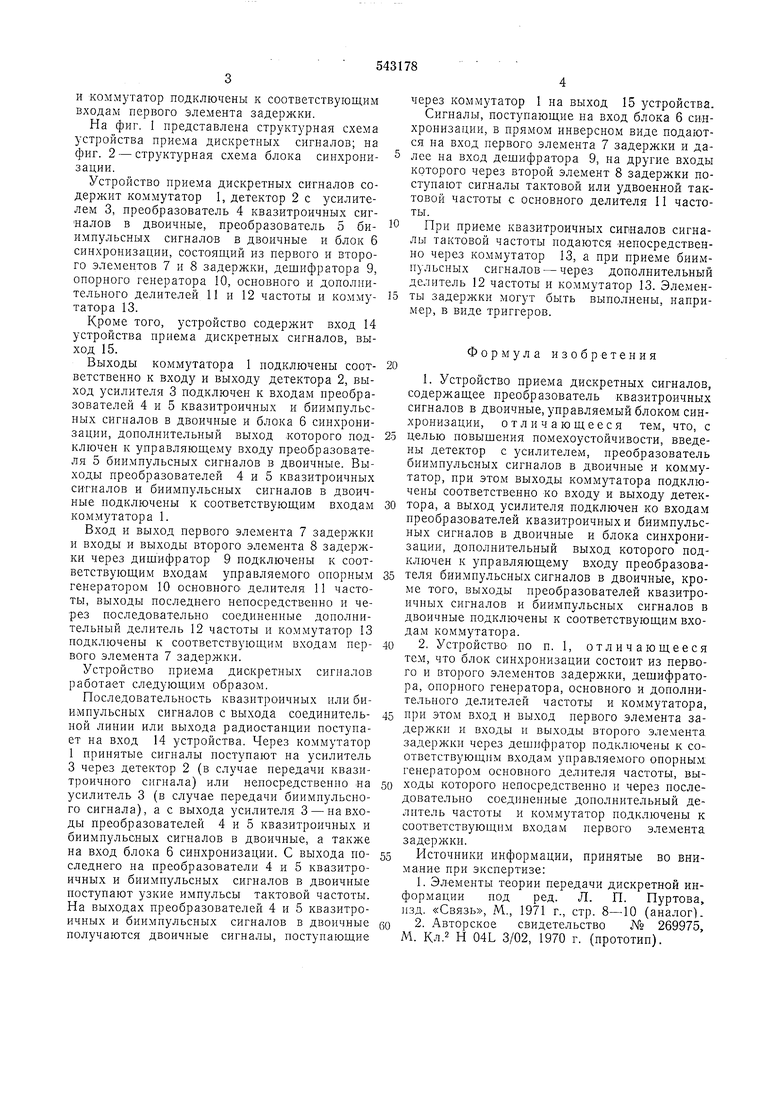

На фиг. 1 представлена структурная схема устройства приема дискретных сигналов; на фиг. 2 - структурная схема блока синхронизации.

Устройство приема дискретных сигналов содержит коммутатор 1, детектор 2 с усилителем 3, преобразователь 4 квазитроичных сигналов в двоичные, преобразователь 5 биимпульсных сигналов в двоичные и блок 6 синхронизации, состоящий из первого и второго элементов 7 и 8 задержки, дешифратора 9, опорного генератора 10, основного и дополнительного делителей 11 и 12 частоты и коммутатора 13.

Кроме того, устройство содержит вход 14 устройства приема дискретных сигналов, выход 15.

Выходы коммутатора 1 подключены соответственно к входу и выходу детектора 2, выход усилителя 3 подключен к входам преобразователей 4 и 5 квазитроичных и биимпульсных сигналов в двоичные и блока 6 синхронизации, дополнительный выход которого подключен к управляющему входу преобразователя 5 биимпульсных сигналов в двоичные. Выходы преобразователей 4 и 5 квазитроичных сигналов и биимпульсных сигналов в двоичные подключены к соответствующим входам коммутатора 1.

Вход и выход первого элемента 7 задержки и входы и выходы второго элемента 8 задержки через дишифратор 9 подключены к соответствующим входам управляемого опорным генератором 10 основного делителя 11 частоты, выходы последнего непосредственно и через последовательно соединенные дополнительный делитель 12 частоты и коммутатор 13 подключены к соответствующим входам первого элемента 7 задержки.

Устройство приема дискретных сигналов работает следующим образом.

Последовательность квазитроичных или биимпульсных сигналов с выхода соединительной линии или выхода радиостанции поступает на вход 14 устройства. Через коммутатор 1 принятые сигналы поступают на усилитель 3 через детектор 2 (в случае передачи квазитроичного сигнала) или непосредственно на усилитель 3 (в случае передачи биимпульсного сигнала), а с выхода усилителя 3 - на входы преобразователей 4 и 5 квазитроичных и биимпульоных сигналов в двоичные, а также на вход блока 6 синхронизации. С выхода последнего на преобразователи 4 и 5 квазитроичных и биимнульсных сигналов в двоичные ноступают узкие импульсы тактовой частоты. На выходах преобразователей 4 и 5 квазитроичных и биимпульсных сигналов в двоичные получаются двоичные сигналы, поступающие

через коммутатор 1 на выход 15 устройства. Сигналы, поступающие на вход блока 6 синхронизации, в прямом инверсном виде подаются на вход первого элемента 7 задержки и далее на вход дешифратора 9, на другие входы которого через второй элемент 8 задержки поступают сигналы тактовой или удвоенной тактовой частоты с основного делителя II частоты.

При приеме квазитроичных силналов сигналы тактовой частоты подаются Непосредственно через коммутатор 13, а при приеме биимпульсных сигналов - через дополнительный делитель 12 частоты и коммутатор 13. Элементы задержки могут быть выполнены, например, в виде триггеров.

Формула изобретения

I. Устройство приема дискретных сигналов, содержащее нреобразователь квазитроичных сигналов в двоичные, унравляемый блоком синхронизации, отличающееся тем, что, с

целью повышения помехоустойчивости, введены детектор с усилителем, преобразователь биимпульсных сигналов в двоичные и коммутатор, при этом выходы коммутатора подключены соответственно ко входу и выходу детектора, а выход усилителя подключен ко входам нреобразователей квазитроичных и биимпульсных сигналов в двоичные и блока синхронизации, дополнительный выход которого подключен к управляющему входу нреобразователя биимпульсных сигналов в двоичные, кроме того, выходы преобразователей квазитроичных сигналов и биимпульсных сигналов в двоичные подключены к соответствующим входам коммутатора.

2. Устройство но п. 1, отличающееся тем, что блок синхронизации состоит из первого и второго элементов задержки, дешифратора, опорного генератора, основного и дополнительного делителей частоты и коммутатора,

при этом вход и выход первого элемента задержки и входы п выходы второго элемента задержки через дешифратор подключены к соответствующим входам управляемого опорным генератором основного делителя частоты, выходы которого непосредственно и через последовательно соединенные дополнительный делитель частоты и коммутатор подключены к соответствующим входам первого элемента задержки.

Источники информации, принятые во внимание при экспертизе:

1. Элементы теории передачи дискретной информации иод ред. Л. П. Пуртова, пзд. «Связь, М., 1971 г., стр. 8-10 (аналог).

2. Авторское свидетельство № 269975, М. Кл.2 Н 04L 3/02, 1970 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема биимпульсных сигналов | 1973 |

|

SU502506A1 |

| УСТРОЙСТВО для ПЕРЕДАЧИ —ПРИЕМА КВАЗИТРОИЧНЫХ | 1973 |

|

SU405181A1 |

| Устройство для приема биимпульсных сигналов | 1977 |

|

SU651485A2 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДАННЫХ | 2009 |

|

RU2406121C2 |

| Устройство для передачи сигналов | 1986 |

|

SU1385295A2 |

| СИСТЕМА ДУПЛЕКСНОЙ ВЫСОКОСКОРОСТНОЙ КОРОТКОВОЛНОВОЙ РАДИОСВЯЗИ | 2013 |

|

RU2553091C2 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

Авторы

Даты

1977-01-15—Публикация

1972-06-16—Подача