Фи1 f

Выпад

Изобретение относится к радиотехнике и может использоваться для передачи дискретных сигналов по каналам связи и является дополнительным к авт. св. № 924889,

Цель изобретения - повышение ско,- рости передачи.

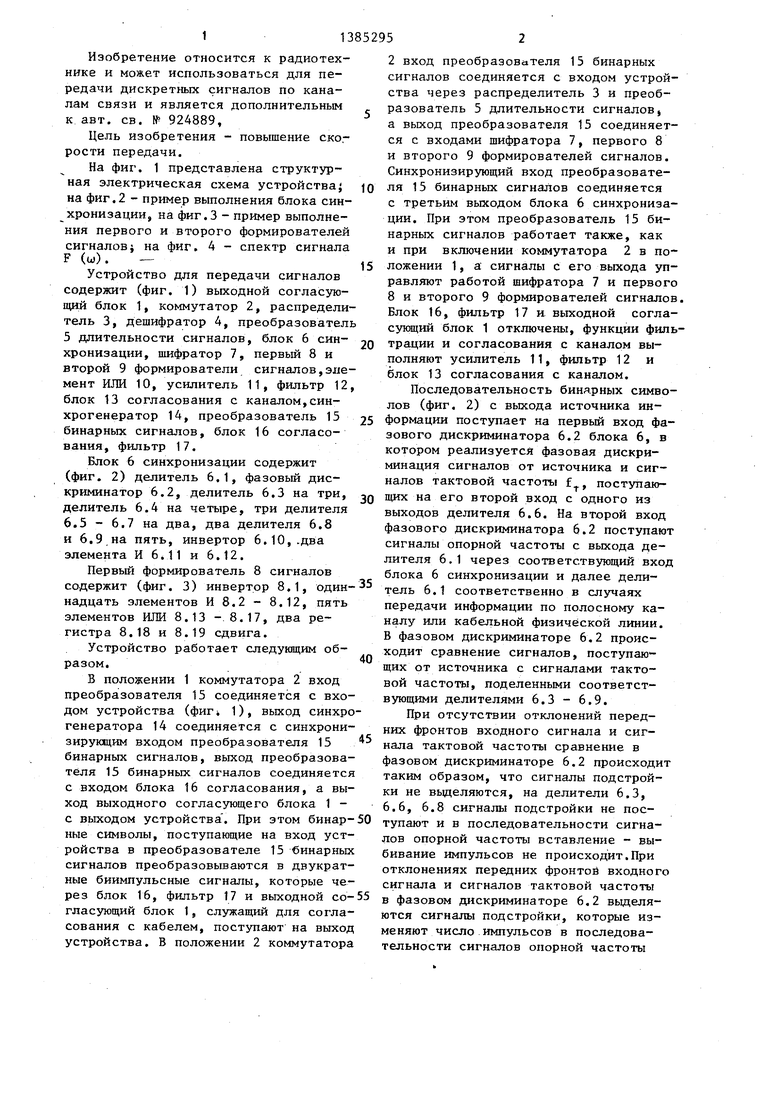

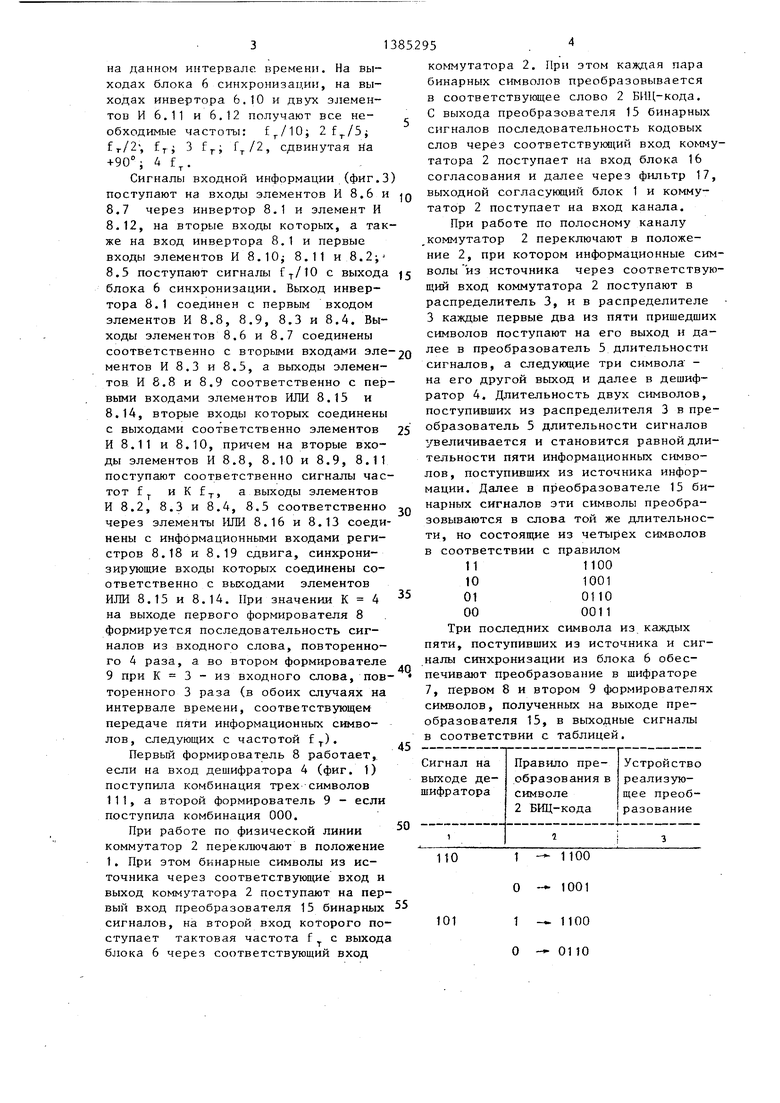

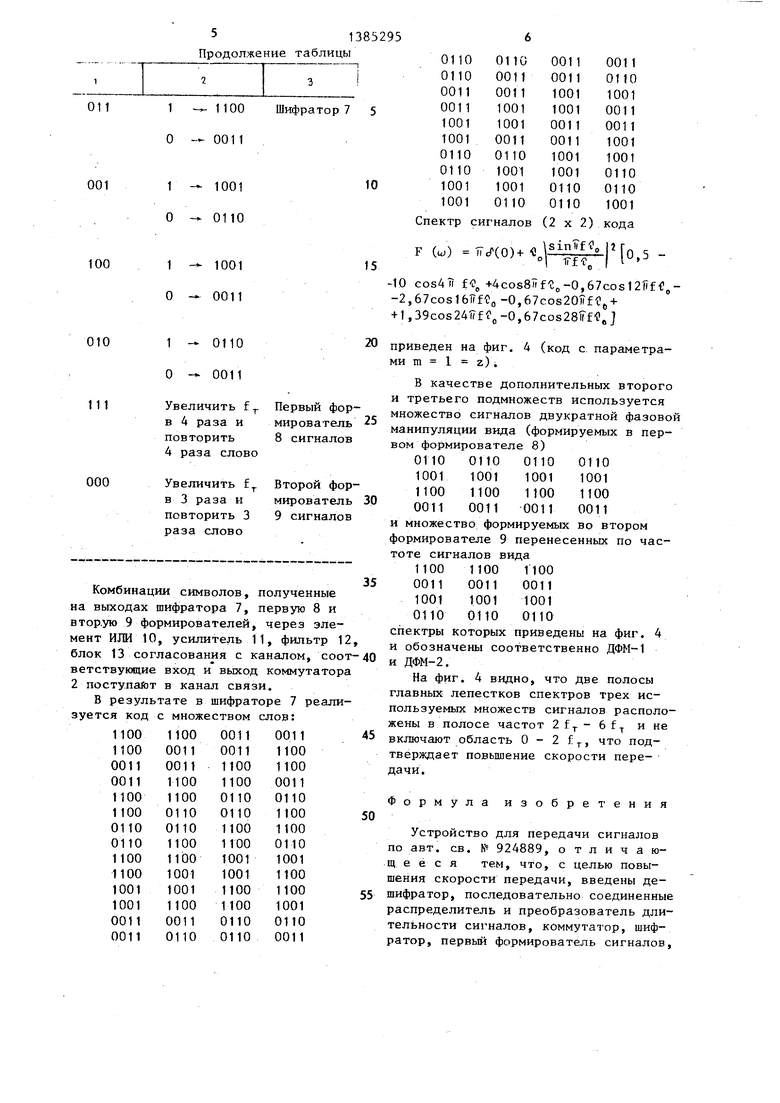

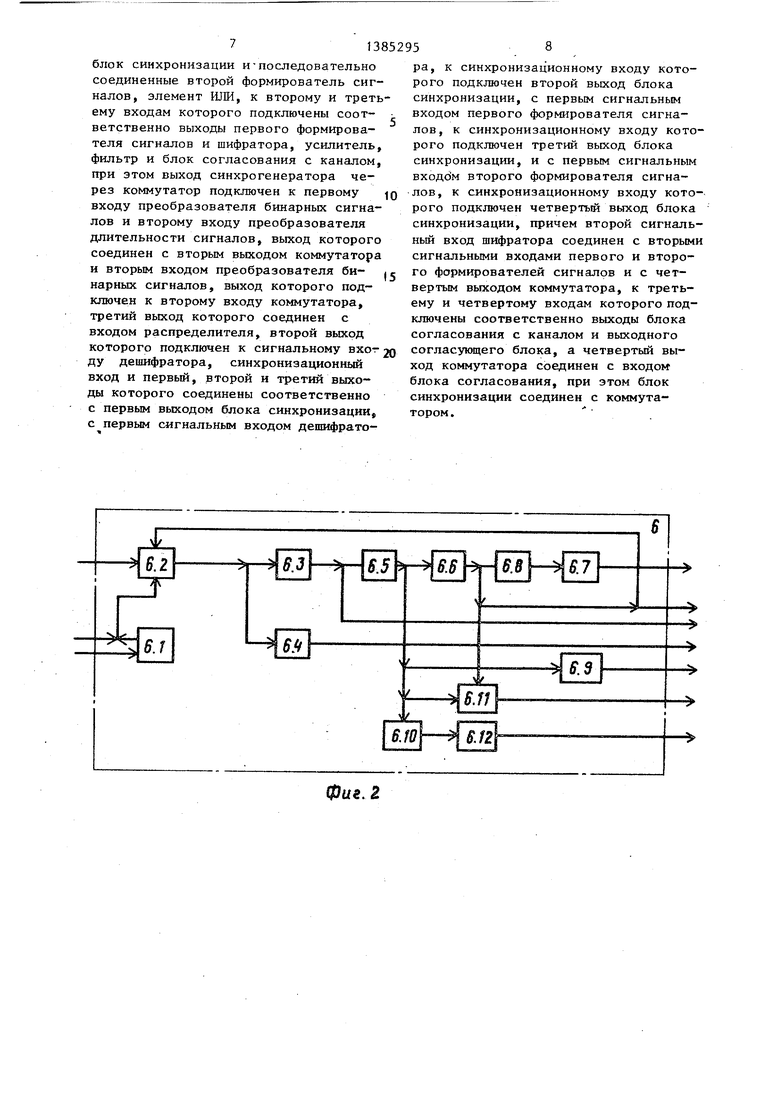

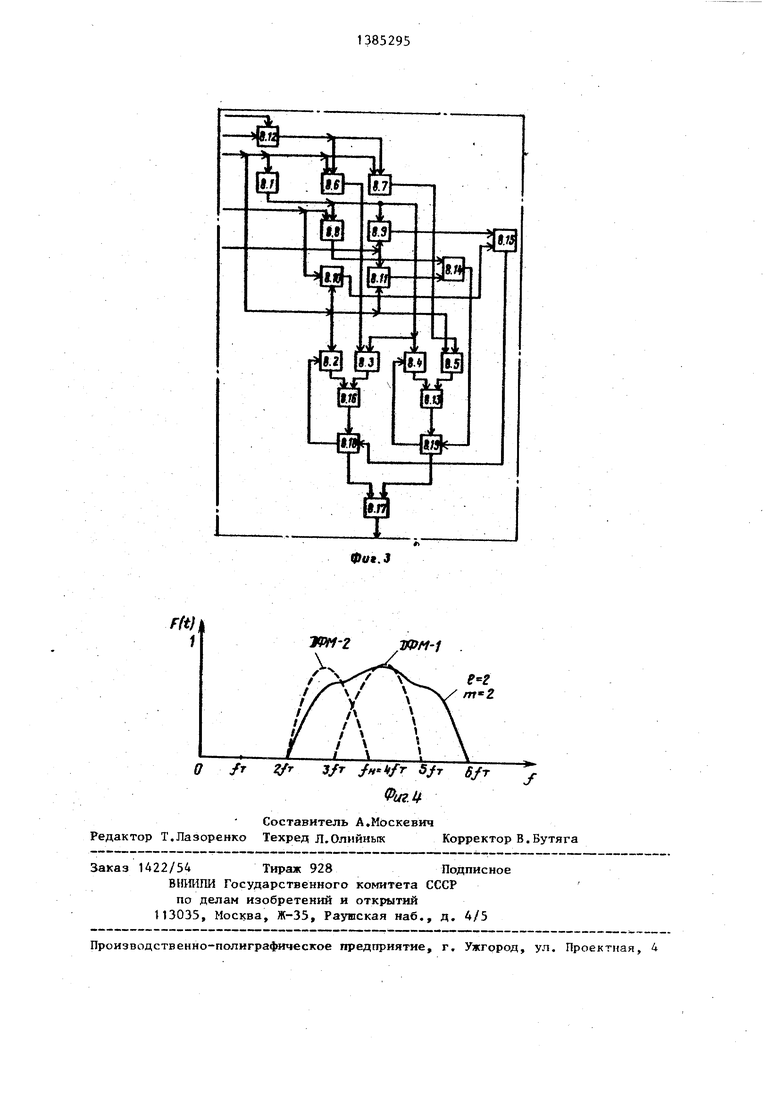

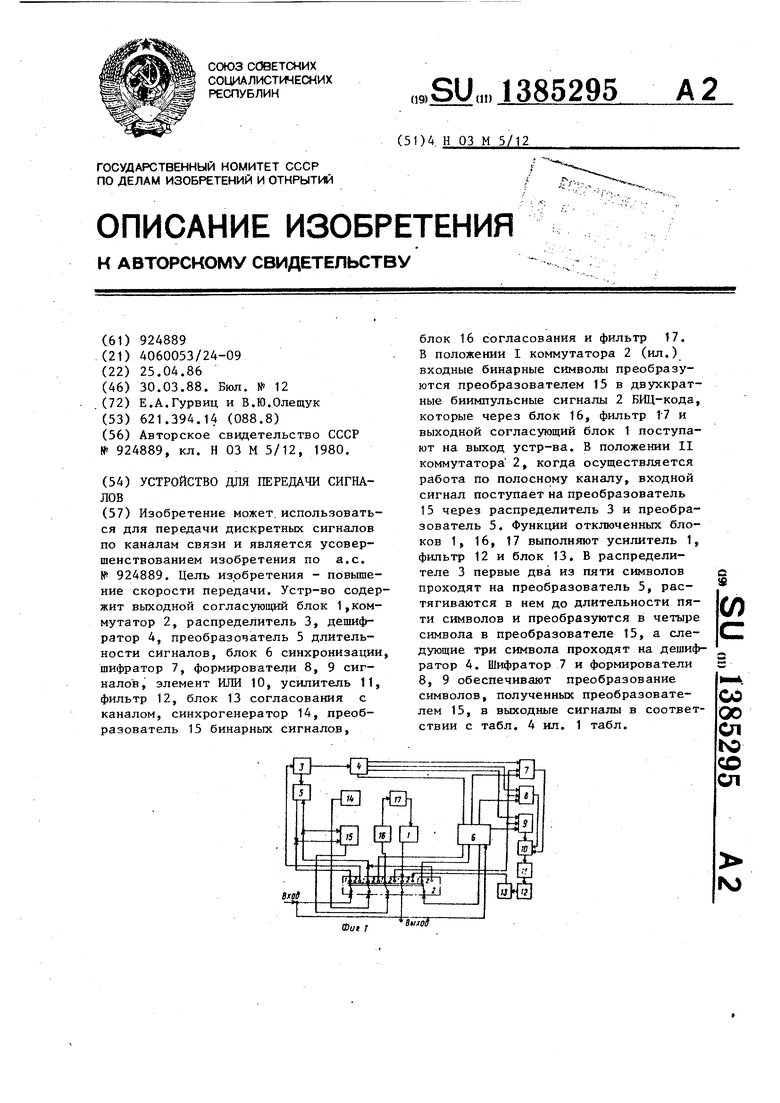

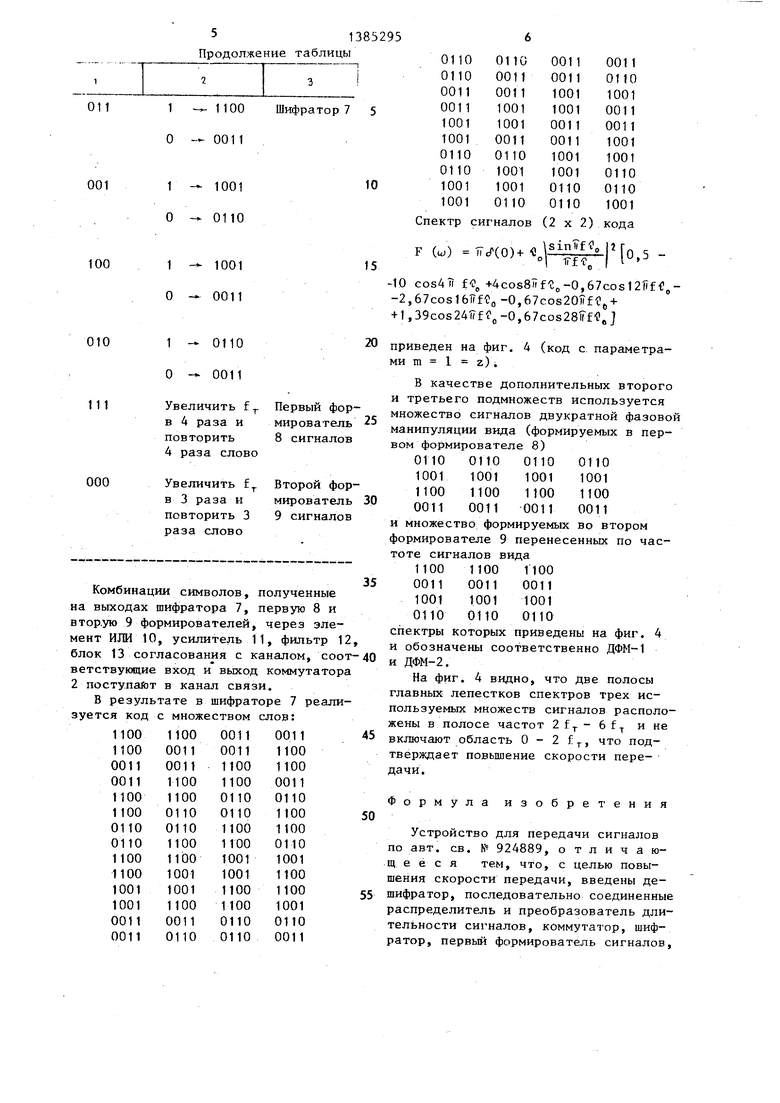

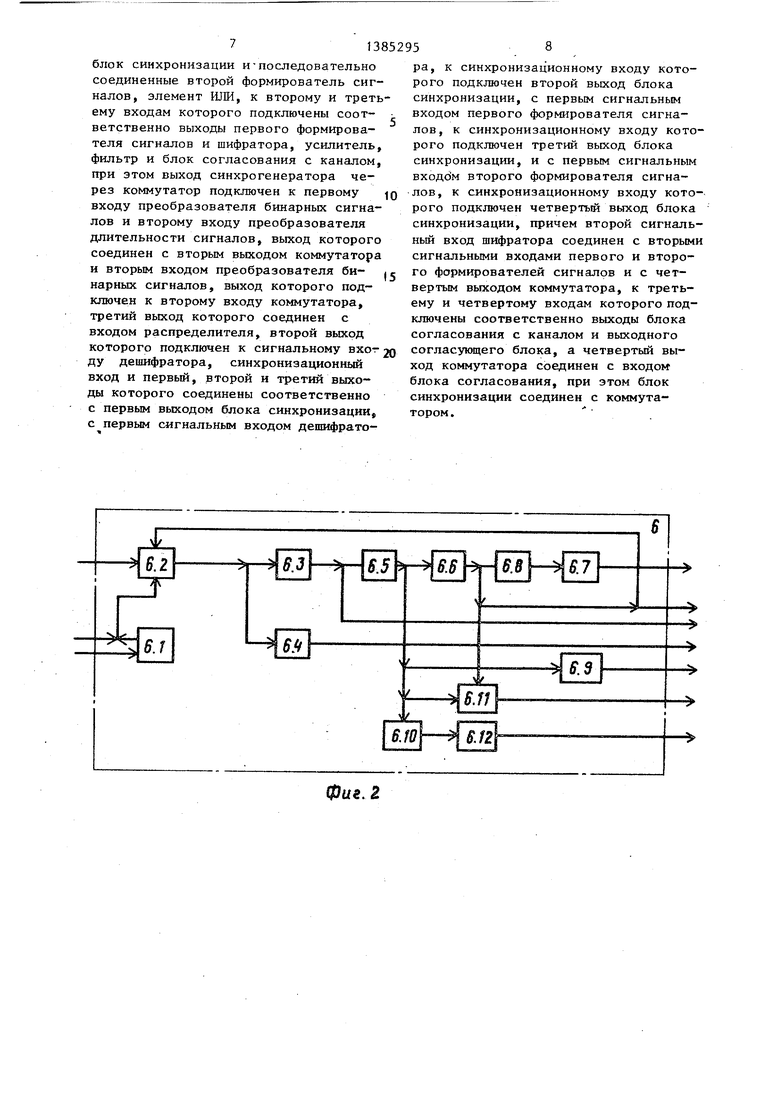

На фиг. 1 представлена структурная электрическая схема устройстваi на фиг.2 - пример выполнения блока син- хронизации, на фиг.З - пример выполнения первого и второго формирователей сигналов} на фиг. 4 - спектр сигнала F (w).

Устройство для передачи сигналов содержит (фиг. 1) выходной согласующий блок 1, коммутатор 2, распределитель 3, дешифратор 4, преобразователь 5 длительности сигналов, блок 6 син- хронизации, шифратор 7, первый 8 и второй 9 формирователи сигналов,элемент ИЛИ 10, усилитель 11, фильтр 12, блок 13 согласования с каналом,син- хрогенератор 14, преобразователь 13 бинарных сигналов, блок 16 согласования, фильтр 17.

Блок 6 синхронизации содержит (фиг. 2) делитель 6.1, фазовый дискриминатор 6.2, делитель 6.3 на три, делитель 6.4 на четыре, три делителя 6.5 - 6.7 на два, два делителя 6.8 и 6.9 на пять, инвертор 6.10,.два элемента Иб.11и6.12.

Первый формирователь 8 сигналов содержит (фиг. 3) инвертор 8.1, одиннадцать элементов И 8.2 - 8.12, пять элементов ИЛИ 8.13 -.8.17, два регистра 8.18 и 8.19 сдвига.

Устройство работает следующим образом.

В положении 1 коммутатора 2 вход преобразователя 15 соединяется с входом устройства (фиг4 1), выход синхро генератора 14 соединяется с синхронизирующим входом преобразователя 15 бинарных сигналов, выход преобразователя 15 бинарных сигналов соединяется с входом блока 16 согласования, а выход выходного согласующего блока 1 - с выходом устройства . При этом бинарные символы, поступающие на вход устройства в преобразователе 15 бинарных сигналов преобразовываются в двукратные биимпульсные сигналы, которые через блок 16, фильтр 17 и выходной согласующий блок 1, служащий для согласования с кабелем, поступают на выход устройства. В положении 2 коммутатора

5

Q

n 5

5

0 5

0

0

2 вход преобразователя 15 бинарных сигналов соединяется с входом устройства через распределитель 3 и преобразователь 5 длительности сигналов, а выход преобразователя 15 соединяется с входами шифратора 7, первого 8 и второго 9 формирователей сигналов. Синхронизирующий вход преобразователя 15 бинарных сигналов соединяется с третьим выходом блока 6 синхронизации. При этом преобразователь 15 бинарных сигналов работает также, как и при включении коммутатора 2 в положении 1, а сигналы с его выхода управляют работой шифратора 7 и первого 8 и второго 9 формирователей сигналов. Блок 16, фильтр 17 и выходной согласующий блок 1 отключены, функции фильтрации и согласования с каналом выполняют усилитель 11, фильтр 12 и блок 13 согласования с каналом.

Последовательность бинарных символов (фиг. 2) с выхода источника информации поступает на первый вход фазового дискриминатора 6.2 блока 6, в котором реализуется фазовая дискриминация сигналов от источника и сигналов тактовой частоты f поступающих на его второй вход с одного из выходов делителя 6.6. На второй вход фазового дискриминатора 6.2 поступают сигналы опорной частоты с выхода делителя 6.1 через соответствующий вход блока 6 синхронизации и далее делитель 6.1 соответственно в случаях передачи информации по полосному каналу или кабельной физической линии. В фазовом дискриминаторе 6,2 происходит сравнение сигналов, поступающих от источника с сигналами тактовой частоты, поделенными соответствующими делителями 6.3 - 6.9.

При отсутствии отклонений передних фронтов входного сигнала и сигнала тактовой частоты сравнение в фазовом дискриминаторе 6.2 происходит таким образом, что сигналы подстройки не выделяются, на делители 6.3, 6.6, 6.8 сигналы подстройки не поступают и в последовательности сигналов опорной частоты вставление - выбивание импульсов не происходит.При отклонениях передних фронтоё входного сигнала и сигналов тактовой частоты в фазовом дискриминаторе 6.2 вьщеля- ются сигналы подстройки, которые изменяют число импульсов в последовательности сигналов опорной частоты

на данном интервале времени. На выходах блока 6 синхронизации, на выходах инвертора 6.10 и двух элементов И 6.11 и 6.12 получают все необходимые частоты: fr/2 , f,-; 3 , сдвинутая на +90°; 4 f.

Сигналы входной информации (фиг.3 поступают на входы элементов И 8.6 и 8.7 через инвертор 8.1 и элемент И 8.12, на вторые входы которых, а также на вход инвертора 8.1 и первые входы элементов И 8.10 8.11 и8. 8.5 поступают сигналы с выхода блока 6 синхронизации. Выход инвертора 8.1 соединен с первым входом элементов И 8.8, 8.9, 8.3 и 8.4. Выходы элементов 8.6 и 8.7 соединены соответственно с вторыми входами эле ментов И 8.3 и 8.5, а выходы элементов И 8.8 и 8.9 соответственно с первыми входами элементов ИЛИ 8.15 и 8.14, вторые входы которых соединены с выходами соответственно элементов И 8.11 и 8.10, причем на вторые входы элементов И 8.8, 8.10 и 8.9, 8.11 поступают соответственно сигналы частот f и К fy, а выходы элементов И 8.2, 8.3 и 8.4, 8.5 соответственно через элементы ИЛИ 8.16 и 8.13 соединены с информационными входами регистров 8.18 и 8.19 сдвига, синхронизирующие входы которых соединены соответственно с вьЕходами элементов ИЛИ 8.15 и 8.14. При значении К 4 на выходе первого формирователя 8 формируется последовательность сигналов из входного слова, повторенного 4 раза, а во втором формирователе 9 при К 3 - из входного слова, пов торенного 3 раза (в обоих случаях на интервале времени, соответствующем передаче пяти информационных С1Шво- лов, следующих с частотой ff).

Первый формирователь 8 работает, если на вход дешифратора 4 (фиг. 1) поступила комбинация трех-символов 111, а второй формирователь 9 - если поступила комбинация 000.

При работе по физической линии коммутатор 2 переключают в положение 1. При этом бинарные символы из источника через соответствующие вход и выход коммутатора 2 поступают на первый вход преобразователя 15 бинарных сигналов, на второй вход которого поступает тактовая частота f с выхода блока 6 через соответствующий вход

1385295.

KONfMyTaTopa 2. При этом каждая пара

10

5

5 0

0

5

5

бинарных символов преобразовывается в соответствующее слово 2 БИЦ-кода. С выхода преобразователя 15 бинарных сигналов последовательность кодовых слов через соответствугаций вход коммутатора 2 поступает на вход блока 16 согласования и далее через фильтр 17, выходной согласуюций блок 1 и коммутатор 2 поступает на вход канала. При работе по полосному каналу коммутатор 2 переключают в положение 2, при котором информационные символы из источника через соответствующий вход коммутатора 2 поступают в распределитель 3, и в распределителе 3 каждые первые два из пяти пришедших символов поступают на его выход и далее в преобразователь 5 длительности сигналов, а следующие три символа - на его другой вьгход и далее в дешифратор 4. Длительность двух символов, поступивших из распределителя 3 в преобразователь 5 длительности сигналов увеличивается и становится равной длительности пяти информационных символов, поступивших из источника информации. Далее в преобразователе 15 бинарных сигналов эти символы преобразовываются в слова той же длительности, но состоящие из четырех символов в соответствии с правилом

1100 1001 0110 0011

Три последних символа из каждых пяти, поступивших из источника и сигналы синхронизации из блока 6 обеспечивают преобразование в шифраторе 7, первом 8 и втором 9 формирователях символов, полученных на выходе преобразователя 15, в выходные сигналы в соответствии с таблицей.

соответствии 11 10 01 00

5

50

101

1 О

- 1100 - 01 10

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1238268A2 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

| Устройство для кодирования чертежей печатных плат | 1979 |

|

SU858029A1 |

| Система связи с многоосновным кодированием | 1987 |

|

SU1443190A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для передачи сигналов | 1980 |

|

SU924889A1 |

| Устройство для передачи и приема телеграмм | 1988 |

|

SU1559419A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1996 |

|

RU2128890C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

Изобретение может, использоваться для передачи дискретных сигналов по каналам связи и является усовершенствованием изобретения по а.с. № 924889. Цель изобретения - повьппе- ние скорости передачи. Устр-во содержит выходной согласующий блок 1,коммутатор 2, распределитель 3, дешифратор 4, преобразователь 5 длительности сигналов, блок 6 синхронизации, шифратор 7, формирователи 8, 9 сигналов, элемент ИЛИ 10, усилитель 11, фильтр 12, блок 13 согласования с каналом, синхрогенератор 14, преобразователь 15 бинарных сигналов. блок 16 согласования и фильтр 17. В положении I коммутатора 2 (ил.) входные бинарные символы преобразуются преобразователем 15 в двухкратные биимпульсные сигналы 2 БИЦ-кода, которые через блок 16, фильтр t7 и выходной согласующий блок 1 поступают на выход устр-ва. В положении II коммутатора 2, когда осуществляется работа по полосному каналу, входной сигнал поступает на преобразователь 15 через распределитель 3 и преобразователь 5. Функции отключенных блоков 1, 16, 17 выполняют усилитель 1, фильтр 12 и блок 13. В распределителе 3 первые два из пяти символов проходят на преобразователь 5, растягиваются в нем до длительности пяти символов и преобразуются в четыре символа в преобразователе 15, а следующие три символа проходят на дешифратор 4. Шифратор 7 и формирователи 8, 9 обеспечивают преобразование символов, полученных преобразователем 15, в выходные сигналы в соответствии с табл. 4 нл. 1 табл. с Ф сл со оо СП Ю СО СП N)

1

О

1 О

1 о

1100 0011

1001 0110

1001 0011

Шифратор 7

010

1 - 0110 о - 0011

Увеличить f Первый форв 4 раза имирователь 25

повторить8 сигналов 4 раза слово

Увеличить f Второй форв 3 раза имирователь 30

повторить 39 сигналов раза слово

45

35

бинации символов, полученные

ходах шифратора 7, первую 8 и ю 9 формирователей, через элеИЛИ 10, усилитель 11, фильтр 12, 13 согласования с каналом, соот-40 вующие вход и выход коммутатора тупает в канал связи.

результате в шифраторе 7 реалия код с множеством слов:

1100 1100 0011 0011 1100 0011 0011 1100 ООП 0011 1100 1100

1100

0110

0110

1100

1100

1001

1001

1100

1 100

0110

0110

ООП 0110 1100 1100 0110 1001 1100 1100 1001 0110 0011

55

50

5

0

5

5

0

1001 1100 0011

1001 1100 0011

0110 1001 1100 0011

-10 cos4li )„+4cos8мf гo-0,67cos12|if }„- -2,67cos16T(f гo -0,67cos20iif«j + + 1,39cos24fffOj,-0,67cos28 f , j

приведен на фиг. 4 (код с. параметрами m 1 z) i

В качестве дополнительных второго и третьего подмножеств используется множество сигналов двукратной фазовой манипуляции вида (формируемых в первом формирователе 8) 0110 0110 0110 1001 1100 0011

и множество формируемых во втором формирователе 9 перенесенных по частоте сигналов вида 1100 1100 1100 0011 0011 1001 1001 0110 0110 спектры которых приведены на фиг. 4 и обозначены соответственно ДФМ-1 и ДФМ-2.

На фиг. 4 видно, что Две полосы главных лепестков спектров трех используемых множеств сигналов расположены в полосе частот 2 f - 6 f и не включают область О - 2 1: , что подтверждает повьшзение скорости передачи.

0011 1001 0110

Формула изобретения

Устройство для передачи сигналов по авт. св. № 924889, отличаю- щ е ее я тем, что, с целью повышения скорости передачи, введены дешифратор, последовательно соединенные распределитель и преобразователь длительности сигналов, коммутатор, шифратор, первьй формирователь сигналов.

7138

блок синхронизации и-последовательно соединенные второй формирователь сигналов, элемент ШШ, к второму и третьему входам которого подключены соот- ветственно выходы первого формирователя сигналов и шифратора, усилитель, фильтр и блок согласования с каналом, при этом выход синхрогенератора через коммутатор подключен к первому входу преобразователя бинарных сигналов и второму входу преобразователя длительности сигналов, выход которого соединен с вторым выходом коммутатора и вторым входом преобразователя би- нарных сигналов, выход которого подключен к второму входу коммутатора, третий выход которого соединен с входом распределителя, второй выход которого подключен к сигнальному вхот ду дешифратора, синхронизационный вход и первый, второй и третий выходы которого соединены соответственно с первым выходом блока синхронизации, с первым сигнальным входом дешифрато

Фиг. 2

8

ра, к синхронизационному входу которого подключен второй выход блока синхронизации, с первым сигнальным входом первого формирователя сигналов, к синхронизационному входу которого подключен третий выход блока синхронизации, и с первым сигнальным входом второго формирователя сигналов, к синхронизационному входу которого подключен четвертый выход блока синхронизации, причем второй сигнальный вход шифратора соединен с вторым сигнальными входами первого и второго формирователей сигналов и с четвертым выходом коммутатора, к третьему и четвертому входам которого подключены соответственно выходы блока согласования с каналом и выходного согласующего блока, а четвертый выход коммутатора соединен с входом блока согласования, при этом блок синхронизации соединен с коммутатором.

liirrLM

б. 5

| Устройство для передачи сигналов | 1980 |

|

SU924889A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-30—Публикация

1986-04-25—Подача