1

Изобретение относится к системам связи и может использоваться в устройствах управления перастройкой частоты приемных и передающих устройств, в комплексах наклонного зондирования ионосферы и выбора оптимальных частот связи.

Известно устройство управления перестройкой частоты системы связи, содержащее последовательно соединенные коммутатор, декадный счетчик и схему сравнения, а так- же регистр, включе шый между коммутаторо и другим входом схемы сравнения, и шифратор l.

Однако в известном устройстве при приеме сигналов от нескольких передающих центров возможны ошибки в перестройке частоты.

Цель изобретения - повышение точности перестройки при приеме сигналов нескольк ос передающих центров.

Для этого в предложенное устройство введены зaпo шнaющий блок, наборный блок, два распределителя, одновибратор, элементы И и ИЛИ, при этом наборный блок через шифратор и запоминающий блок подключен к

коммутатору; выход шифратора подключен к друго 1у входу коммутатора, к стробирующим входам которого подключены выходы обоих распределителей, выход первого распределите-чя подключен к первому адресному входу зэ.по я1нающего блока, первый вход первого распределитечя подключен к наборному блоку, другой выход которого подключен к первому входу переключателя, первый выход Которого подключен к входу второго распределителя, а второй вход первого распределителя подключен к второму выходу переключателя, причем другие адресные входы запоминающего блока соединены с выходами элементов И, первые входы которых подключены к выходу элемента ИЛИ, один вход которого подключен к третьему выходу наборного блока, на другой вход элемента ИЛИ через одновибратор и на третий вход первого распределителя непосредственно поданы импульсы начала щжла, а на второй вход .переключателя поданы -импульсы тактовой частоты.

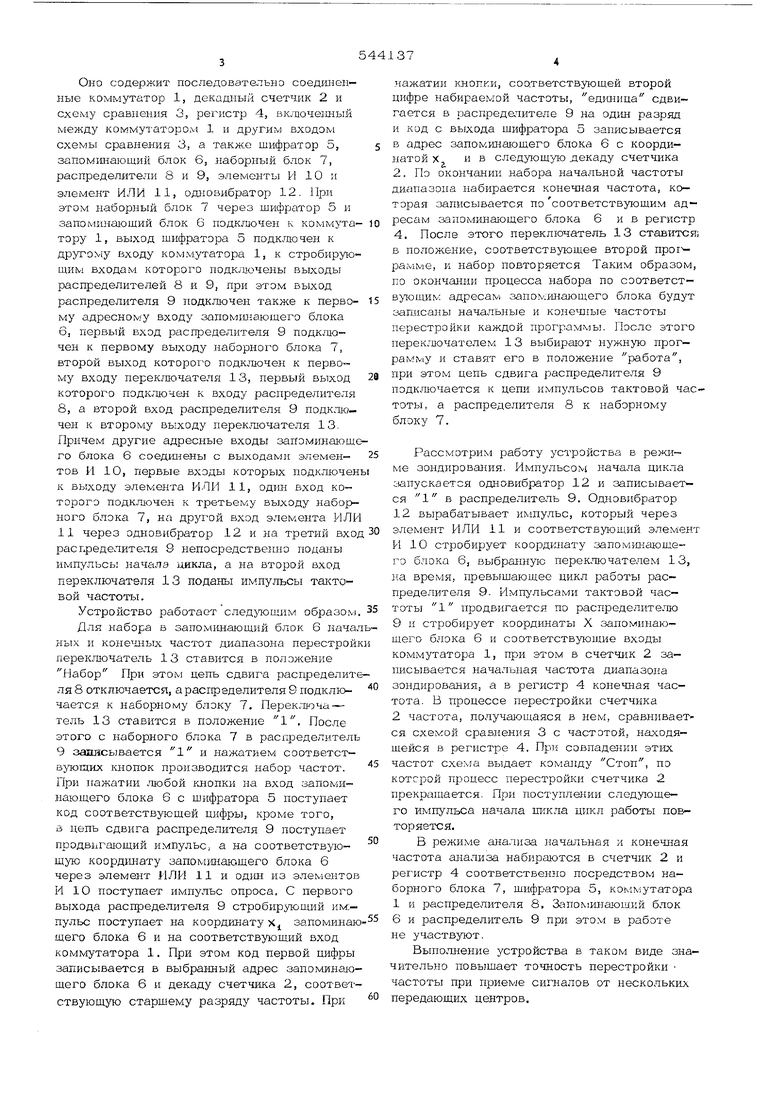

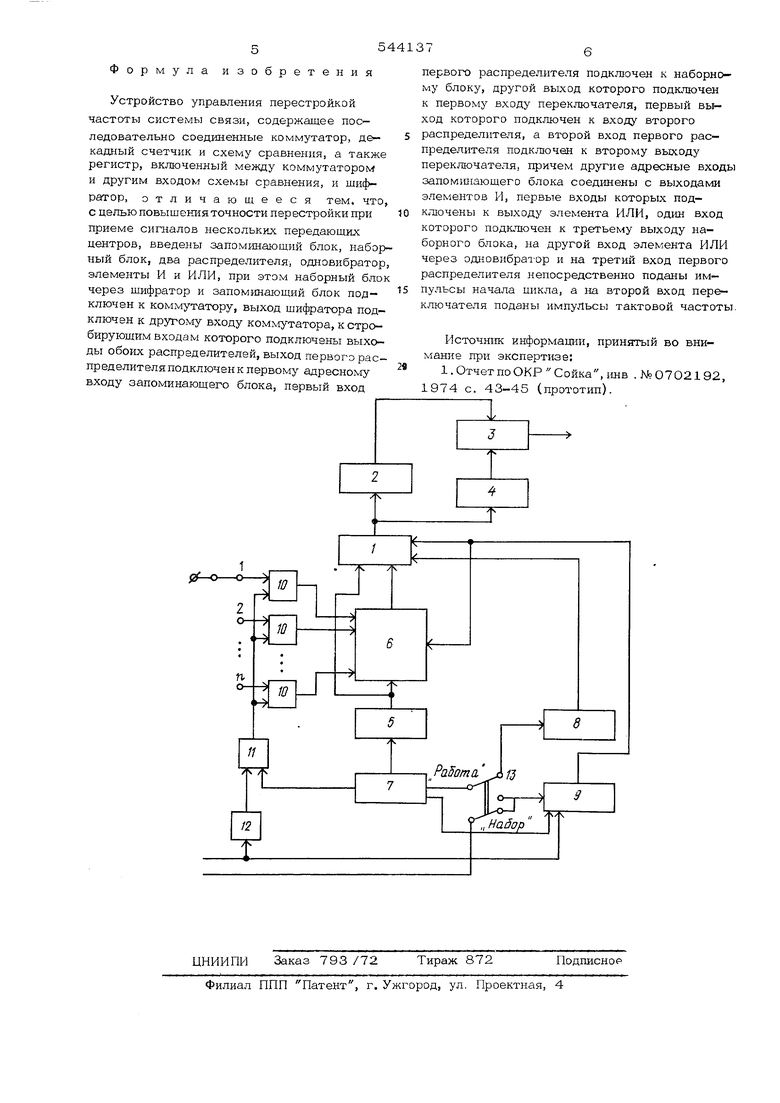

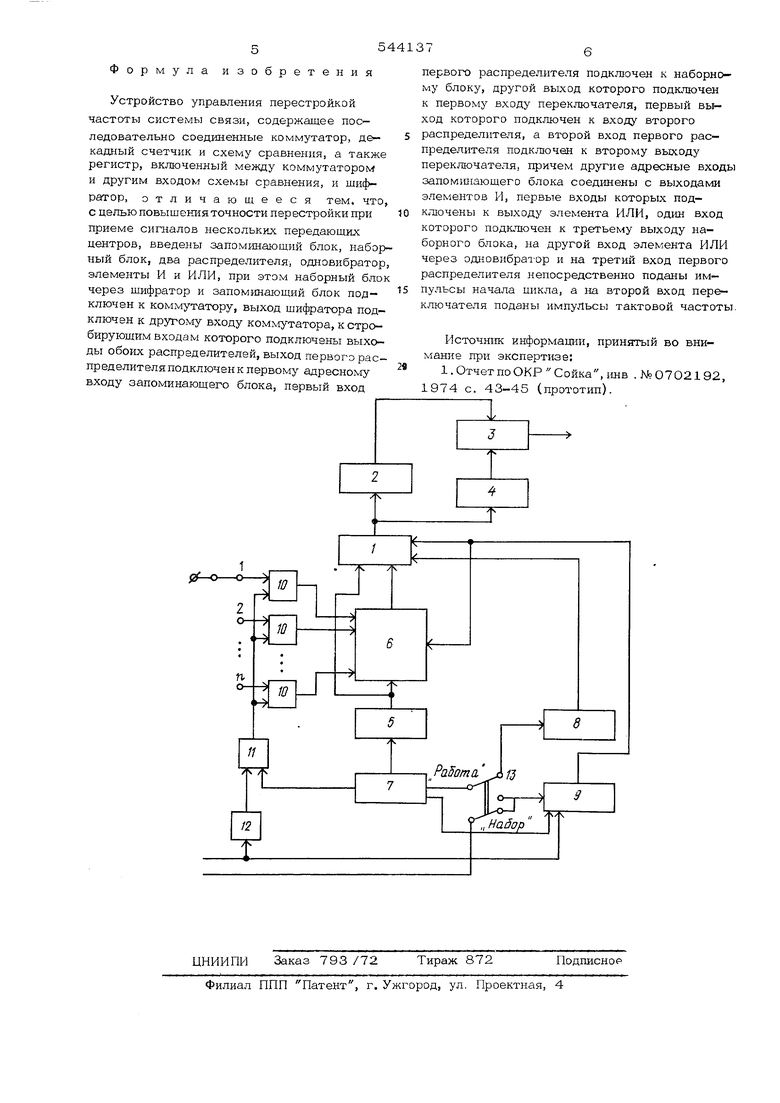

На чертеже изображена структурнв.я электрическая схема предложенного устройства. Оно содержит последовательно соед1шен- ные коммутатор 1, декадный счетчик 2 и схему сравнення 3, регистр 4, вк.почехшый между коммутатором 1 и другим входом схемы сравнения 3, а также шифратор 5, запомршающий блок 6, наборный блок 7, распределители 8 и 9, элементы И 10 и элемент ИЛИ 11, одновибратор 12. При этом наборный блок 7 через шифратор 5 и запоминающий блок 6 подключен к коммута тору 1, выход шифратора 5 нодк.шочен к другому входу коммутатора 1, к стробирующим входам которого подклдочены выходы распределителей 8 и 9, при этом выход распределителя 9 подключен также к первому адресному входу запокишающего блока 6, первый вход распределителя 9 подключен к первому выходу наборного блока 7, второй выход которого подключен к первому входу переключателя 13, первый выход которого подключен к входу распределителя 8, а второй вход распределителя 9 подключен к второму выходу переключателя 13. Причем другие адресные входы запоминающ го блока 6 соедш1ены с выходами элемен тов И 10, первые входы которых подключен к выходу элемента ИЛИ 11, один вход которого подключен к третьему выходу наборного блока 7, на другой вход элемента ИЛИ 11 через одновибратор 12 и на третий вхо распределителя 9 непосредстве11.но поданы импульсы начала цикла, а на второй вход переключателя 13 поданы импульсы тактовой частоты. Устройство работает след тошим образом Для набора в запомщ1ающий блок 6 нача ных и конечных частот диапазона перестрой переключатель 13 ставится в положение Набор При этом цепь сдвига распределит ля 8 отключается, а распределителя 9 подключается к наборному блоку 7. Переключатель 13 ставится в положение 1. После этого с наборного блока 7 в распределитель 9 занисывается 1 и нажатием соответствующих кнопок производится набор частот. При нажатии любой клопки на вход запоминающего блока 6 с шифратора 5 поступает код соответствующей пнфры, кроме того, S, цепь сдвига распределителя 9 поступает продвигающий импульс, а на соответствуете- щую коорд шату запомш1ающего блока 6 через элемент ИЛИ 11 и один из элементов И 10 поступает импульс опроса, С первого выхода распределителя 9 стробирующий им:- пульс поступает на координату х запоминаю щего блока 6 и на соответствующий вход коммутатора 1. При этом код первой цифры записывается в выбранный адрес запомина ю щего блока 6 и декаду счетчика 2, соответ ствующую старшему разряду частоты. При .нажатии кнопки, соответствующей второй цифре набираемой частоты, едшпща сдвигается в распред&лителе 9 на один разряд и код с выхода шифратора 5 записывается в адрес запоминающего блока 6 с координатой X ив следующую декаду счетчика 2. По окончании набора начальной частоты диапазона набирается конечная частота, которая записывается по соответствующим адресам запоминающего блока 6 ив регистр 4, После этого переключатель 13 ставится; в положение, соответствующее второй прог рамме, и набор повторяется Таким образом, по окончании процесса набора по соответствующим адресам запомШ ающего блока будут записаны начальные и конечные частоты перестройки каждой программы. После этого переключателем 13 выбирают нужную программу и ставят его в положение работа, при этом цепь сдвига распределителя 9 подключается к цепи импульсов тактовой частоты, а распределителя 8 к наборному блоку 7. Рассмотрим работу устройства в режиме зондирования. Импульсом начала цикла запускается одновибратор 12 и записывается 1 в распределитель 9. Одновибратор 12 вырабатывает импульс, который через элемент ИЛИ 11 и соответствующий элемент И 10 стробирует координату запомш-1ающего блока 6, выбранную переключателем 13, на время, нревыщающее цикл работы распределите.ля 9. Имп льсами тактовой частоты 1 продвигается по распределителю 9 и стробирует координаты X запоминающего блока 6 и соответствующие входы коммутатора 1, при этом в счетчик 2 записывается начальная частота диапазона зондирования, а в регистр 4 конечная частота. В процессе перестройки счетчика 2 частота, получающаяся в нем, сравнивается схемой сравнения 3 с частотой, находящейся в регистре 4. При совпадении этих частот схема выдает команду Стоп, по котсрой процесс перестройки счетчика 2 прекращается. При поступлении следующего импульса начала шжла цикл работы повторяется. В режиме анализа начальная и конечная частота анализа набираются в счетчик 2 и регистр 4 соответственно посредством наборного блока 7, шифратора 5, коммутатора 1 и распределителя 8, Запомишюший блок 6 и распределитель 9 при этом в работе не участвуют. Выполнение устройства в таком виде значительно повышает точность перестройки частоты при приеме сигналов от нескольких передающих центров.

Формула изобретения

Устройство угфавления перестройкой частоты системы связи, содержащее последовательно соединенные коммутатор, декадный счетчик и схему сравнения, а также регистр, включенный между коммутатором и другим входом схемы сравнения, и шифратор, отличающееся тем. что, С целью повыщенияточности перестройки при

приеме сигналов нескольких передающих центров, введены запоминающий блок, наборный блок, два распределителя, одновибратор, элементы И и ИЛИ, при этом наборный блок через шифратор и запоминающий блок подключен к коммутатору, выход шифратора подключен к другому входу коммутатора, к стробирующим входам которого подключены выходы обоих распределителей, выход первого распределителя подключен к первому адресному входу запоминающего блока, первый вход

0-Q-О-5

первого распределителя подключен к наборному блоку, другой выход которого подключен к первому входу переключателя, первый выход которого подключен к входу второго распределителя, а второй вход первого распределителя подк,пючен к второму выходу переключателя, причем другие адресные входы запоминающего блока соединены с выходами элементов И, первые входы которых подключены к выходу элемента ИЛИ, один вход которого подключен к третьему выходу наборного блока, на другой вход элемента ИЛИ через одновибра1-ор и на третий вход первого распределителя непосредственно поданы импульсы начала цикла, а на второй вход переключателя поданы импульсы тактовой частоты.

Источник информации, принятый во внимание при экспертизе;

1. Отчет по ОКР Сойка, шв . № О7021 92, 1974 с. 43-45 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1980 |

|

SU947886A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Электронные часы | 1988 |

|

SU1569801A1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Цифровые вторичные часы | 1988 |

|

SU1511733A1 |

| Устройство для формирования пачекиМпульСОВ | 1979 |

|

SU828384A1 |

| Программное задающее устройство | 1975 |

|

SU542173A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| УСТРОЙСТВО ДЛЯ ПОВЕРКИ ИЗМЕРИТЕЛЕЙ ЧАСТОТЫ И ПЕРИОДА | 2009 |

|

RU2392633C1 |

Авторы

Даты

1977-01-25—Публикация

1975-02-19—Подача