1

Изобретение относится к области вычислительной и измерительной техники и может быть использовано в автоматических системах контроля, анализаторах спектров и т.д.

Известный преобразователь изменяющаяся частота-код содержит устройство управления, устройство сравнения кодов, схему ИЛИ, регистр-счетчик, генератор импульсов и два канала каждый из которых содержит ключ, цифровой частотомер, управляемый делитель с коммутируемы м выходом и двоичный счетчик 1 . Однако в преобразователе период первичного квантования по времени равен времени измерения. В связи с этим в состав преобразователя входят два совершенно идентичных канала, включающие наиболее сложные устройства (двоичный счетчик, управляемый делитель, цифровой частотомер). Эта особенность является недостатком данного преобразователя.

Цель изобретедак - повышение надежности.

Это достиг0етс т тем, что преобразовател изменяющаяся частота-код, содержащий один канал, состоящий из ключа, частотоме-

ра, счетчика, управляемого делителя частоты, а также генератора опорной частоты, регистра счетчика, блока сравнения и блока управления, причем выход ключа соединен со счетчиком и частотомером, выход которого соединен с управляемым делителем частоты, ко второму входу последнего подключен генератор опорной частоты, а выход управляемого делителя частоты соединен с регистром-счетчиком, второй вход регистрасчетчика подключен к счетчику, второй выход которого соединен с блоком сравнения, выход последнего соединен со вторым входом частотомера, а первый выход блока управления подключен к входу ключа, второй его выход - к выходам счетчика, регистра счетчика, управляемому делителю частоты, а также частотомеру, снабжен регистром памяти, входы которого соединены с выходами счетчика, а выходы - со входами блока сравнения, причем блок управления соединен с регистром памяти.

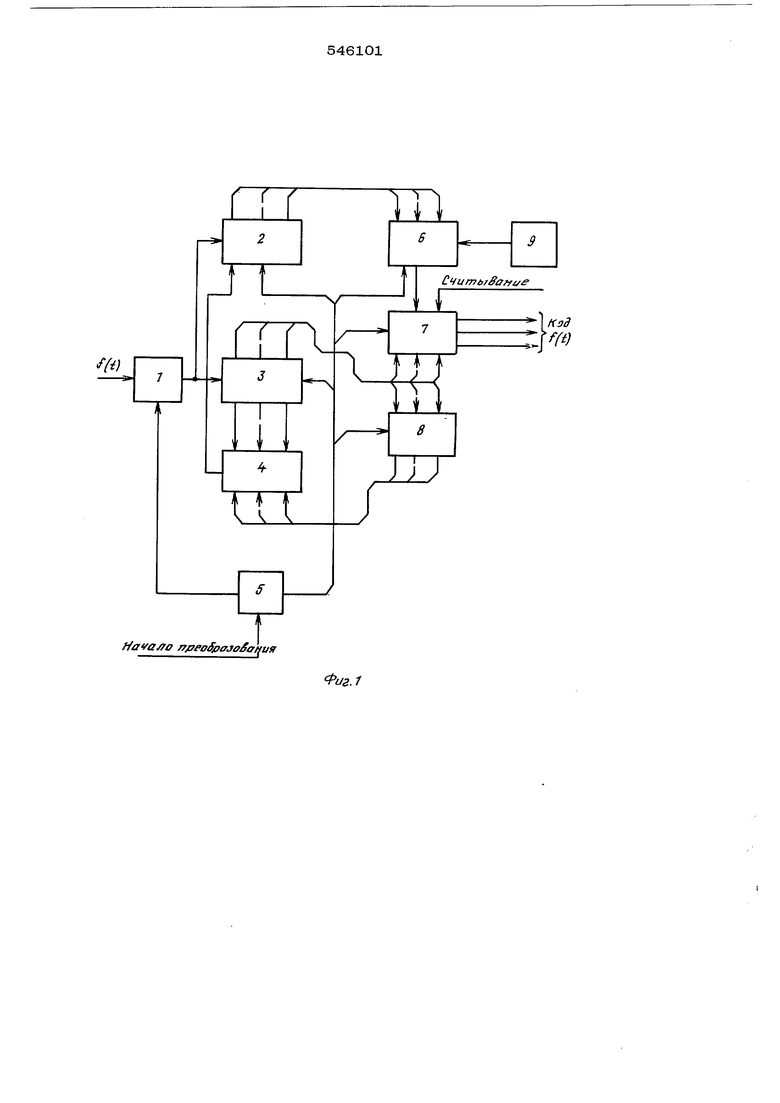

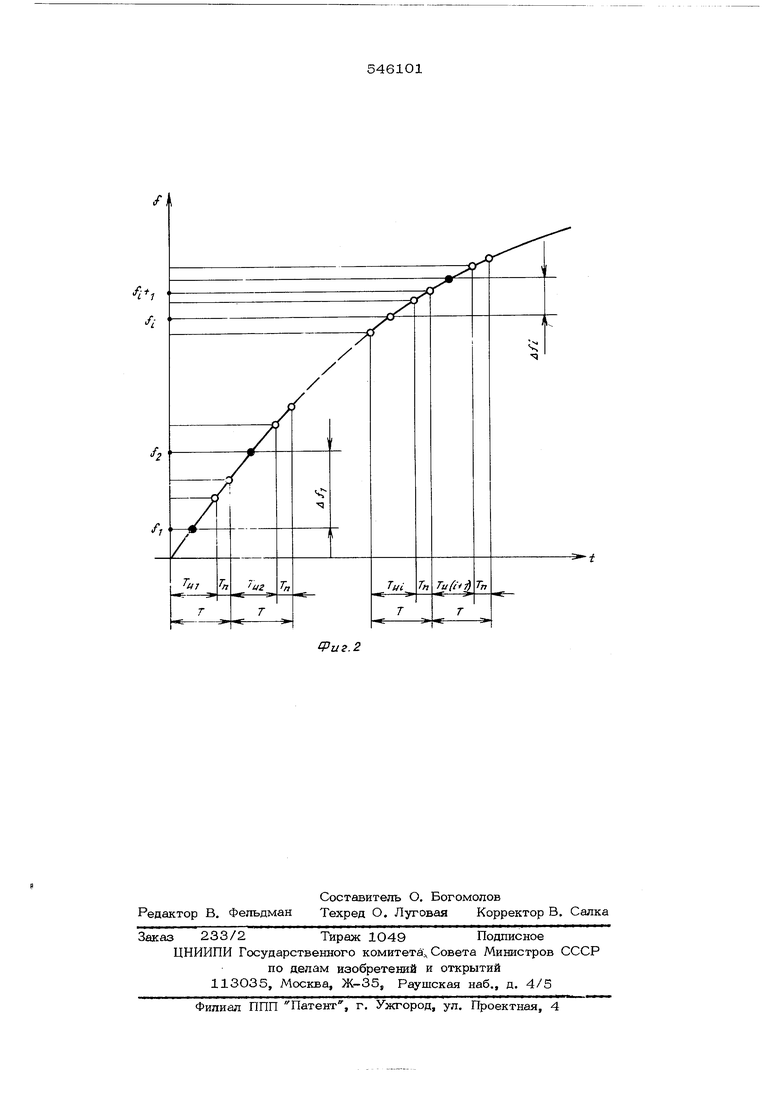

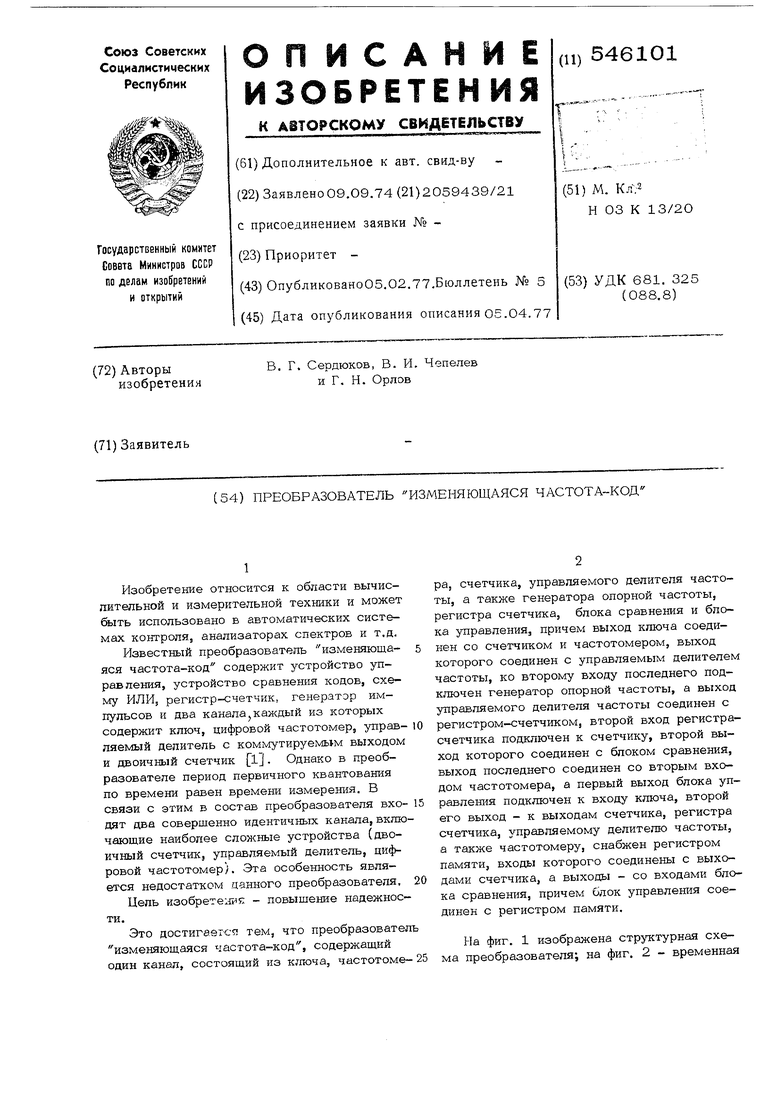

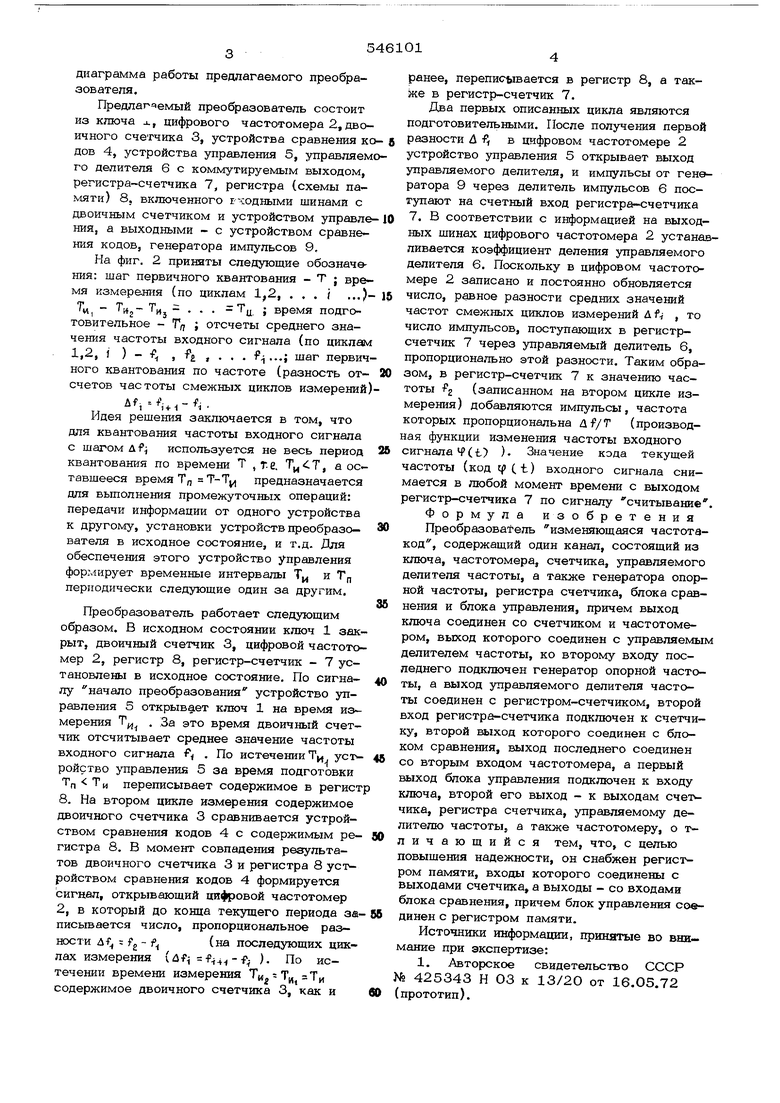

На фиг. 1 изображена стр тстурная схема преобразователя; на фиг. 2 - временная диаграмма работы предлагаемого преобразователя. Предлаг емый преобразователь состоит из ключа А, цифрового частотомера 2, двоичного счетчика 3, устройства сравнения ко дов 4, устройства управления 5, управляем го делителя б с комг гутируемым выходом, регистра-счетчика 7, регистра {схемы памяти) 8, включенного гчодными шинами с двоичным счетчиком и устройством управле ния, а выходными - с устройством сравнения кодов, генератора импульсов 9, На фиг. 2 приняты следующие обозначения: шаг первичного квантования - Т ; время измерантта (по циклам 1,2, . , . i ...)Т„, - Tt,- Tnj - . . . TU ; время подготовительное - Т/7 ; отсчеты среднего значения частоты входного сигнала (по циклам 1.2, J ) - f, f;...; шаг первич ного квантования по частоте (разность отсчетов частоты смежных циклов измерений Af. f. f , Идея решения заключается в том, что для квантования частоты входного сигнала с шагом ufi используется не весь период квантования по времени Т , г е. Тц . Т, а оставшееся время Тп T-Tj предназначается для выполнения промежуточных операций: передачи информации от одного устройства к другому, установки устройств преобразователя в исходное состояние, и т.д. Для обеспечения этого устройство управления формирует временные интервалы Tj и Т периодически следующие один за другим, Преобразователь работает следующим образом. В исходном состоянии ключ 1 закрыт, двоичный счетчик 3, цифровой частотомер 2, регистр 8, регистр-счетчик - 7 установлены в исходное состояние. По сигналу начало преобразования устройство управления 5 открыв§.ет ключ 1 на время из мерения Т . За это время двоичный счетчик отсчитывает среднее значение частоты входного сигнала f , По истечении Т устройство управлений 5 за время подготовки Тп Ти переписывает содержимое в регист 8. На втором цикле измерения содержимое двоичного счетчика 3 сравнивается устройством сравнения кодов 4 с содержимым регистра 8, В момент совпадения результатов двоичного счетчика 3 и регистра 8 уст ройством сравнения кодов 4 формируется сигнал, открывающий цифровой частотомер 2, в который до конца текущего периода записьгаается число, пропорциональное разности 4 fg - f((на последующих циклах измерения (ilfi - истечении времени измерения содержимое двоичного счетчика 3, как и

Источники информации, принзиые во вни,мание при экспертизе:

1. Авторское свидетельство СССР NO 425343 Н 03 к 13/20 от 16.05.72 (прототип). ранее, переписывается в регистр 8, а также в регистр-счетчик 7. Два первых описанных цикла являются подготовительными. После получения первой разности & f, в цифровом частотомере 2 устройство управления 5 открывает выход управляемого делителя, и импульсы от генэратора 9 через делитель импульсов 6 посгупают на счетный вход регистра-счетчика соответствии с информацией на выходных шинах цифрового частотомера 2 устанавливается коэффициент деления управляемого делителя 6. Поскольку в цифровом частотомере 2 записано и постоянно обновляется число, равное разности средних значений частот смежных циклов измерений Afv , то число импульсов, поступающих в регистрсчетчик 7 через управляемый делитель 6, пропорционально этой разности. Таким образом, в регистр-счетчик 7 к значению частоты f (записанном на втором цикле измерения) добавляются импульсы, частота которых пропорциональна Af/T (производая функции изменения частоты входного сигнала 9 (t) ), Значение кода текущей частоты (код tpCt) входного сигнала снимается в любой момент времени с выходом регистр-счетчика 7 по сигналу считывание. Формула изобретения Пpeoбpaзoвateль изменяющаяся частотакод, содержащий один канал, состоящий из ключа, частотомера, счетчика, управляемого делителя частоты, а также генератора опорной частоты, регистра счетчика, блока сравнения и блока управления, причем выход ключа соединен со счетчиком и частотомером, выход которого соединен с управляемым делителем частоты, ко второму входу последнего подключен генератор опорной частоты, а выход управляемого делителя частоты соединен с регистром-счетчиком, второй вход регистра-счетчика подкгаочен к счетчику, второй выход которого соединен с блоком сравнения, выход последнего соединен со вторым входом частотомера, а первый гкоц блока управления подключен к входу ключа, второй его выход - к выходам счет чика, регистра счетчика, управляемому делителю частоты, а также частотомеру, о т„ичающийся тем, что, с целью повышения надежности, он снабжен регистром памяти, входы которого соединены с выходами счетчика, а выходы - со входами блока сравнения, причем блок управления соединен с регистром памяти.

ггг

гп

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА-КОД | 1972 |

|

SU425343A1 |

| Цифровой низкочастотный частотомер | 1981 |

|

SU966619A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2002 |

|

RU2231077C2 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| ЦИФРОВОЙ ПРОЦЕНТНЫЙ ЧАСТОТОМЕР | 1971 |

|

SU300838A1 |

| Цифровой частотомер | 1978 |

|

SU771561A1 |

| Цифровой измеритель отношения низких частот | 1980 |

|

SU941907A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для измерения частоты сердечных сокращений | 1990 |

|

SU1759401A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

ffavg/fo f7jpeofffffjo o/fug

/i

Vus.2

Авторы

Даты

1977-02-05—Публикация

1974-09-09—Подача