САЭ 00

сд

со

Изобретение относится к радиотехнике и может быть использовано в различных устройствах автоматики и измерительной техники при.разработке фазометров, частотомеров, фазовра.- щателей.

Цель изобретения - повышение точности умножения при расширении диапазона умножаемых частот.

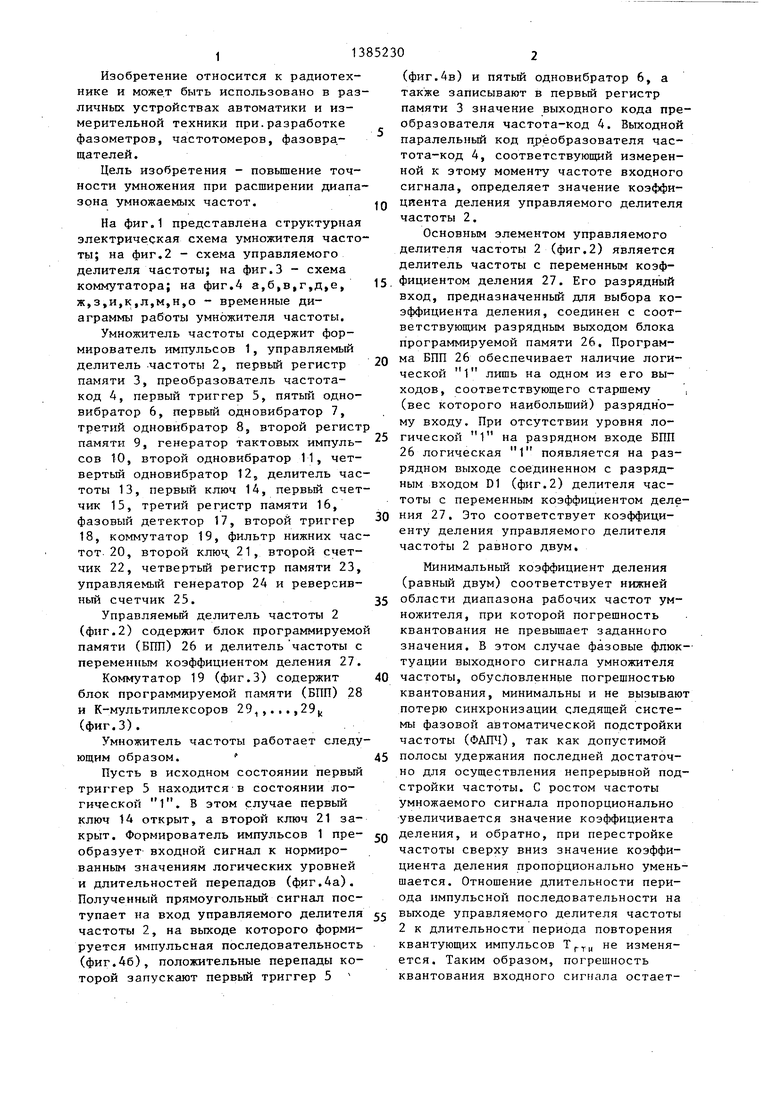

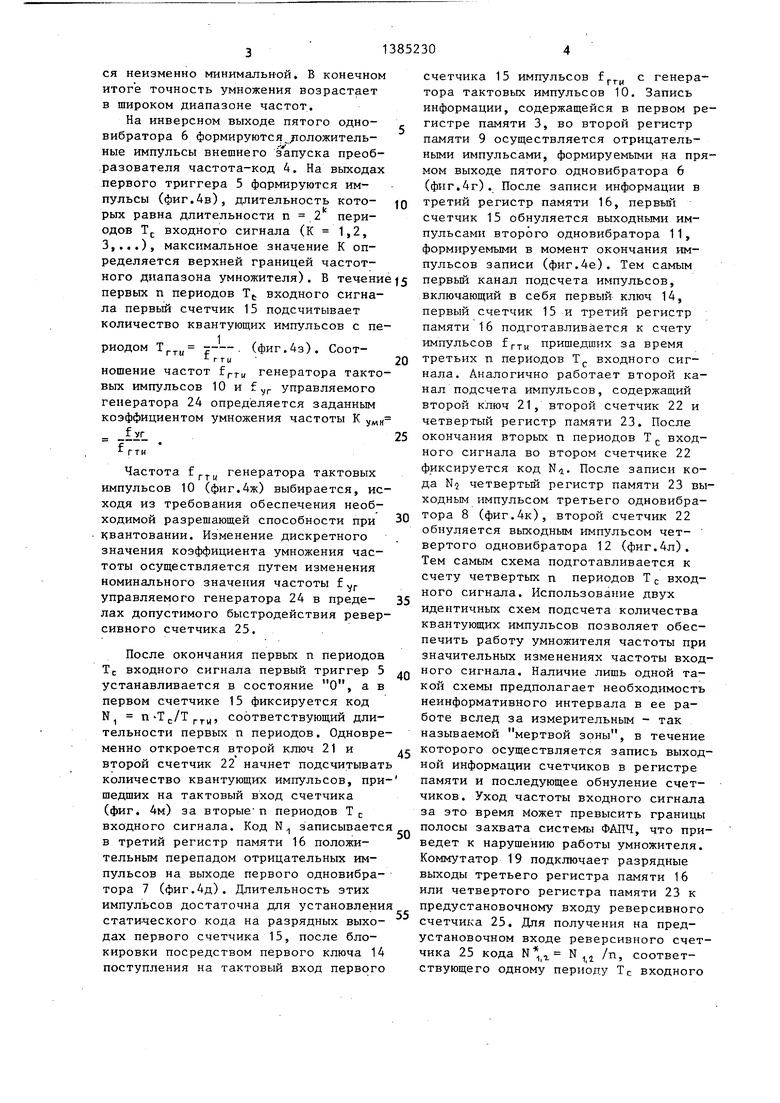

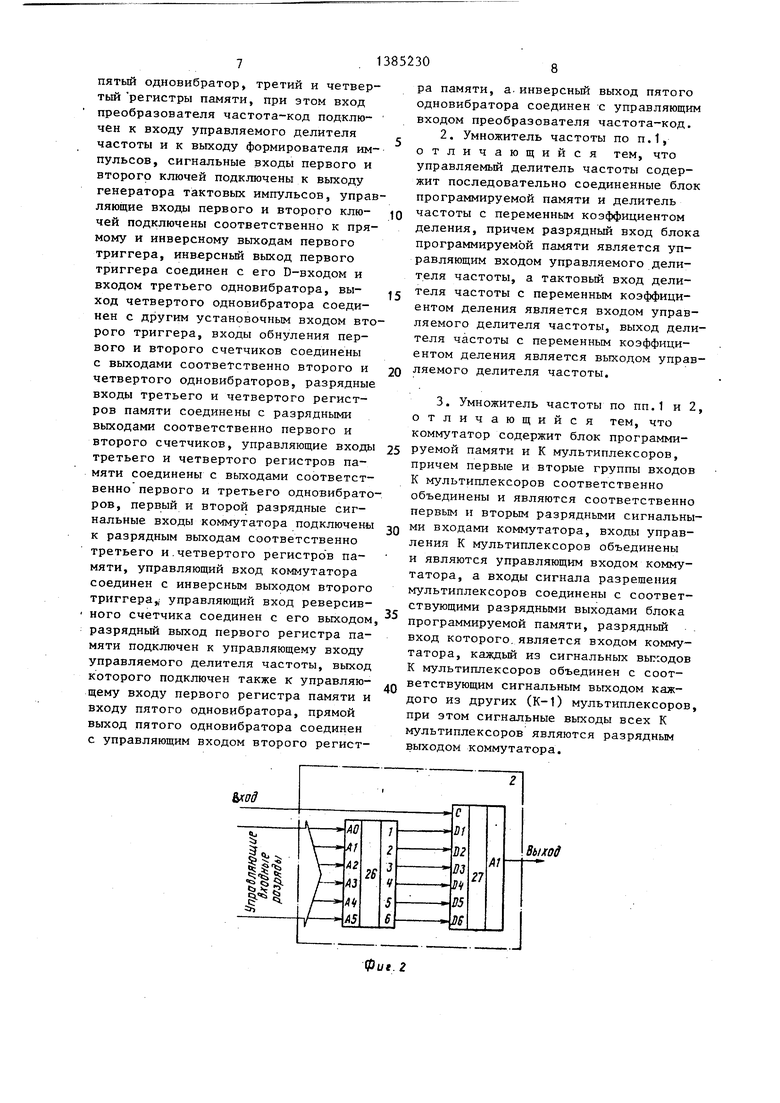

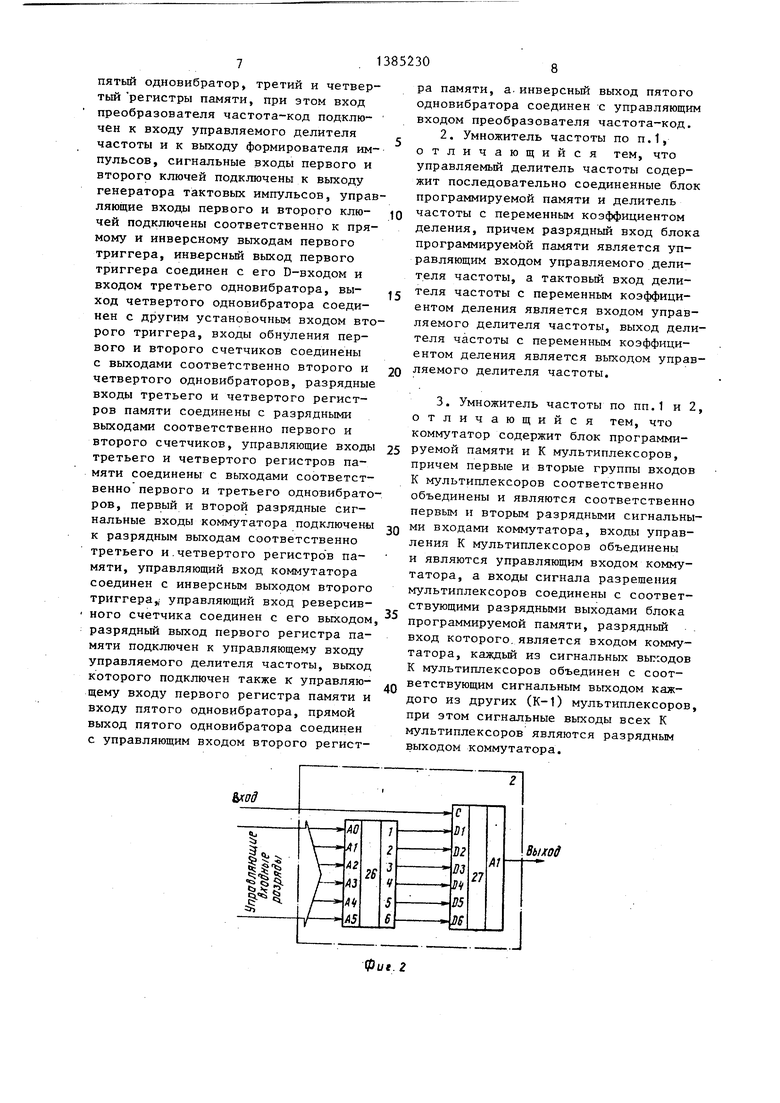

На фиг.1 представлена структурная электрическая схема умножителя частоты; на фиг.2 - схема управляемого делителя частоты; на фиг.З - схема коммутатора; на фиг.4 а,б,в,г,д,е, ж,з,и,к,л,м,н,о - временные диаграммы работы умножителя частоты.

Умножитель частоты содержит формирователь импульсов 1, управляемый делитель -частоты 2, первый регистр памяти 3, преобразователь частота- код А, первый триггер 5, пятый одно- вибратор 6, первый одновибратор 7, третий одновибратор 8, второй регист памяти 9, генератор тактовых импуль

сов 10, второй одновибратор 11, четвертый одновибратор 12, делитель частоты 13, первый ключ 14, первый счетчик 15, третий регистр памяти 16, фазовый детектор 17, второй триггер 18, коммутатор 19, фильтр нижних частот 20, второй ключ 21, второй счетчик 22, четвертьй регистр памяти 23, управляемый генератор 24 и реверсивный счетчик 25.

Управляемый делитель частоты 2 (фиг.2) содержит блок программируемой памяти (БПТТ) 26 и делитель частоты с переменным коэффициентом деления 27.

Коммутатор 19 (фиг.З) содержит блок программируемой памяти (БПП) 28 и К-мультиплексоров 29,,.,.,29 (фиг.З).

Умножитель частоты работает следующим образом.

Пусть в исходном состоянии первый триггер 5 находится-в состоянии логической 1. В этом случае первый ключ 14 открыт, а второй ключ 21 закрыт. Формирователь импульсов 1 пре- образует входной сигнал к нормированным значениям логических уровней и длительностей перепадов (фиг.4а). Полученный прямоугольный сигнал поступает на вход управляемого делителя частоты 2, на выходе которого формируется импульсная последовательность (фиг.4б), положительные перепады которой запускают первый триггер 5

20

40

(фиг.4в) и пятый одновибратор 6, а также записывают в первый регистр памяти 3 значение выходного кода преобразователя частота-код 4. Выходной паралельный код преобразователя частота-код 4, соответствующий измеренной к этому моменту частоте входного сигнала, определяет значение коэффи Q циента деления управляемого делителя частоты 2.

Основным элементом управляемого делителя частоты 2 (фиг.2) является делитель частоты с переменным коэф15, фициентом деления 27. Его разрядный вход, предназначенный для выбора коэффициента деления, соединен с соответствующим разрядным выходом блока программируемой памяти 26, Программа БПП 26 обеспечивает наличие логической 1 лишь на одном из его выходов, соответствующего старшему , (вес которого наибольший) разрядн о- му входу. При отсутствии уровня ло- 25 гической 1 на разрядном входе БПП 26 логическая 1 появляется на разрядном выходе соединенном с разрядным входом D1 (фиг.2) делителя частоты с переменным коэффициентом деления 27. Это соответствует коэффициенту деления управляемого делителя частоТы 2 равного двум.

Минимальный коэффициент деления (равный двум) соответствует нижней 35 области диапазона рабочих частот умножителя, при которой погрешность квантования не превышает заданного значения. В этом случае фазовые флюк-- туации выходного сигнала умножителя частоты, обусловленные погрешностью

квантования, минимальны и не вызывают потерю синхронизации следящей системы фазовой автоматической подстройки частоты (ФАШО , так как допустимой полосы удержания последней достаточно для осуществления непрерывной подстройки частоты. С ростом частоты умножаемого сигнала пропорционально увеличивается значение коэффициента деления, и обратно, при перестройке частоты сверху вниз значение коэффициента деления пропорционально уменьшается. Отношение длительности периода импульсной последовательности на выходе управляемого делителя частоты 2 к длительности периода повторения квантующих импульсов не изменяется. Таким образом, погрешность квантования входного сигнала остается неизменно минимальной, В конечном итоге точность умножения возрастает в широком диапазоне частот.

На инверсном выходе пятого одно- вибратора 6 формируются /толожитель- ные импульсы внешнего з апуска преоб- -разователя частота-код 4. На выходах первого триггера 5 формируются импульсы (фиг.4в). длительность котоik

рых равна длительности п

Т

2 периодов Tj. входного сигнала (К 1,2, 3,...), максимальное значение К определяется верхней границей частотного диапазона умножителя). В течениеf5 первый канал подсчета импульсов.

первых п периодов Т. входного сигнала первый счетчик 15 подсчитывает количество квантующих импульсов с периодом Т 7. (фиг.4з). Соотfrru 20

ношение частот f генератора тактовых импульсов 10 и fv,r управляемого генератора 24 определяется заданным коэффициентом умножения частоты К у„ -Ьц 25

гти

Частота генератора тактовых импульсов 10 (фиг.4ж) выбирается, исходя из требования обеспечения необходимой разрешающей способности при 1(;вантовании. Изменение дискретного значения коэффициента умножения частоты осуществляется путем изменения номинального значения частоты f

30

vr

vr

управляемого генератора 24 в преде- 35 лах допустимого быстродействия реверсивного счетчика 25.

После окончания первых п периодов Тс входного сигнала первый триггер 5 устанавливается в состояние О, а в первом счетчике 15 фиксируется код N п Т J./T |.jj, соответствующий длительности первых п периодов. Одновременно откроется второй ключ 21 и второй счетчик 22 начнет подсчитывать количество квантующих импульсов, пришедших на тактовый вход счетчика (фиг. 4м) за вторые п периодов Т (- входного сигнала. Код N записывается в третий регистр памяти 16 положительным перепадом отрицательных импульсов на выходе первого одновибратора 7 (фиг.4д). Длительность этих импульсов достаточна для установления статического кода на разрядных выходах первого счетчика 15, после блокировки посредством первого ключа 14 поступления на тактовый вход первого

счетчика 15 импульсов f с генератора тактовых импульсов 10. Запись информации, содержащейся в первом регистре памяти 3, во второй регистр памяти 9 осуществляется отрицательными импульсами, формируемыми на прямом выходе пятого одновибратора 6 (фиг,4г). После записи информации в третий регистр памяти 16, первьш счетчик 15 обнуляется выходными импульсами второго одновибратора 11, формируемыми в момент окончания импульсов записи (фиг.4е). Тем самым

20

25

включающий в себя первый ключ 14, первый счетчик 15 и третий регистр памяти 16 подготавливается к счету импульсов fpTM пришедших за время третьих п периодов Т, входного сиг30

35

нала. Аналогично работает второй канал подсчета импульсов, содержащий второй ключ 21, второй счетчик 22 и четвертый регистр памяти 23. После окончания вторых п периодов Т входного сигнала во втором счетчике 22 фиксируется код N-I. После записи кода N-2 четвертьш регистр памяти 23 выходным импульсом третьего одновибратора 8 (фиг.4к), второй счетчик 22 обнуляется выходным импульсом чет- вертого одновибратора 12 (фиг.4л). Тем самым схема подготавливается к счету четвертых п периодов Т входного сигнала. Использование двух идентичных схем подсчета количества квантующих импульсов позволяет обеспечить работу умножителя частоты при значительных изменениях частоты входного сигнала. Наличие лишь одной такой схемы предполагает необходимость неинформативного интервала в ее работе вслед за измерительным - так называемой мертвой зоны, в течение

д которого осуществляется запись выходной информации счетчиков в регистре

памяти и последующее обнуление счетчиков. Уход частоты входного сигнала за это время Может превысить границы полосы захвата системы ФАПЧ, что приведет к нарушению работы умножителя. Коммутатор 19 подключает разрядные выходы третьего регистра памяти 16 или четвертого регистра памяти 23 к предустановочному входу реверсивного

40

50

55

счетчика 25. Для получения на пред- установочном входе реверсивного счетчика 25 кода N N /п, соответствующего одному периоду Тс входного

сигнала умножителя частоты независимо от количества усредняемых перио- дов, в качестве коммутируемых используются коды, взятые от различных групп разрядных сигнальных входов, которые сдвинуты между собой на один двоичный разряд. Коммутация той или иной группы разрядных выходов третьего регистра памяти 16 или четвертого регистра памяти 23 эквивалентна сдвигу на то или иное число разрядов кода, соответствующего п периодам входного сигнала. Управление коммутацией таких групп осуществляется выходным кодом преобразователя частота-код 4, записанным во второй регистр памяти 9о Коммутатор 19 (фиг.З может .быть выполнен на базе интегральных мультиплексоров, имеющих три выходных состояния и .допускающих объединение по выходам. Поочередное подключение разрядных выходов третьего регистра памяти 16 или четвертого регистра памяти 23 достигается с помощью выходного сигнала второго триггера 18 (фиг.4н), поступающего на управляющий вход коммутатора 19. При наличии логического О на управляющем входе коммутатора 19, на разряд- ньй выход коммутатора 19 поступает сигнал с разрядного выхода третьего регистра памяти 16, а при наличии логической 1 - сигнал с разрядного выхода четвертого регистра памяти 23.

Наличие логического О на входе сигнала разрешения одного из мульти- плексоров 29,,...,29 к разрешает подключение соответствующей группы разрядных выходов третьего регистра памяти 16 или четвертого регистра памдти 23 к предустановочному входу реверсивного счетчика 25. Наличие логической 1 переводит мультиплексоры 29,...,29 в состояние высокоимпедансного выхода. Подключение к разрядному выходу сигнального выхода мультиплексора 29,, эквивалентна подключению кода соответствующего одному периоду Т, входного сигнала умножителя частоты, при этом коэффициент деления управляемого де- .лителя ча.стоты 2 равен 2 2().

Подключение мультиплексора 29i (на фиг.З не показан) эквивалентна подключению, кода, соответствующего одному периоду Т. входного сигнала при коэффициенте деления управляемого делителя частоты 2, равном 2 4

(). Входы сигнала разрешения мультиплексоров 29V,...,29ц соединены с соответствующими разрядными выходами БПП 28. Разрядный вход БПП 28 подключен к разрядному выходу второго регистра памяти 9. Программа БПП 28 обеспечиваем наличие логического О одновременно лишь на одном из его разрядных выходов, соответствующего старшему разрядному входу БПП 28. При отсутствии уровня логической 1 на разрядном входе БПП 28, логический О появляется на разрядном выходе

БПП 28, соединенном со входом сигнала разрешения мультиплексора 29,.

Реверсивный счетчик 25 работающий после предустановки в режиме вычитания, осуществляет деление периода TC входного сигнала или, что то же самое, умножение его частоты. На . тактовый вход реверсивного счетчика 25 поступают импульсы от управляемого генератора 24, частота повторения

этих импульсов fyr

ту квантования f.

превьппает часто- V м №. раУ

0

5

0

5

0

5

Форму ла изо.бретения

1. Умножитель частоты, содержащий формирователь импульсов, генератор тактовых импульсов, первый и второй ключи, первый и второй счетчики, последовательно соединенные делитель частоты, фазовый детектор, фильтр нижних частот, управляемый генератор и реверсивный счет чик, выход которого соединен с входом дели- т еля частоты, сигнальные выходы первого и второго ключей соедйне-ны с тактовыми входами соответственно первого и второго счетчиков, другой вход фазового детектора соединен с выходом формирователя импульсов, отличающийся тем, что, с целью повьш1ения точности умножения при расширении диапазона умножаемых частот, введены последовательно соединенные управляемьй делитель частоты, первый триггер, первый одновибратор, второй одновибратор и вторвй триггер, последовательно соединенные третий одновибратор и четвертый одновибратор, последовательно соединенные преобразователь частота-код, первьй регистр памяти, второй регистр памяти и коммутатор, разрядный, выход которого подключен к предустановочному входу реверсивного счетчика, а также

пятый одновибратор, третий и четвертый регистры памяти, при этом вход преобразователя частота-код подклю- чен к входу управляемого делителя частоты и к выходу формирователя импульсов, сигнальные входы первого и второго ключей подключены к выходу генератора тактовьрс импульсов, управляющие входы первого и второго ключей подключены соответственно к прямому и инверсному выходам первого триггера, инверсньш выход первого триггера соединен с его D-входом и входом третьего одновибратора, выход четвертого одновибратора соединен с другим установочным входом второго триггера, входы обнуления первого и второго счетчиков соединены с выходами соответственно второго и четвертого одновибраторов, разрядные входы третьего и четвертого регистров памяти соединены с разрядными вьпсодами соответственно первого и

5

0

ра памяти, а.инверсный выход пятого одновибратора соединен с управляющим входом преобразователя частота-код.

2.Умножитель частоты по п.1, отличающийся тем, что управляемый делитель частоты содержит последовательно соединенные блок программируемой памяти и делитель частоты с переменньм коэффициентом деления, причем разрядный вход блока программируемой памяти является управляющим входом управляемого делителя частоты, а тактовый вход делителя частоты с переменным коэффициентом деления является входом управляемого делителя частоты, выход делителя частоты с переменным коэффициентом деления является выходом управляемого делителя частоты.

3.Умножитель частоты по пп.1 и 2, отличающийся тем, что коммутатор содержит блок программи

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1989 |

|

SU1741274A2 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Умножитель частоты следования импульсов (его варианты) | 1983 |

|

SU1120483A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР | 1992 |

|

RU2116620C1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Фазоимпульсный преобразователь | 1984 |

|

SU1256186A1 |

Изобретение относится к радиотехнике и м.б. использовано в различных устр-вах автоматики и измерительной техники при разработке фазометров, частотомеров, фазовращателей. Целью изобретения является повьшение точности умножения, при расширении диапазона умножаемых частот. Умножитель частоты содержит формирователь импульсов 1, г-р тактовых импульсов 10, делитель частоты 13, ключи 14, 21, счетчики 15, 22, фазовый детектор 17, фильтр нижних частот 20, уп- равляемьп г-р 24 и реверсивньш с4ет- чик-25. С целью повышения точности умножения введены управляемый делитель частоты 2, триггеры 5, 18, пять одновибраторов 7, 11, 8, 12, 6, преобразователь частота-код 4, четыре регистра памяти 3, 9, 16, 23, коммутатор 19. Использование двух идентичных схем подсчета кол-ва квантующих импульсов позволяет обеспечить работу умножителя частоты при значительных изменениях частоты входного сигнала. Отношение длительности периода импульсной последовательности на выходе управляемого делителя частоты 2 к длительности периода повторения квантующих импульсов не изменяется. Т.обр., погрешность квантования входного сигнала остается неизменно минимальной. Б конечном итоге точность умножения возрастает в широком диапазоне частот. 2 з,По ил. i (Л

второго счетчиков, управляющие входы 25 руемой памяти и К мультиплексоров.

третьего и четвертого регистров памяти соединены с выходами соответственно первого и третьего одновибраторов, первый и второй разрядные сигнальные входы коммутатора подключены к разрядным выходам соответственно третьего и.четвертого регистро в памяти, управляющий вход коммутатора соединен с инверсньм выходом второго триггера,, управляющий вход реверсивного счетчика соединен с его выходом разрядный выход первого регистра памяти подключен к управляющему входу управляемого делителя частоты, выход которого подключен также к управляющему входу первого регистра памяти и входу пятого одновибратора, прямой выход пятого одновибратора соединен с управляющим входом второго регист0

5

0

причем первые и вторые группы входов К мультиплексоров соответственно объединены и являются соответственно первым и вторым разрядными сигнальными входами коммутатора, входы управления К мультиплексоров объединены и являются управляющим входом коммутатора, а входы сигнала разрешения мультиплексоров соединены с соответствующими разрядными выходами блока программируемой памяти, разрядный вход которого, является входом коммутатора, каждый из сигнальных выходов К мультиплексоров объединен с соответствующим сигнальным выходом каждого из других (К-1) мультиплексоров, при этом сигнальные выходы всех К мультиплексоров являются разрядным выходом коммутатора.

Фие.г

| Умножитель частоты | 1976 |

|

SU621062A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты | 1979 |

|

SU834697A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-30—Публикация

1986-11-19—Подача