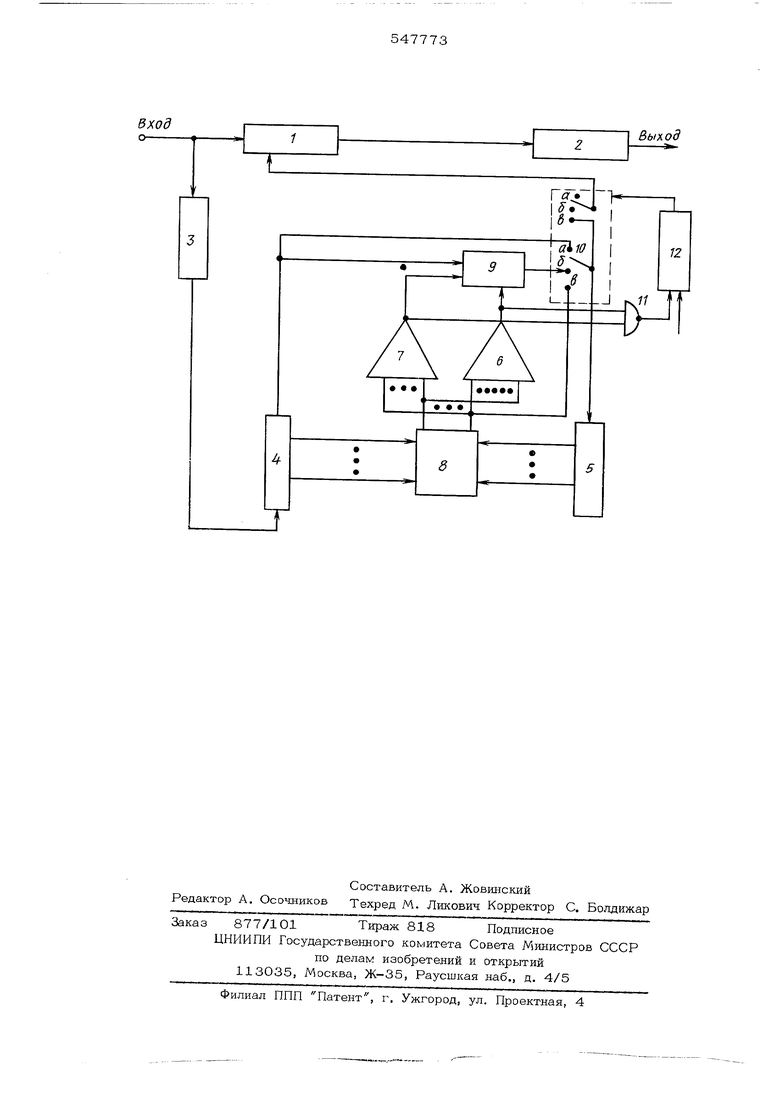

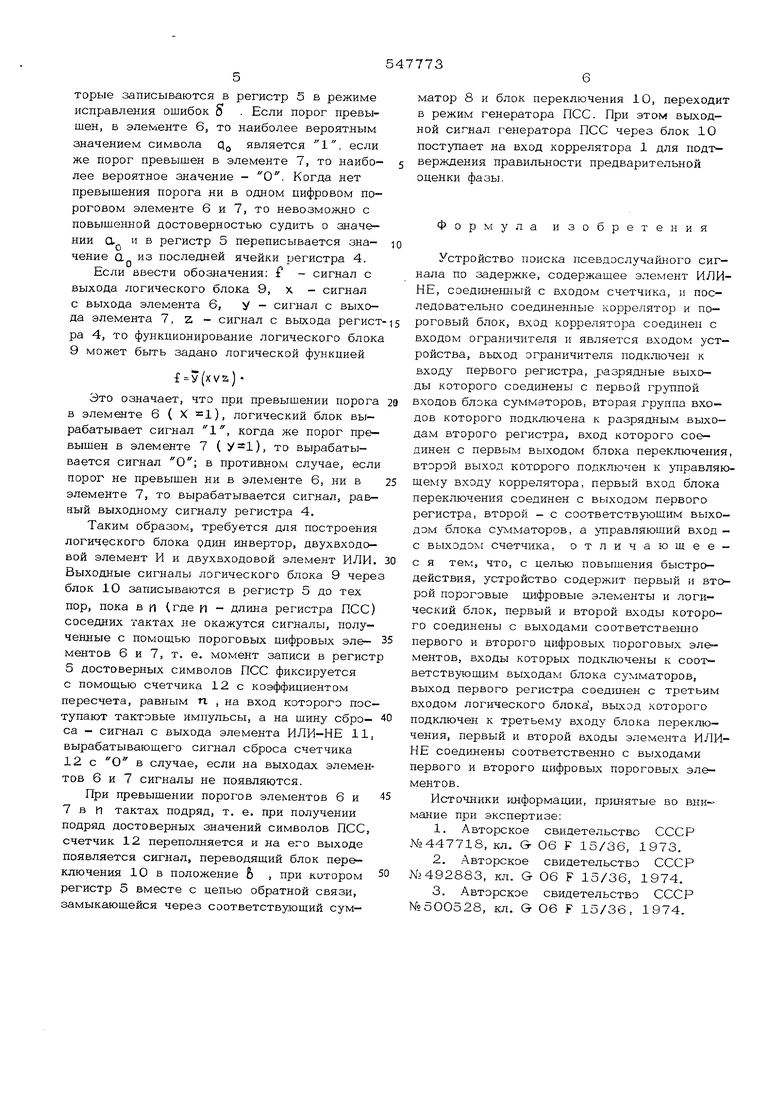

содержащее элемент ИЛИ-НЕ, соединенный с входом счетчика, и последовательно соединенные коррелятор и нороговый блок. Вход коррелятора связан с входом ограничителя и является входом устройства, выход ограничителя - с входом нервого регистра, разрядные выходы этого регистра - с первой группой входов блока сумматоров, вторая групна входов которого подключена к разрядным выходам второго регистра, входом соединенного с первым выходом блока переключения, второй выход блока переключения к управляющему входу коррелятора. Первый вход блока переключения соединен с вы ходом первого регистра, второй - с соответствующим выходом блока сумматоров, а управляющий вход - с выходом счетчика. Однако такое устройство не обеспечивает достаточно высокого быстродействия. Цель изобретения - сокращение времени поиска пес по задержке, т. е. повышение быстродействия. Это достигается тем, что устройство содержит первый и второй пороговые цифровые элементы и логический блок. Первый и второй входы логического блока соединены с выходами соответственно первого и второго цифровых пороговых элементов, входы которых подключены к соответствующим выходам блока сумматоров, выход первого регистра с третьим входом логического блока, выход которого подключен к третьему входу блока переключения, а первый и второй входы эле мента ИЛИ-НЕ - соответственно с выходам первого и второго цифровых пороговых элементов., Сущность изобретения состоит в обеспечении автоматической остановки процесса исправления ошибок по достижении наиболее достоверной оценки фазы. Блок-схема устройства показана на чертеже. Устройство содержит коррелятор 1, поро вый блок 2, ограничитель 3, регистры сдви га 4 и 5, цифровые пороговые элементы 6 и 7, блок сумматоров 8 по модулю два, логический блок 9 выбора сигнала записи, блок переключения 10 - сдвоенный переклю чатель, двухвходовой элемент ИЛИ-НЕ 11 и счетчик 12. Входная щина устройства соединена с одним из входов коррелятора 1, выходом по ключенного к входу порогового блока 2, выход которого является выходом всего устройства. Вход регистра 4 через ограничитель 3 подключен к входной шине устройства, выход регистра 4 через блок переключения 10 - к входу регистра 5, выходы регистров 4 и 5 - к входам блока сумматора 8 по модулю два, выходы которых сое k входами порогового цифрового инены с 6. Параллельно упомянутым k вхолементаам порогового элемента 6 подсоединены ходы дополнительного порогового элемента 7с инверторами на входах. Выходы цифровых пороговых элементов 6 и 7 и выход региста 4 через логический блок 9 выработки игнала записи и блок переключения Ю подключены к входу регистра 5. Параллельно входам цифровых пороговых элементов 6 и 7 включены входы элемента ИЛИ-НЕ 11, выход которого подключен к шине сброса счетчика 12, входом связанного с тактовой шиной, а выходом - с шиной управления блока переключения 10. Выход сумматора по модулю два из блока сумматоров 8, подключенного к разрядным выходам регистра 5, соединен через блок 10 с вторым входом коррелятора 1. Устройство работает следующим образом. В исходном cocтoя iии положение блокапереключателя 10 соответствует тому, что подвижные контакты переключателя находятся в положении Q и видеосигнал с выхода ограничителя 3 поступает в регистры 4 и 5. После заполнения всех ячеек регистров 4 и 5 блок переключения устанавливается в положение б , при этом, на вход регистра 4 продолжают поступать сигналы с выхода ограничителя 3 . На выходах блока суммато- ров по модулю два вырабатываются сигналы, соответствующие значению разряда Q регистра 4, проходящие на входы цифровых пороговых элементов 6 и 7, пороги которых ( одинаковы и превышают порог мажоритарного элемента На выходе порогового элемента 6 появляется сигнал только при условии, если число единичных входных сигналов больше или равно h , а на выходе цифрового порогового элемента 7 образуется сигнал, если число нулевых входных сигналов больше или равно h (так как входы порогового цифрового элемента 7 инвертированы). Таким образом, назначение цифровых пороговых элементов 6 и 7 состоит в выработке только наиболее достоверных элементарных символов СС. В связи с тем, что при большой вероятности искажения символов факт превыщения порога в цифровых пороговых элементах 6 и 7 имеет место не в каждом такте, то на вход регистра 5 кроме достоверных значений символов поступает часть символов с выхода регистра 4. Запись соответствующих символов с цифровых пороговых элементов 6 и 7 или с выхода регистра 4 проводится с помощью логического блока О выбора сигнала записи. Логический блок 9 вырабатывает сигналы, соответствующие значениям символа О , ко-

торые записываются в регистр 5 в режиме исправления ошибок 5 . Если порог превышен, в элементе 6, то наиболее вероятным значением символа QQ является 1, если же порог превышен в элементе 7, то наиболее вероятное значение - О. Когда нет превышения порога ни в одном цифровом пороговом элементе 6 и 7, то невозможно с повышенной достоверностью судить о значении О- ив регистр 5 переписывается зна- чение QL из последней ячейки регистра 4. Если ввести обозначения; - сигнал с выхода логического блока 9, х - сигнал с выхода элемента 6, У - сигнал с выхода элемента 7, z - сигнал с выхода регист ра 4, то функционирование логического блока 9 может быть задано логической функцией

f y(xv2.

Это означает, что при превышении порога в элементе 6 ( X 1), логический блок вырабатывает сигнал 1, когда же порог превышен в элементе 7 ( ), то вырабатывается сигнал в пpoтивнo случае, если порог не превышен ни в элементе 6, ни в элементе 7, то вырабатывается сигнал, равный выходному сигналу регистра 4.

Таким образом, требуется для построения логического блока рдин инвертор, двухвходо- вой элемент И и двухвходовой элемент ИЛИ. Выходные сигналы логического блока 9 чере блок 10 записываются в регистр 5 до тех пор, пока в и (где ц - длина регистра ПСС) соседних тактах не окажутся сигналы, полученные с помощью пороговых цифровых эле- ментов 6 и 7, т, е. момент записи в регист 5 достоверных символов ПСС фиксируется с помощью счетчика 12 с коэффициентам пересчета, равным п , на вход которого поступают тактовые импульсы, а на шину сбро- са - сигнал с выхода элемента ИЛИ-НЕ 11, вырабатывающего сигнал сброса счетчика 12 с О в случае, если на выходах элементов 6 и 7 сигналы не появляются.

При превышении порогов элементов 6 и 7 в и тактах подряд, т. е. при получении подряд достоверных значений символов ПСС, счетчик 12 переполняется и на его выходе появляется сигнал, переводящий блок переключения 10 в положение 6 , при котором регистр 5 вместе с депью обратной связи, замыкающейся через соответствующий сумматор 8 и блок переключения 10, переходит в режим генератора ПСС. При этом выходной сигнал генератора ПСС через блок 10 поступает на вход коррелятора 1 для подтверждения правильности предварительной оценки фазы.

Формула изобретения

Устройство поиска псевдослучайного сигнала по задержке, содержащее элемент ИЛИНЕ, соед1ше1шый с входом счетчика, и последовательно соединенные коррелятор и пороговый блок, вход коррелятора соединен с входом ограничителя и является входом устройства, выход ограничителя подключен к входу первого регистра, разрядные выходы которого соединены с первой группой входов блока сумматоров, вторая группа входов которого подключена к разрядным выходам второго регистра, вход которого соединен с первым выходом блока переключения второй выход которого подключен к управляющему входу коррелятора, первый вход блока переключения соединен с выходом первого регистра, второй - с соответствующим выходом блока сумматоров, а управляющий вход - с выходом счетчика, отличающеес я тем, что, с целью повышения быстродействия, устройство содержит первый и второй пороговые цифровые элементы и логический блок, первый и второй входы которого соединены с выходами соответственно первого и второго цифровых пороговых элементов, входы которых подключены к соответствующим выходам блока сумматоров, выход первого регистра с третьим входом логического блока , выход которого подключен к третьему входу блока переключения, первый и второй входы элемента ИЛИНЕ соединены соответственно с выходами первого и второго цифровых пороговых элементов.

Источники информации, пр1шятые во внимание при экспертизе:

1.Авторское свидетельство СССР №447718, кл. G- Об F 15/36, 1973.

2..А.вторское свидетельство СССР jNa 492883, кл. G Об F 15/36, 1974.

3.Авторское свидетельство СССР №500528, кл. G Об F 15/36, 1974.

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации псевдослучайного сигнала | 1974 |

|

SU540394A1 |

| Устройство для определения фазы псевдослучайного сигнала | 1975 |

|

SU559423A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| ВСЕСОЮЗНАЯ 1"ЛШТНО.Ш(кгт-ЯАя/ | 1973 |

|

SU374594A1 |

| Устройство для поиска псевдослучайного сигнала по задержке | 1974 |

|

SU500528A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Устройство поиска псевдослучайных сигналов | 1972 |

|

SU470082A1 |

| Устройство для синхронизации м-последовательностей с инверсной модуляцией | 1977 |

|

SU651493A2 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840116A2 |

Авторы

Даты

1977-02-25—Публикация

1975-06-30—Подача