1

Изобретение относится к области электротехники и может быть использовано в качестве источника питания интегральных схем.

Известен стабилизатор постоянного напряжения, содержащий регулирующий элемент, усилитель обратной связи и источник опорного напряжения. Недостаток этого стабилизатора состоит в том, что для получения высокого коэффициента стабилизапии выходного напряжения требуется высокий коэффициент у.;иления усилителя обратной связи, что приводит к усложнению схемы. Известен также стабилизатор, являющийся наиболее близким по технической сущности и достигаемому результату к изобретению. Он содержит два последовательно включенных усилительных каскада, каждый из которых содержит управляющий и нагрузочный полевой транзисторы, при этом затворы нагрузочных транзисторов присоединены к их стокам, а истоки - к стокам соответствующих управляющих транзисторов, истоки которых подключены к земляной щине стабилизатора, и третий усилительный каскад, подключенный стоком к выходной клемме и через конденсатор к земляной щине. Недостатком этого стабилизатора является склонность к самовозбуждению, свойственная трехкаскадным усилителям, охваченным обратной связью, устраняемая подключением к выходной клемме конденсатора большой емкости, что препятствует полной микроминиатюризации устройства.

Кроме того, в известном устройстве идеальная стабильность выходного напряжения может быть доступна только при бесконечно больщом коэффициенте усиления усилителя. Что практически неосуществимо 1 , 2 .

Цель изобретения - улучщение стабильности выходного напряжения, обеспечение возможности микроминиатюризации и повышение устойчивости работы устройства.

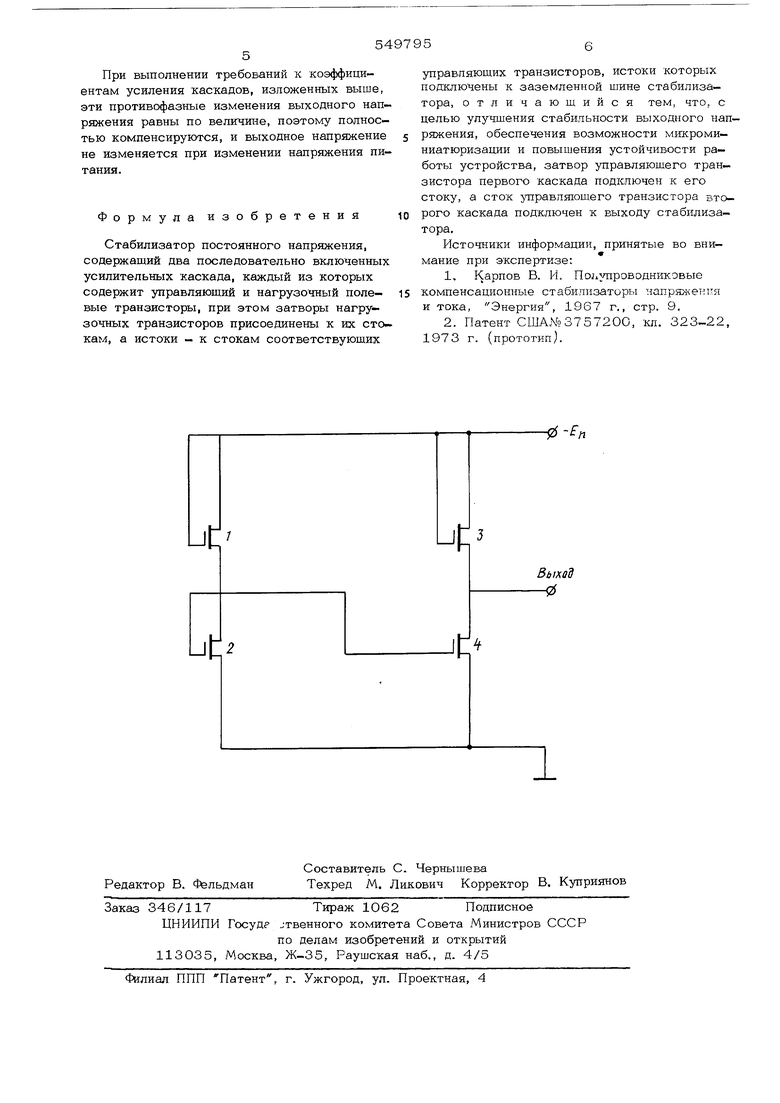

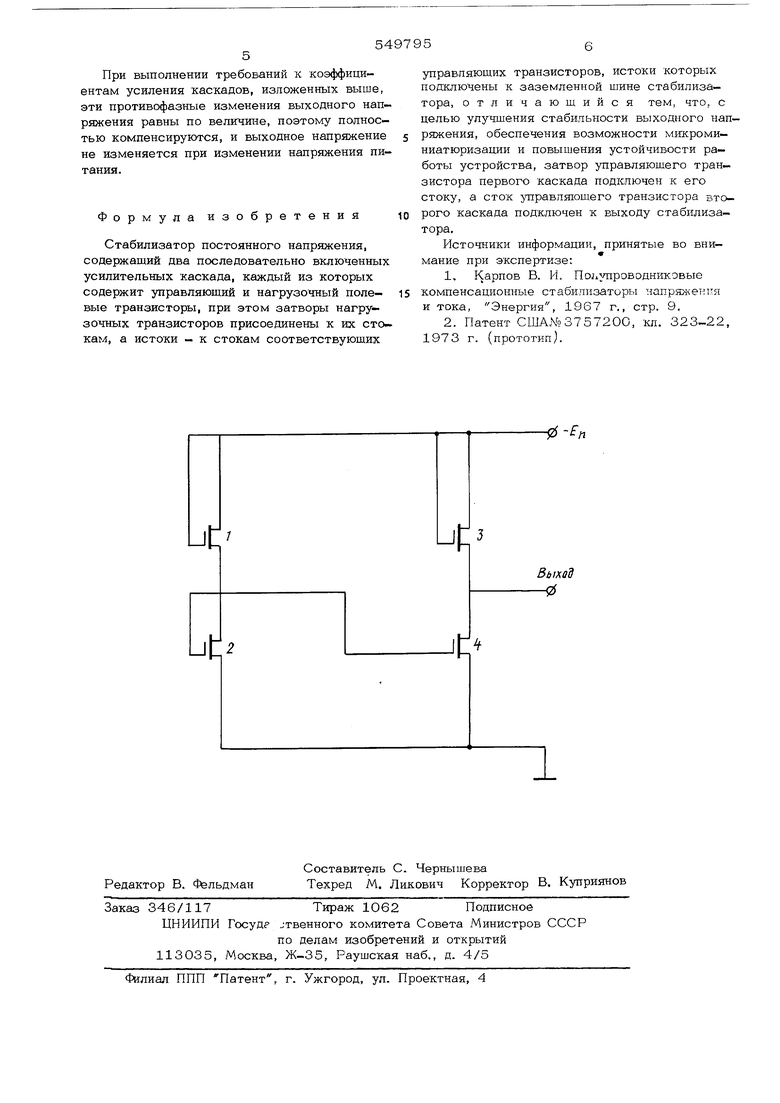

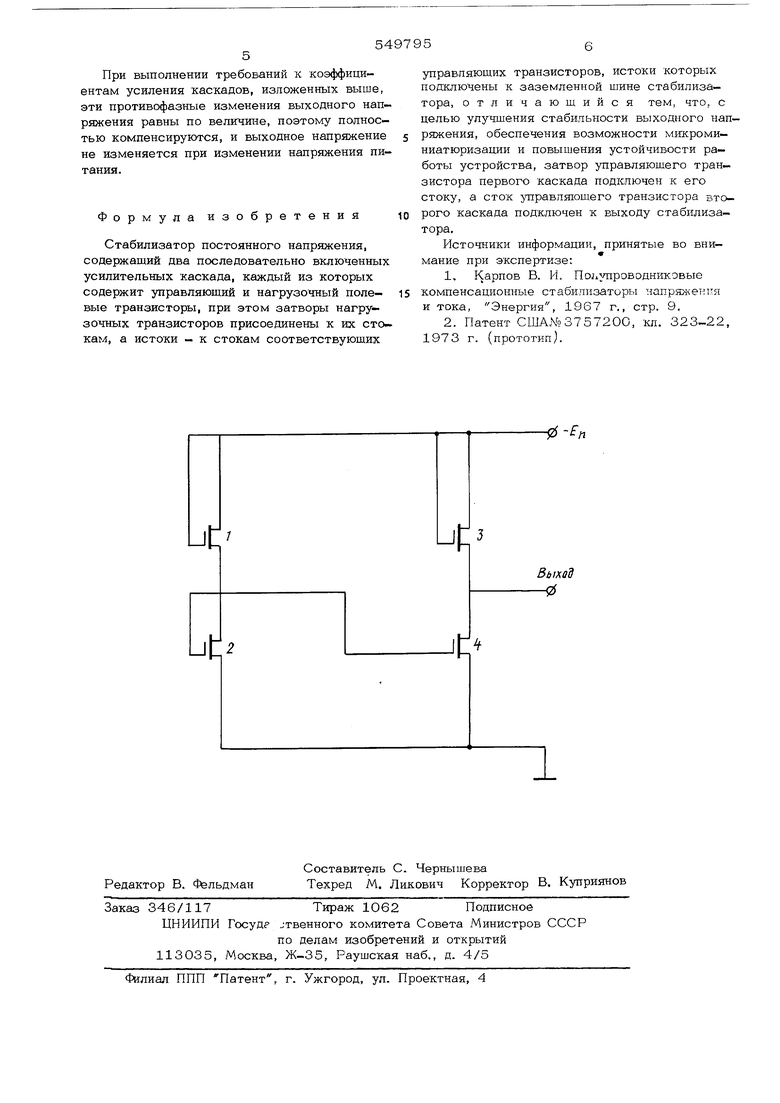

Поставленная цель достигается тем, что в стабилизаторе, содержащем два последовательно включенных усилительных каскада, каждый из которых содержит управляющий и нагрузочный полевые транзисторы, при этом затворы нагрузочных транзисторов присоединены к их стокам, а истоки-к стокам соответствующих управляющих транзисторов, истоки которых подключены к заземленной шине стабилизатора, затвор управляющего транзистора первого каскада подключен к его стоку, сток управляющего транзистора второго каскада подключен к выходу стабили затора. На чертеже приведена электрическая схема стабилизатора постоянного напряжения. Первый усилительный каскад состоит из нагрузочного транзистора 1 и управляющего транзистора 2. Второй - из нагрузочного транзистора 3 и управляющего транзистора 4. В исходном состоянии через оба усилительных каскада протекает ток; напряжение на затворе и стоке транзистора 2 устанавли вается на уровне, определяемом соотношением электрических параметров транзисторов 1 и 2, величиной порогового напряжения и напряжения питания Е Напряжение стока транзистора 2 подае на затвор транзистора 4,благодаря чему ряду с электрическими характеристиками транзисторов 3 и 4, напряжением питания Е и порога И Q , обеспечиваются определ ный ток через транзисторы 3 и 4 и вел чина напряжения на стоке транзистора 4, т.е. выходное напряжение устройства. Ток, текущий через транзистор 1,равен - -(Е ток через транзистор 1; где Л |), - крутизна транзистора 1; т - напряжение питания; (J - пороговое напряжение транзи тора, одинаковое для всех т зисторов интегральной схем и потенциал стока транзистора Ток через транзистор 2 равен Э, V---r(JcrUo) и 2 соедин Учитвая, что транзисторы 1 ны последовательно, r- zТок через транзисторы 3 и 4, работающ в пологой области выходных характерист определяется соответственно (1-и-( (В 4. где Usbix - выходной потенциал. Решив совместно уравнение (1)-г(б),нахо язь ивыхс и параметрами транзисов ( 1 }: ловием стабильности , при изменении является (8) (8) следует Так как коэффициент усиления первого кас- када k равен У-о а второго 2 то условие (9) примет следующий вид: -к, к. что является общим условием стабильности выходного напряжения. Поскольку р - , где Д - подвижность носителей в канале; , - диэлектрическая проницаемость и изолятора - окисла; t - толщина изолятора - окисла; - ширина канала МОП-транзистора; L, - длина канала МОП-транзистора и величина - постоянна для всех транзисторов интегральной схемы, то отношение крутизны транзисторов f определяется отношением их геометрических размеров, что обеспечивается интегральной технологией с высокой степенью точности. Таким образом, изменение напряжения питания Д Е вызвало бы такое же изменение напряжения на выходе -il-l-gj j . E,AUg,, Однако подключение затвора транзистора 4 к стоку транзистора 2 приводит к тому, что вызванное увеличением Е, увеличение И приводит к увеличению тока через транзистор 4 и увеличению падения напряжения на нагрузочном транзисторе 3, т.е. уменьшению напряжения на стоке транзистора 4. Таким образом, изменение напряжения питания вызывает два выше описанных процесса, приводящих к противоположным результатам: изменение выходного напряжения в той же фазе, что и напряжение питания, происходящее через транзистор 3,и изменение выходного напряжения в противофазе по отнощению к изменению напряжения питания, происходящее через транзисторы 1,2, 4.

При выполнении требований к коэффициентам усиления каскадов, изложенных выше, эти противофазные изменения выходного напряжения равны по величине, поэтому полностью компенсируются, и выходное напряжение не изменяется при изменении напряжения питания.

Формула изобретения

Стабилизатор постоянного напряжения, содержащий два последовательно включенных усилительных каскада, каждый из которых содержит управляющий и нагрузочный полевые транзисторы, при этом затворы нагрузочных транзисторов присоединены к их стокам, а истоки - к стокам соответствующих

управляющих транзисторов, истоки которых подключены к заземленной шине стабилизатора, отличающийся тем, что, с целью улучшения стабильности выходного напряжения, обеспечения возможности микроминиатюризации и повышения устойчивости работы устройства, затвор управляющего транзистора первого каскада подключен к его стоку, а сток управляющего транзистора второго каскада подключен к выходу стабилизатора.

Источники информации, принятые во внимание при экспертизе:

1.Карпов В. И. По:1упроводниковые компенсационные стабилизаторы напряй етпш и тока, Энергия, 1967 г., стр. 9.

2.Патент США№3757200, кл, 323-22, 1973 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор постоянного напряжения | 1976 |

|

SU571800A1 |

| Компенсационный стабилизатор постоянного напряжения | 1981 |

|

SU922698A1 |

| Стабилизатор постоянного напряжения | 1973 |

|

SU514280A1 |

| Стабилизатор постоянного напряжения | 1975 |

|

SU547747A1 |

| Формирователь стабилизированного напряжения на МДП-транзисторах | 1987 |

|

SU1534754A1 |

| Операционный усилитель на КМОП транзисторах | 1988 |

|

SU1676065A1 |

| Стабилизатор постоянного напряжения | 1984 |

|

SU1233125A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Управляемый операционный усилитель | 1985 |

|

SU1272473A1 |

| Стабилизатор напряжения постоянного тока | 1976 |

|

SU650066A1 |

ьс

Ь6

bf

Выход

-0

IP

Авторы

Даты

1977-03-05—Публикация

1975-07-09—Подача