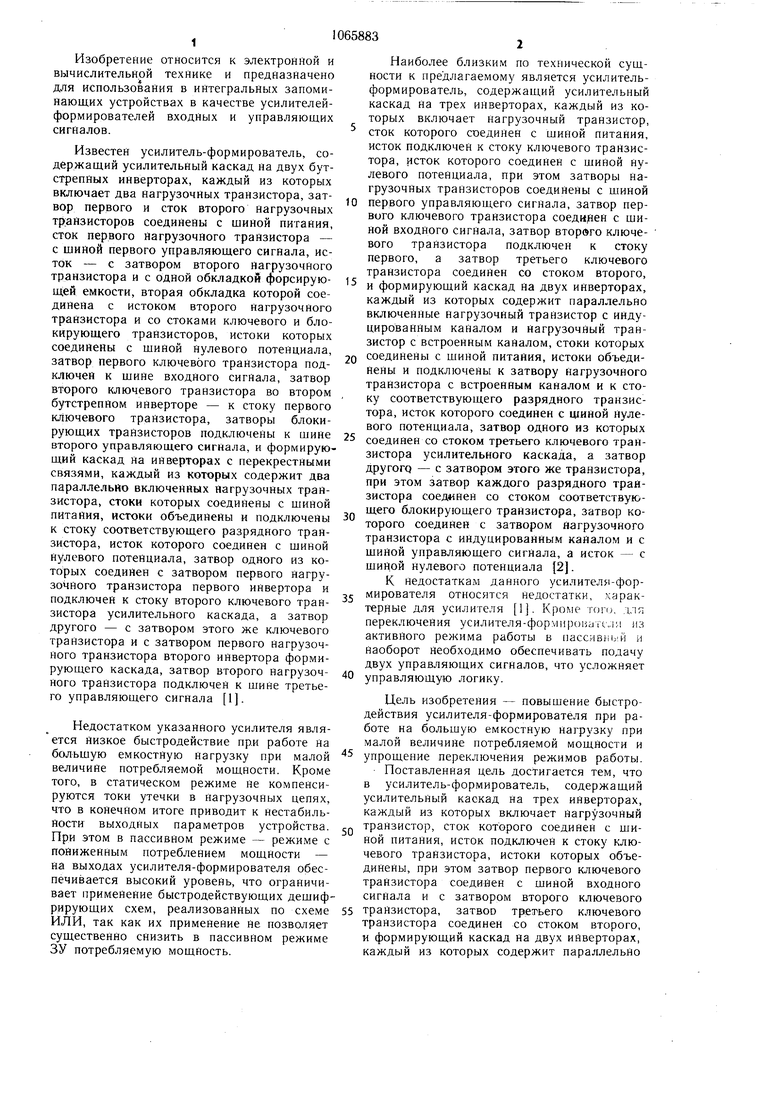

Изобретение относится к электронной и вычислительной технике и предназначено для использования в интегральных запоминающих устройствах в качестве усилителейформирователей входных и управляющих сигналов. Известен усилитель-формирователь, содержащий усилительный каскад на двух бутстрепйых инверторах, каждый из которых включает два нагрузочных транзистора, затвор первого и сток второго нагрузочных транзисторов соединены с щиной питания, сток первого нагрузочного транзистора - с щиной первого управляющего сигнала, исток - с затвором второго нагрузочного транзистора и с одной обкладкой форсирующей емкости, вторая обкладка которой соединена с истоком второго нагрузочного транзистора и со стоками ключевого и блокирующего транзисторов, истоки которых соединены с щиной Нулевого потенциала, затвор первого ключевого транзистора подключен к щине входного сигнала, затвор второго ключевого транзистора во втором бутстрепном инверторе - к стоку первого ключевого транзистора, затворы блокирующих транзисторов подключены к шине второго управляющего сигнала, и формирующий каскад на инверторах с перекрестными связями, каждый из которых содержит два параллельно включенных нагрузочных транзистора, стоки которых соединены с щиной питания, истоки объединены и подключены к стоку соответствующего разрядного транзистора, исток которого соединен с щиной нулевого потенциала, затвор одного из которых соединен с затвором первого нагрузочного транзистора первого инвертора и подключен к стоку второго ключевого транзистора усилительного каскада, а затвор другого - с затвором этого же ключевого транзистора и с затвором первого нагрузочного транзистора второго инвертора формирующего каскада, затвор второго нагрузочного транзистора подключен к щине третьего управляющего сигнала 1. Недостатком указанного усилителя является Низкое быстродействие при работе на больщую емкостную нагрузку при малой величине потребляемой мощности. Кроме того, в статическом режиме не компенсируются токи утечки в нагрузочных цепях, что в конечном итоге приводит к нестабильНости выходных параметров устройства. CQ При этом в пассивном режиме - режиме с пониженным потреблением мощности - на выходах усилителя-формирователя обеспечивается высокий уровень, что ограничивает применение быстродействующих дещифрирующих схем, реализованных по схеме55 ИЛИ, так как их применение не позволяет существенно снизить в пассивном режиме ЗУ потребляемую мощность. Наиболее близким по технической сущности к предлагаемому является усилительформирователь, содержащий усилительный каскад на трех инверторах, каждый из которых включает нагрузочный транзистор, сток которого соединен с щиной питания, исток подключен к стоку ключевого транзистора, исток которого соединен с щиной нулевого потенциала, при этом затворы нагрузочных транзисторов соединены с щиной первого управляющего сигнала, затвор первого ключевого транзистора соединен с шиной входного сигнала, затвор вторвго ключевого транзистора подключен к стоку первого, а затвор третьего ключевого транзистора соединен со стоком второго, „формирующий каскад на двух инверторах, каждый из которых содержит параллельно включенные нагрузочный транзистор с индуцированным каналом и нагрузочный трандистор с встроенным каналом, стоки которых соединены с тиной питания, истоки объединены и подключены к затвору нагрузочного транзистора с встроенным каналом и к стоку соответствующего разрядного транзистора, исток которого соединен с шиной нулевого потенциала, затвор одного из которых соединен со стоком третьего ключевого транзистора усилительного каскада, а затвор другогр - с затвором этого же транзистора, при этом затвор каждого разрядного трайзистора соединен со стоком соответствующего блокирующего транзистора, затвор которого соединен с затвором нагрузочного транзистора с индуцированным каналом и с щиной управляющего сигнала, а исток - с щиной Нулевого потенциала {2. К недостаткам данного усилителя-формирователя относятся недостатки, характерные для усилителя 1. Кроме тоги, для переключения усилителя-формиро15а1Ч.1:1 из активного режима работы в Г1ассив1м й и Наоборот необходимо обеспечивать подачу двух управляющих сигналов, что усложняет управляющую логику. Цель изобретения - повышение быстродействия усилителя-формирователя при работе на большую емкостную нагрузку при малой величине потребляемой мощности и упрощение переключения режимов работы, Поставленная цель достигается тем, что в усилитель-формирователь, содерж:ащий усилительный каскад на трех инверторах. каждыи из которых включает нагрузочный транзистор, сток которого соединен с нои питания, исток подключен к стоку ключевого транзистора, истоки которых объединены, при этом затвор первого ключевого транзистора соединен с щиной входного сигнала и с затвором второго ключевого транзистора, затвоо третьего ключевого транзистора соединен со стоком второго, и формирующий каскад на двух инверторах, каждый из которых содержит параллельно включенные нагрузочный транзистор с индуцированным каналом и нагрузочный транзистор с встроенным каналом, стоки которых соединены с шиной питания, истоки объединены и подключены к стоку соответствующего разрядного транзистора, затвор одного из которых соединен с затвором одного из Нагрузочных транзисторов усилительного каскада, а затвор другого - с затвором соответствующего ключевого транзистора, исток - с щиной Нулевого потенциала и с истоком блокирующего транзистора, дополнительно введены тра-й истор отсечки, СТОК которого соединен с истоками ключевых транзисторов, исток - с щиной нулевого потенциала, а затвор подключен к щине управляющего сигнала, два разделительных транзистора, стоки которых являются соответственно инверсным и прямым входами усилительного каскада, истоки подключены к затворам нагрузочных транзисторов формирующего каскада, а затворы подключены к щине управляющего сигнала, две форсирующие емкости, включенные каждая между затворами и истоками соответствующей пары нагрузочных транзисторов формирующего каскада, второй и третий нагрузочные транзисторы усилительного каскада выполнены с встроенным каналом, причем затвор первого нагрузочного транзистора усилительного каскада соединен с шийой питания, затвор второго соединен со стоком первого ключевого транзистора, затвор, третьего нагрузочного транзистора усилительного каскада соединен со стоком третьего ключевого транзистора, стоки блокирующих транзисторов подключены к затворам соответствующих нагрузочных транзисторов формирующего каскада, а затворы соедийейы со стоком транзистора отсечки. На чертеже представлена электрическая схема предлагаемого усилителя-формирователя. Усилитель-формирователь включает уси лительйый и формирующий каскады. Усилительный каскад содержит три нагрузочных МДП-транзистора 1-3, причем нагрузочные трайзисторы 2 и 3 со встроейным каналом, три ключевых МДО-транзистора 4-6 с ивдудиров.аййым кайалом, транзистор 7 отоечкй ййду|№аров,авйым «авадом, щину 8 ииташия, шийу 9 вхолйош ттала, щину 10 уш|э Ш1 8шишпо .ада и даийу U нулевого аоше9йздш1-{ш о|цмИ)рчуюзд,1йй с:а.екад содержит четыре ааг| а0чйых трайзист фа 12-15, причем йагрузочяые гpaйз«c PO, 12-14 - МДПтрайзистрры .с индуцированным каналом, а аагрузочные трайзисторы 13 и 15 - МДПТ;рэйзист.оры с :встроенным каналом, два разрядных МДП-транзистора 16 и 17 с индуцированным кайалом, два разделительных МДП-транзистора 18 и 19 с индуцированным каналом, два блокирующих МДП-транзистора 20 и 21 с индуцированным каналом, две форсирующие емкости 22 и 23, а также инверсный 24 и прямой 25 выходы усилителя. Усилитель работает в двух режимах: активном и пассивном. Рассмотрим работу усилителя-формирователя в активном режиме. В этом режиме на щину 10 управляющего сигнала подается потенциал логической «1, открывающий транзистор 7 отсечки и разделительные трайзисторы 18 и 19. Если на входную щину 9 подается потенциал логического «О, то ключевые трайзисторы 4 и 5 запираютеЯг Открытый транзистор 7 отсечки обеспечивает запирание блокирующих транзисторов 20 и 21. Емкостная нагрузка первого инвертора усилительного каскада намного меньще емкостной нагрузки второго и третьего инверторов, вследствие чего процессы перезаряда в первом инверторе происходят быстрее, в результате быстро открывается нагрузочный транзистор 2 с встроенным каналом, работающий в крутой -области и тем самым обеспечивающий максимальный трк заряда емкостной нагрузки второго инвертора и через открытый разделительный транзистор 18 ток заряда форсирующ,ей емкости 22, формирующей напряжение на затворе нагрузочного транзистора 12. При этом ключевой транзистор 6 открывается и на выходе третьего инвертора устанавливается уровень логического «О, запирающий разрядный транзистор 16. Как только напряжение на затворе Нагрузочного транзистора 12 становится выще порогового, нагрузочный транзистор 12 открывается и на его истоке появляется нарастающее напряжение, которое за счет положительной обратной связи приводит к перераспределению заряда форсирующей емкости 22, обеспечивающей на затворе нагрузочного транзистора 12 формирование напряжения, превышающего напряжение питания в нашем случае на 3 В (т.е. 8В), благодаря чему ускоряется процесс отработки сигнала логической «1 и Напряжение питания полностью передается инверсный выход усилителя-формирователя. Для ускорения процесса формирования сигнала логической «1, при заряде нагрузок с больщей емкостью при малой величине потребляемой мощности используется второй нагрузочный транзистор 13 с встроенным каналом, на затвор которого подается напряжение, превышающее напряжение питания затвора нагрузочного транзистора 12, вследствие чего при небольших геометрических размерах за счет высокой проводимости при работе в крутой области обеспечивается максимальный ток заряда. Кроме того, в статическом режиме нагрузочный транзистор 13 с встроенным

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

УСИЛИТЕЛЬ-ФОРМИРОВАТЕЛЬ, содержащий усилительный каскад на трех инверторах, каждый из которых включает нагрузочный транзистор, сток которого соединен с шиной питания, исток подключен к стоку ключевого транзистора, истоки которых объединены, при этом затвор первого ключевого транзистора соединен с шиной входного сигнала и с затвором второго ключевого транзистора, затвор третьего ключевого транзистора соединен со стоком второго, и формирующий каскад на двух инверторах, каждый из которых содержит параллельно включенные нагрузочный транзистор с индуцированным кана.йом и нагрузочный транзистор с встроенным каналом, стоки которых соединены с шиной питания, истоки объединены и подключены к стоку соответствующего разрядного транзистора, затвор одного из которых соединен с затвором одного из нагрузочных транзисторов усилительного каскада, а затвор другого - с затвором соответствующего ключевого транзистора, исток - с шиной нулевого потенциала и с истоком блокирующего транзистора, отличающийся тем, что, с целью повышения его быстродействия при работе на емкостную нагрузку при уменьшении потребляемой мощности и упрощения переключения режимов работы, в него введены транзистор отсечки, сток которого соединен с истоками ключевых транзисторов, исток - с шиной Нулевого потенциала, а затвор подключен к шине управляющего сигнала, два разделительных транзистора, стоки которых являются соответственно инверсным и прямым входами усилительного каскада истоки подключены к затворам нагрузочных транзисторов формирующего каскада, а затворы подключены к шине управляющего сигнала, две форсирующие емкости, включенные каждая 5 между затворами и истоками соответствую(Л щей пары нагрузочных транзисторов формирующего каскада, второй и третий нагрузочные транзисторы усилительного каскада выполнены с встроенным каналом, причем затвор первого нагрузочного транзистора усилительного каскада соединен с П1иной питания, затвор второго соединен со стоком первого ключевого транзистора, затвор третьего нагрузочного транзистора усилительного каскада соединен со стоком третьего ключевого Ci транзистора, стоки блокирующих транзисел торов подключены к затворам соответствуюоо щих нагрузочных транзисторов формирую00 00 щего каскада, а затворы соединены со стоком транзистора отсечки. о// о//

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4161040, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4160291, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1984-01-07—Публикация

1982-04-06—Подача