(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1974 |

|

SU741321A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1007106A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ В ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2022 |

|

RU2787294C1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

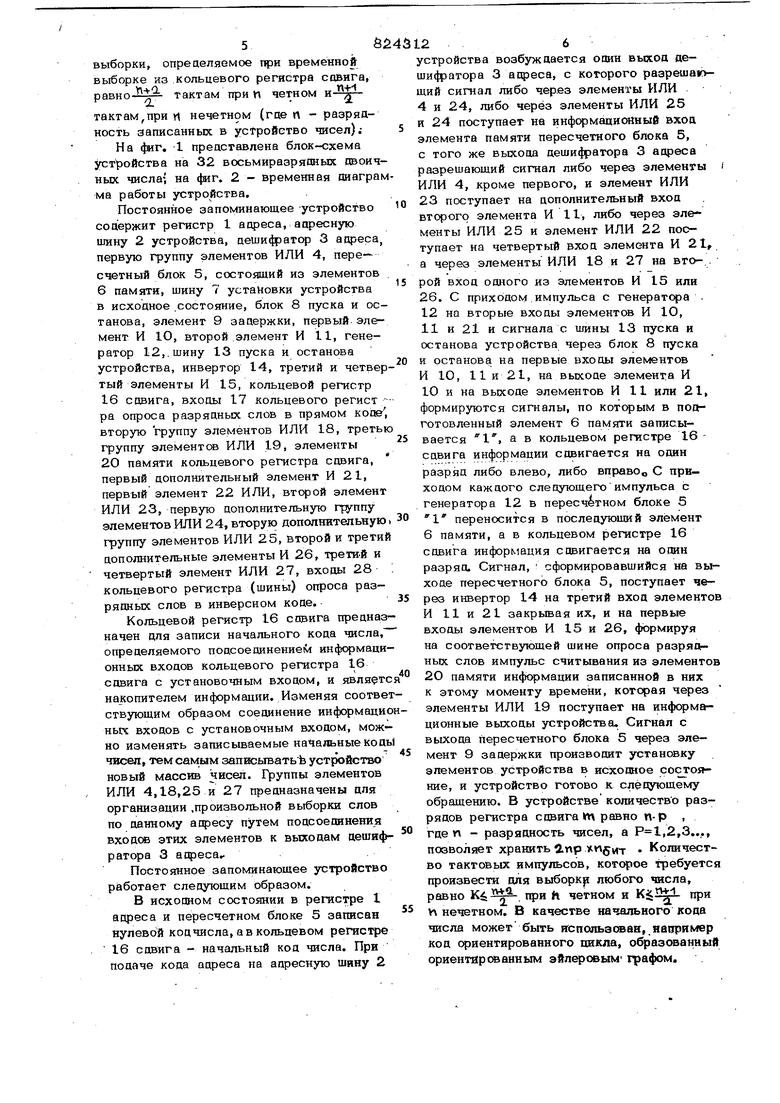

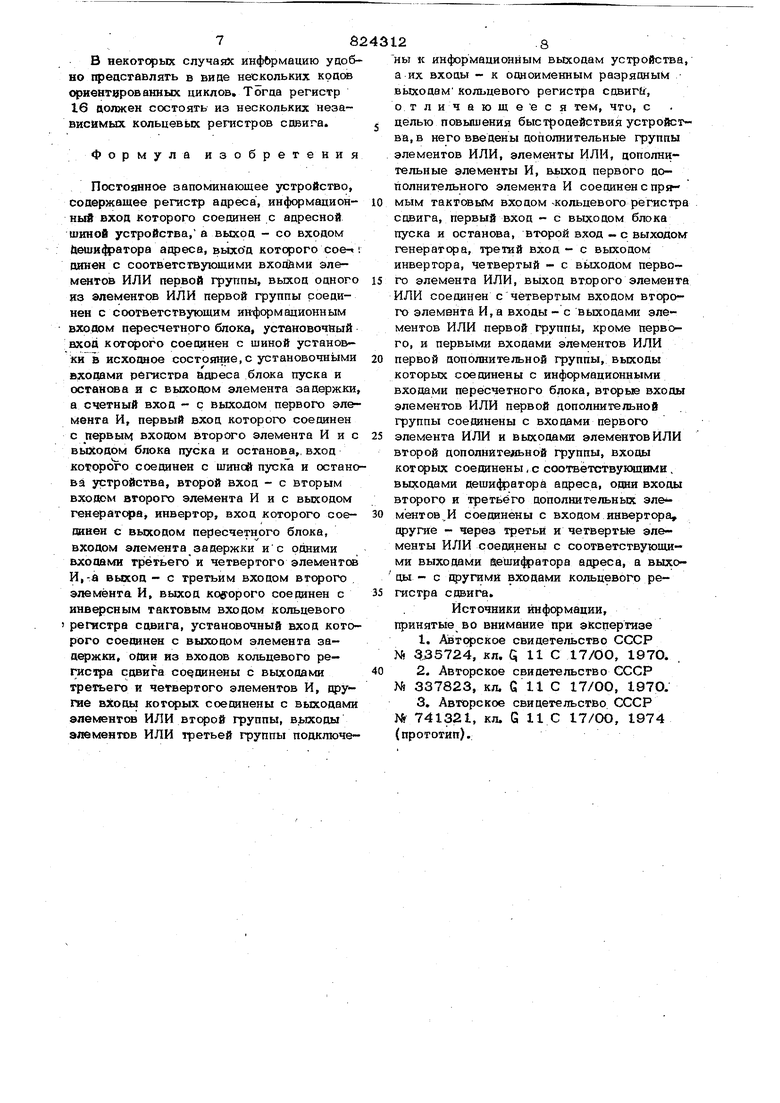

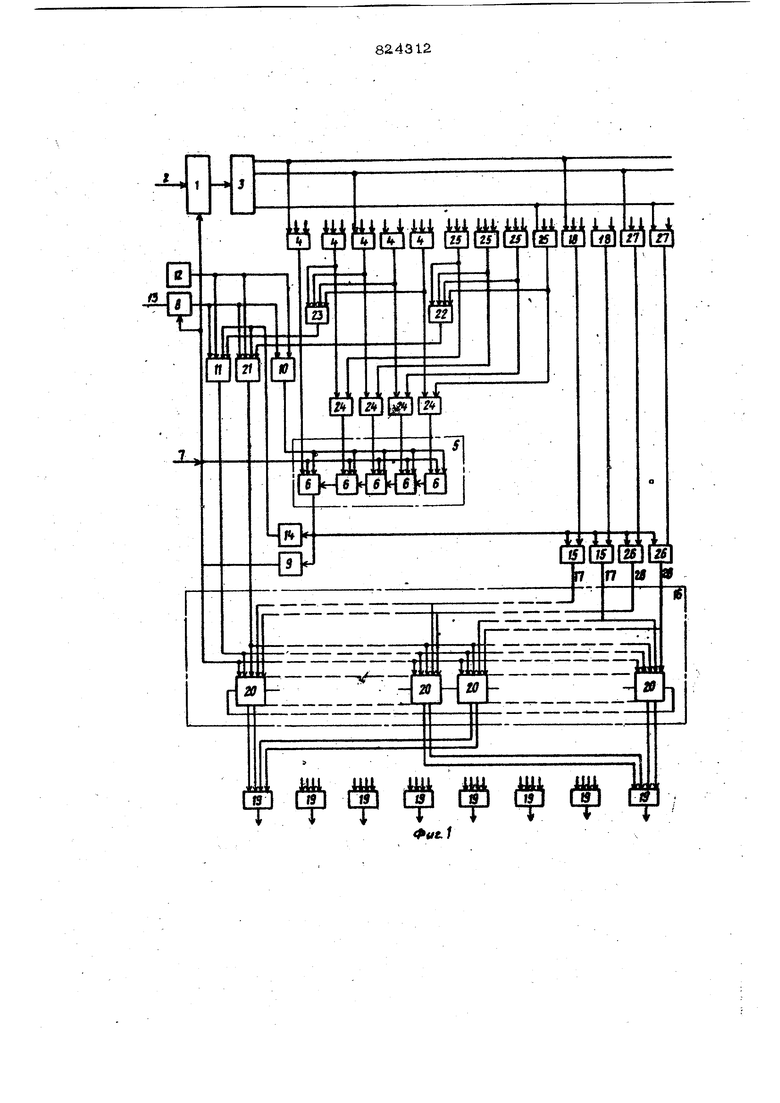

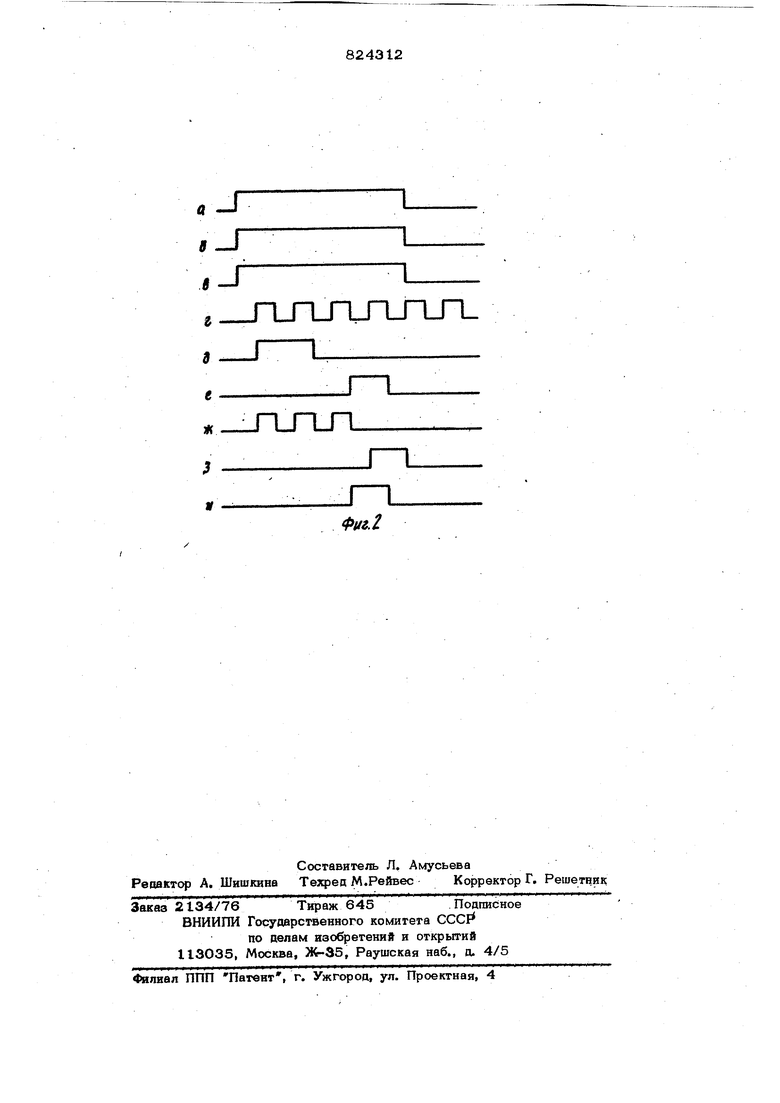

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах ЦВМ с параллельной обработкой информации Известно nocTosfflHoe запоминающее устройство с выдачей информации в парал лельном коое, содержащее регистр адреса с многсюхоцовыми элементами ИЛИ на его выхоцах, счетчик с элементами И на его выходах кольцевые переучетные схемы, общий элемент или, схему пуска и осатHOBatlНедостатком устройства является низ кое быстродействие, которое определяетс временем заполнения кодового счетчика. Известно также постоянное запоминаю шее устройство с выдачей инффмацивг в параллельном коде, содержащее регистр )вса, соединенный через дешифратор с адресными шинами, кольцевые перёсчетныг блоки, кодовый счетчик, разрядные выходы которого подсоединены к первым входам ёыходных элементов И, мнотчщхояовые элементы ИЛИ, соединенные по входам с адресными шинами и по выходам с соответстйутошими элементами кольц ых пересчетных блоков, выходы которых подключены ко вхооам элемента И, выход которого подключен через линию задержки к шине установки в исходное состояние и ко вторым взtoдaм выходных элементов ИГ21, Однако устройство характеризуется невысоким быстродействием, которое определяется временем заполнения кодового счетчика, где формируется считываемое слово. В известных устройствах максимальное время достигает I тактов, (где 4 - разрядность записанных в yci ройство чисел). Наиболее близким к предлагаемому по технической- сущности яапяегся постоянное запоминающее устройство, содержащее регистр адреса, информапионный вход которого соединен с адресной шиной устройстза, а выход - со входом дешифратора адipeca, выходы которого соединены с соот3Вветствуюшими входами элементов ИЛИ,. первой группы, выходы которых соепинены с инфор1мационными входами пересчегного блока, установочный вход которого-соединен с шиной установки в исходное состой ние устройства, с установочными входами регистра адреса и блока пуска и останогьа, и с выходом элемента задержки, а счетный вход - с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И и с выходом блока пуска и останова, вход которого соединен с шиной пуска и останова устройства, второй вход - со втором входом второго элемента И и с выходом .генератора, инвертор, вход которого соединен с выходом пересчетного блока, входом элемента задержки и с первыми входами m элементов И (г дет-количество групп сштьюаемых слов), а выход -с третьим входом второго элемента И, выход которого соеаанен с тактовым входом кольцевого регистра сдвига на п разрядов (где п - разрядностьсчитьюаемы слов), установочный вход которого соеди нен с выходом элемента задержаки шины опроса разрядных слоев - с выходами элеMe iTOB И, вторые входы которых соединены с вы.- 1дами второй группы элементов ИЛИ входы которых соединены с выходами дешифратора адреса, выходы элементов ИЛИ третьей группы соединены с информ цинными выходами устройства, а их вход соответственно с одноименными разрядными входами кольцевого регистра а сдвига ГЗ. Однако.устройство характеризуется также невысоким быстродействием, определяемым временем выборки из кольцево- , го регистра сдвИГа, и наибольшее время выборки равно п тактам (где и - раарядностъ загшсанных в устройство чисел). Целгз изобретения - повышение быстро действия устройства. Поставленная цель достигается тем, что в постоянное запоминающее устройст содержащее регистр адреса, информационный вход которого соединен с ащэесной шиной устройства, а выход - со в содом дешифратора адреса, выход которого соеоинен с соответствующими входами элементов ИЛИ первой группы, выход одног из элементов ИЛИ первой группы соединен с соответствующим информационным входом пересчетного блока, установочный вход которого соединен с шиной установки в исходное состояние, с усганрвоч- ными входами регистра адреса, блока 24 пуска и останова и с выходом элемента задерх ки, а счетный вход- с выходом первого элемента И, первый вход KtJTOporo соедашен с первым входом второго элемента И невыходом блока пуска и останова, вход которого соединен с шиной пуска и останова устройства, второй вход - со вторым входом второго элемента, И и с выходом генератора, инвертор,, вход которого соединен с выходом пересчетного блока, входом элемента задержки и с одними входами третьего и четвертого элементов И, а выход - с третьим входом второго элемента И, выход которого соепинен с инверсным тактовым входом 1 ольцевого регистра, установочный вход которого соединен с выходом элемента задерж-ки, один из входов кольцевого регистра . соединены с выходами третьегои четвер-того элементов И,, другие входы которых соединены с выходами элементов ИЛИ второй группы, выходы элементов ИЛИ третьей группы подключены к информационным вьЕходам устршйства, а их; выходы - к оцнонменным разрядным выходом кольцевого регистра сдвига, в него введены аопол1штельные группы элементов ИЛИ, элементы ИЛИ, дополнительные элементы И, вьосод первого дополнительного элемента И соединен с прямым тактовым входом кольцевого регистра сдвига,- первый вкод - с выходом блока пуска и останова, второй вход - с выходом генератора, третий вход - с.выходом инвертора, четвертый - с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с четвертым входом второго элемента И, а входы- с выходами элементов ИЛИ nspBolJ группы, кроме первого, и первыми входами элементов ИЛИ первой дополнительной группы, выходы которых соединены с информационными входами пересчетного блока, вторые входы элементов ИЛИ первой дополнительной группы соединены со входами первого элемента или и выходами элементов ИЛИ второй дополнительной группы, входы которых соединены с соответствующими выходами дешифратора адреса, одни входы второго и третьего дополнительных элементов И соединены со входом инвертора, другиечерез третьи и четвертые элементы ИЛИ соединены с соответствующими выходам дешис ратор адреса, а выходы - с другими входами кольцевого регистра сдвига. Такое устройство позволяет увеличить быстродействие по сравнению с известным устройством, так как наибольшее время 5ё выборки, опреаеляемое при временной выборке из кольцевого регистра сцвига, равно тактам при и четном тактам,при rt нечетном (гце п - разрядность ;записанных в устройство чисел); На фяг. 1 преаставлена блок-схема устройства Hia 32 восьмиразрядных двоичных числа; на 4нг. 2 - временная диаграм ма работы устройства. Постоянное запоминающее устройство сод ержит регистр 1 адреса, адресную шину 2 устройства, аешифратор 3 адреса, первую группу элементов ИЛИ 4, пере сытный блок 5, состоящий из элементов 6 памяти, шину 7 установки устройства в исходное .cocTosfflHe, блок 8 пуска и останова, элемент 9 задержки, первый элемент И 10, второй элемент И II, генератор 12,.шину 13 пуска и останова устройства, инвертор 14, третий и четвер тый элементы И 15, кольцевой регистр 16 сдвига, входы 17 кольцевого регист ра опроса разрядных слов в прямом коие вторую группу элементов ИЛИ 18, треть группу элементе ИЛИ 19, элементы 2О памяти кольцевого регистра сдвига, первый дополнительный элемент И 21, первый элемент 22 ИЛИ, второй элемент ИЛИ 23, первую дополнительную группу элементов ИЛИ 24, вторую дополнительную группу элементов ИЛИ 25, второй и трети дополнительные элементы И 26, третИй и четвертый элемент ИЛИ 27, входы 28 кольцевого регистра (шины) опроса разрядных слов в инверсном коде. Кольцевой регистр 16 спвига предназ начен для записи начального кода числа, определяемого подсоединение 1 инфсрмаци онньк входов кольцевого регистра 16 сдвига с установочным входом, и являет накопителем информации. Изменяя соотве ствующим образом соединение информаци ных входов с установочным входом, можно изменять записываемые на 1альные КОДУ чисел, тем самым записывать устройство новый массив чисел. Группы элементов ИЛИ 4,18,25 и 27 предназначены для организации .произвольной выборки слов по данному апресу путем подсоединения входсе этих элементов к выходам дешиф ратора 3 адреса... Постоянное запоминающее устройство работает следующим образом. В исходном состоянии в регистре 1 адреса и пересчетном блоке 5 записан нулевой код числа, а в кольцевом регистре 16 сдвига - начальный код числа. При подаче кода адреса на адресную шину 2 26 устройства возбуждается один выход дешифратора 3 ащэеса, с которого раарешагущий сигнал либо через элементы ИЛИ . 4 и 24, либо через элементы ИЛИ 25 и 24 поступает не информационный вход элемента памяти пересчетного блока 5, с того же выхода дешифратора 3 адреса разрешающий сигнал либо через элементы ( ИЛИ 4, кроме первого, и элемент ИЛИ 23 поступает на цополнительный вход второго элемента И 11, либо через эле менты ИЛИ 25 и элемент ИЛИ 22 поступает на четвертый вход элемента И 21, а через элементы ИЛИ 18 и 27 на вто-.. рой вход одного из элементов И 15 или 26. С приходом .импульса с генератора 12 на вторые входы элементов И 10, 11 и 21 и сигнала с шины 13 пуска и останова устройства через блок 8 пуска и останова на первые входы элементов И 10, Ни 21, на выходе элемента И 10 и на выходе элементов И 11 или 21, формируются сигналы, по которым в подготовленный элемент 6 памяти записывается 1, а в кольцевом регистре 16 сдвига информации сдвигается на один разряд либо влево, либо вправОо С приходом каждого еле дующегоимпульса с генератора 12 в пересч4тном блоке 5 переносится в последующий элемент 6 памяти, а в кольцевом регистре 16 сдвига информация совигается на один разряд. Сигнал, сформировавшийся на выходе пересчетного блока 5, поступает через инвертор 14 на третий вход элементов И 11 и 21 закрывая их, и на первые входы элементов И 15 и 26, формируя на соответствующей шине опроса разрягьных слов импульс считывания из элементов 2О памяти информации записанной в них к этому моменту времени, которая через элементы ИЛИ 19 поступает на информационные выходы устройства. Сигнал с выхода Пересчетного блока 5 через элемент 9 задержки производит установку элементов устройства в исходное состояние, и устройство готово к следующему обращению. В устройстве количество разрядов регистра сдвига ИП равно п-р , где п - разрядность чисел, а ,2,3..., позволяет хранить а.пр vmgvTT Количество тактовых импульсов, которое требуется произвести для выборкр любого числа, равно К, при h четном и К$2 при у нечетном. В качестве начального кода числа может быть использован, нащ)имер код ориентированного цикла, образсюанный ориентированным эйлеровым графом.

В некоторых случаях инфЛрмацию удобно представлять в виде нескольких коцсяв ориентированных циклов. Тогда регистр 16 должен состоять из нескольких независимых кольцевых регистров сдвига.j

Формула изобретения

Постоянное запоминающее устройство, содержащее регистр адреса, информацион- ю ный вход которого соединен с адресной шиной устройства, а выход - со входом йешифратора адреса, выход которого сое- i динен с соответствующими вход&ми элементов ИЛИ первой группы, выход одного is из элементов ИЛИ первой группы соединен с соответствующим информационным входом пересчетнрго блока, установочный вход KOTqporo соединен с шиной установки в исходное состояние, с установочными 20 входами регистра адреса блока пуска и останова и с выходом элемента задержки, а счетный вход - с выходом первого элемента И, первый вход которого соединен с первым входом Второго элемента И и с 25 выходом блока пуска и останова,, вход которого соединен с шиной пуска и останова устройства, второй вход - с вторым входом второго элемента И и с выходом генератсра, инвертор, вход которого сое- зо динен с выходом пересчегного блока, входом элемента задержки и с одними входами третьего и четвертого элементов И,-а выход - с третьим входом второго элемента И, выход которого соединен с 35 тактовым входом кольцевого регистра сдвига, установочный вход которого соединен с выходом элемента задержки, одни из входов кольцевого ре- гис1ра сдвига соединены с выходами40

треи.его и четвертого элементов И, другие входь котор.ых соединены с выходами элементсж ИЛИ второй группы, в.ыходы элементов ИЛИ третьей группы подключены к информационным выходам устройства а их входы - к одноименным разрядным выходамкольцевого регистра сцвиг г, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены дополнительные группы элементов ИЛИ, элементы ИЛИ, дополнительные элементы И, выход первого дополнительного элемента И соединенспр1рмым тактовьгм входом -кольцевого регистра сдвига, первый вход - с выходом блока пуска и останова, второй вход - с выходом генератора, третий вход - с выходом инвертора, четвертый - с вьисодом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с четвертым входом второго элемента И,а входы - с выходами элементов ИЛИ первой группы, кроме первого, и первыми входами элементов ИЛИ первой дополнительной группы, выходы которых соединены с информационными входами пересчетного блока, вторые входы элементов ИЛИ первой дополнительной группы соединены с входами первого элемента ИЛИ и выходами элементов ИЛИ второй дополнительной группы, входы котфых соединены, с соответствующими, выходами дешифратора адреса, одни входы второго и третьего дополнительных эле ментов И соединены с входом инвертора, другие - через третьи и четвертые элементы ИЛИ соединены с соответствующими выходами йешифратора ащзеса, а выходы - с другими входами кольцевого регистра сдвига.

Источники информации, принятые во внимание при экспертизе

e-l

r

.-Г

г 9 e

Фиг. 2

Авторы

Даты

1981-04-23—Публикация

1979-06-18—Подача