технической сущности является устройство, содержащее блок управления, ком1мутатор переменных логической функции, выход которого подключен ко входу индикатора тестовых наборов, и коммутатор инверсных переменных логической функции, управляющий вход которого подключен к выходу блока управления. Это устройство характеризуется большим объемом логических преобразований, связанных с полученнем дизъюнктивной нормальной формы инверсной логической функции и с достроеннем дешифрирующего ключа, а также большим числом ручных операций по вводу информации о проверяемой схеме. Каждая переменная в устройство вводится четыре раза: два раза - при получении наборов разрыва и два раза - при получении наборов шунтирования. Без дешифрирующего ключа невоз-. можна диагностика комбинационных схем.

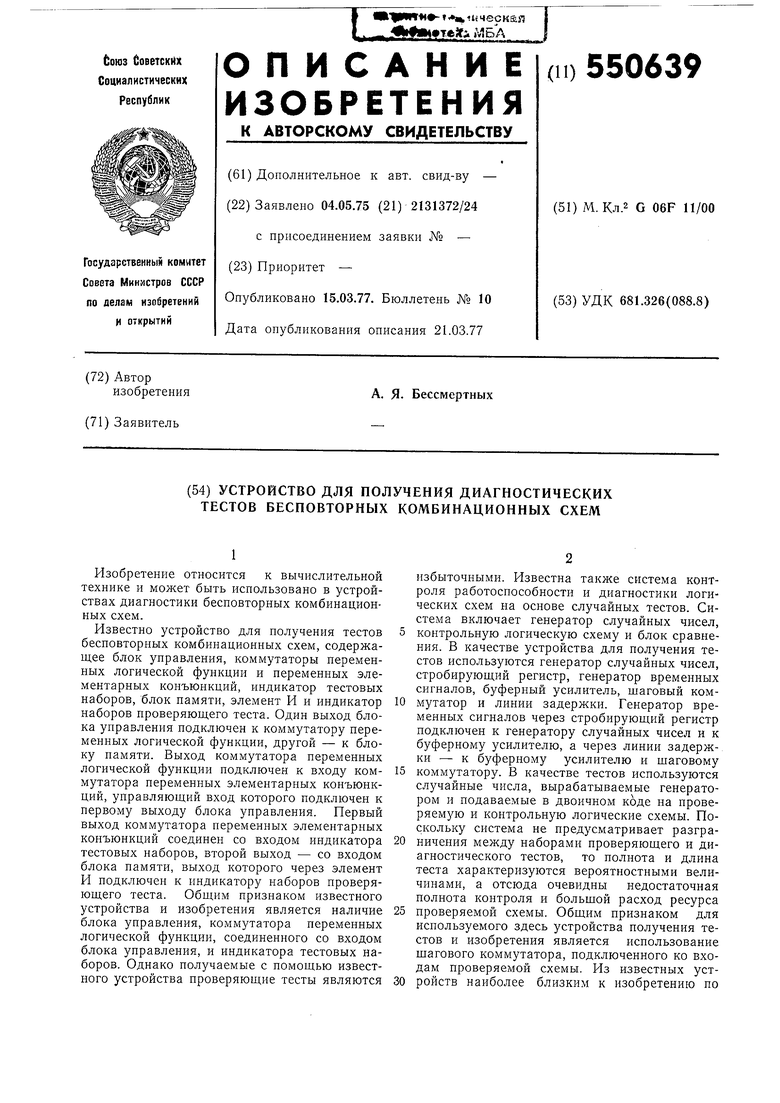

Целью изобретения является повышение быстродействия путем сокращения логических операций и операций ввода данных. В описываемом устройстве это достигается тем, что в него введены коммутаторы столбцов, строк, переменных разрыва, неременных шунтирования и ключи, причем входы коммутаторов строк и переменных логической функции подключены к соответствующим выходам коммутатора столбцов, управляющие входы которого через коммутатор переменных шунтирования и через коммутатор переменных разрыва соединены с выходом блока управления, выходы коммутатора строк через коммутатор переменных щунтирования соединены со входами соответствующих ключей, выходы и управляющие входы которых соединены соответственно со входами индикатора тестовых наборов и с выходами коммутатора инверсных переменных логической функции.

Сокращение логических преобразований достигается путем исключения математических операций, связанных с получением дизъюнктивной нормальной формы инверсной логической функции. Это в свою очередь позволяет более чем вдвое сократить число операций по вводу информации о диагностируемой схеме. В устройстве образован матричный запоминающий блок объединением общими элементами коммутаторов столбцов, строк, переменных логической функции н инверсных переменных логической функции. Образование общего матричного запоминающего блока позволяет осуществлять ввод информации о диагностируемой схеме в виде дизъюнктивной формы, а наличие коммутатора столбцов - выделять последовательные элементы (пути прохождения сигнала). Коммутатор строк совместно с ключами автоматически при этом выделяет параллельные элементы (пути прохождения сигнала). Поскольку ключи управляются выходными цепями коммутатора инверсных переменных логической функции, то информация о параллельных элементах в индикатор тестовых наборов поступает со знаком состояния, противоположным состоянию их в логической

функции. Коммутаторы же переменных разрыва н шунтирования позволяют осуществлять привязку получаемых тестовых наборов к контролируемым элементам (путем прохождения сигналов).

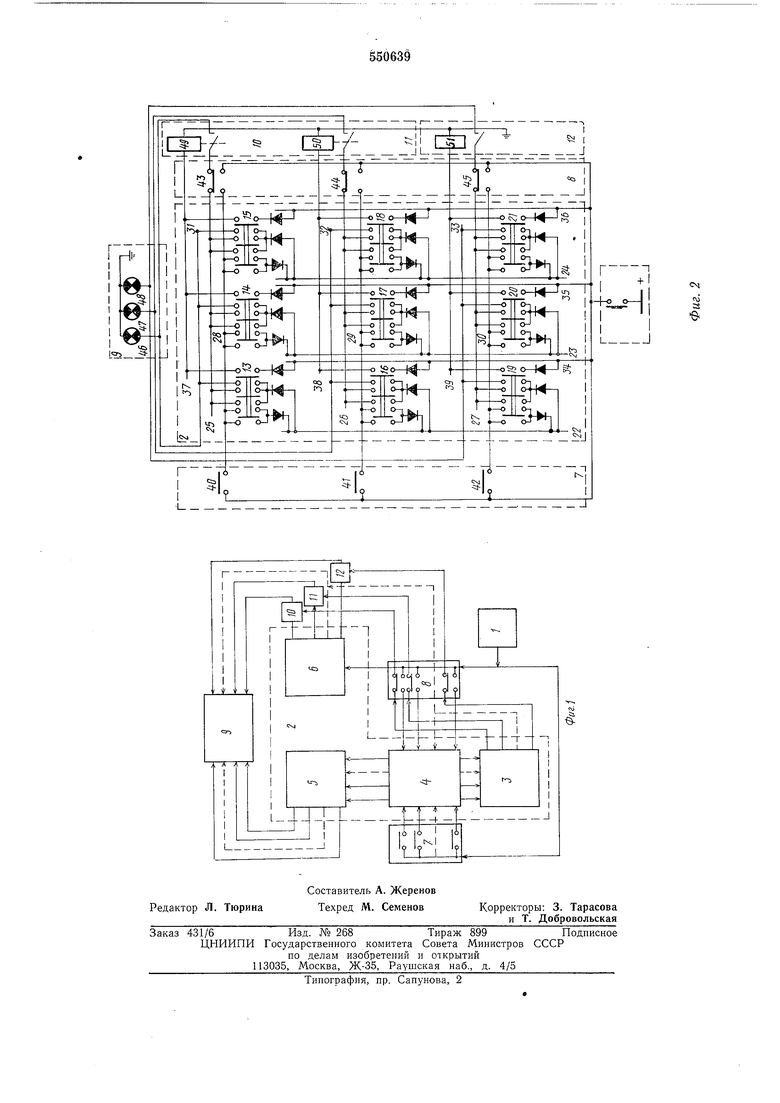

На фиг. 1 изображена структурная схема описываемого устройства; на фиг. 2 - принципиальная электрическая схема в одном из возможных вариантов технической реализации.

Устройство содержит блок 1 управления, матричный запоминающий блок 2, состоящий из коммутатора 3 строк, коммутатора 4 столбцов, коммутатора 5 переменных логической функции и коммутатора 6 инверсных переменных логнческой функции, коммутатор 7 переменных разрыва, коммутатор 8 переменных щунтирования, индикатор 9 тестовых наборов и ключи 10, 11 и 12. Блок 1 управления представляет собой устройство, осуществляющее во включенном состоянии подачу напряжения источника питания па подключенные к его выходу устройства. Коммутатор 3 строк выполпен матричным, коммутирующие элементы которого, объединенные вертикальными шинами, соответствуют переменным в элементарных конъюнкциях. Коммутирующие элементы имеют три устойчивых состояния: два - включенных и одно нейтральное. В любом из включенных состояний вертикальные шины подключаются к соответствующим входным шинам. Коммутатор 4 столбцов выполнен также матричным и с таким же назначением и положением коммутирующих элементов. Вертикальные шины подключаются к соответствующим горизонтальным шпнам в любом из включенных положений коммутирующих элементов. В коммутаторе 5 переменных логической функции, выполненном также матричным, горизонтальные шины подключаются к соответствующим вертикальным шинам в положенип тех же коммутирующих элементов, соответствующем наличию переменной без инверсии, а в коммутаторе 6 горизонтальные шины подключаются к вертикальным в положении коммутирующих элементов, соответствующем переменной с инверсией. Коммутаторы 3, 4, 5 и 6 имеют общие коммутирующие элементы и объединены в единый запоминающий блок матричного типа. Коммутатор 7 переменных разрыва представляет собой набор коммутирующих элементов, соответствующих переменным логнческой функции, во включенном состоянии которых вход коммутатора подключается к соответствующему выходу. Коммутатор 8 переменных шунтирования выполнен в виде коммутирующих элементов, например переключателей, в выключенном состоянии которых горизонтальные шины коммутатора подключены к управляемым входам ключей 10, 11 п 12, а во включенном состоянии вход коммутатора подключается к соответствующим выходам. Индикатор 9 тестовых наборов представляет собой набор индицирующих элементов, состояние которых соответствует перемен11ЫМ в наборах диагностического теста. Ключи 10, 11 и 12 в исходном состоянии - открыты. При подаче питания па управляемые входы ключи закрываются.

Выход блока 1 управления иодключен к входам коммутатора 7 переменных разрыва, коммутатора 8 переменных шунтирования и коммутатора 6 инверсных неременных логической функции. Горизонтальные шины коммутатора

3строк через одноименные коммутируюш,ие элементы коммутатора переменных шунтирования при их выключенном состоянии подключены к управляюш,им входам электронных ключей, а горизонтальные шины коммутатора

4столбцов подключены к выходам коммутаторов 7 и 8. Входы индикатора 9 тестовых наборов подключены к горизонтальным шинам коммутатора 5 переменных логической функции, а через электронные ключи 10, И и 12- горизонтальным шинам коммутатора 6 инверсных переменных логической функции.

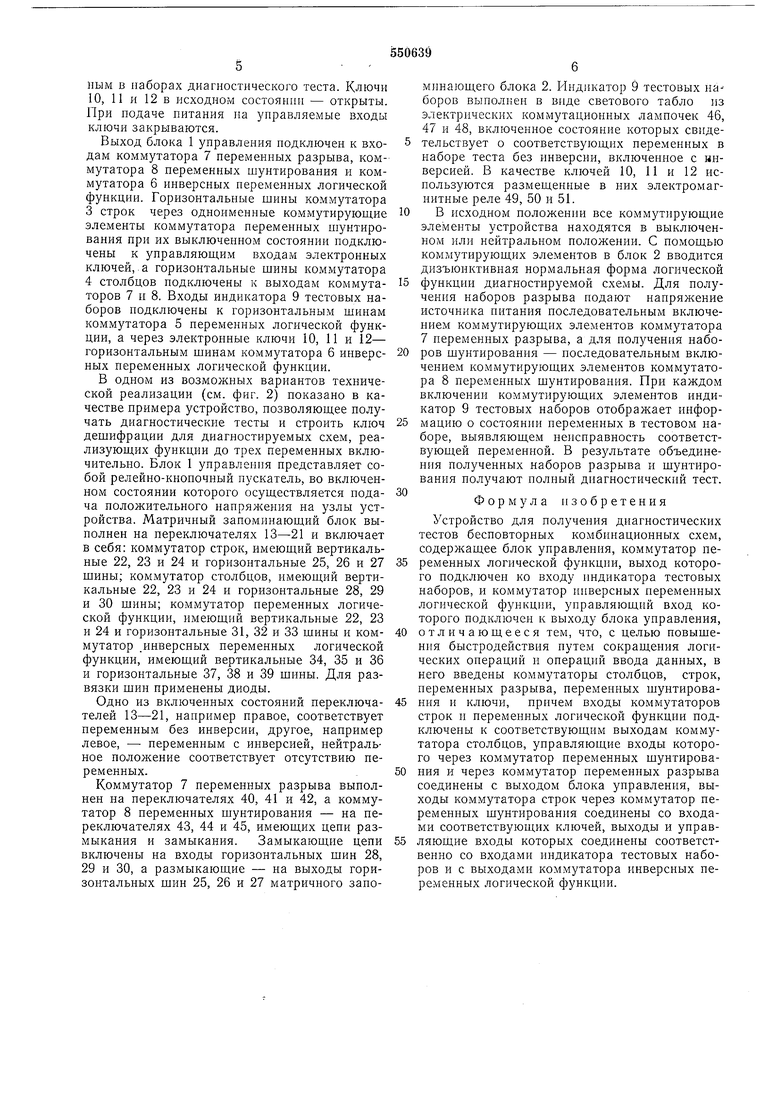

В одном из возможных вариантов технической реализации (см. фиг. 2) показано в качестве примера устройство, позволяющее получать диагностические тесты и строить ключ дешифрации для диагностируемых схем, реализующих функции до трех переменных включительно. Блок 1 управлення представляет собой релейно-кнопочный пускатель, во включенном состоянии которого осуществляется подача положительного напряжения на узлы устройства. Матричный запоминающий блок выполнен на переключателях 13-21 и включает в себя: коммутатор строк, имеющий вертикальные 22, 23 и 24 и горизонтальные 25, 26 и 27 шины; коммутатор столбцов, имеющий вертикальные 22, 23 и 24 н горизонтальные 28, 29 и 30 шины; коммутатор переменных логической функции, имеющий вертикальные 22, 23 и 24 и горизонтальные 31, 32 и 33 шины и коммутатор .инверсных переменных логической функции, имеющий вертикальные 34, 35 и 36 и горизонтальные 37, 38 и 39 шины. Для развязки шин применены диоды.

Одно из включенных состояний переключателей 13-21, например правое, соответствует переменным без инверсии, другое, например левое, - переменным с инверсией, нейтральное положение соответствует отсутствию переменных.

Коммутатор 7 переменных разрыва выполнен на переключателях 40, 41 и 42, а коммутатор 8 переменных шунтирования - на переключателях 43, 44 и 45, имеющих цепи размыкания и замыкания. Замыкающие цепи включены на входы горизонтальных шин 28, 29 и 30, а размыкающие - на выходы горизонтальных шин 25, 26 и 27 матричного запоминающего блока 2. Индикатор 9 тестовых наборов выполнен в виде светового табло из электрических коммутационных лампочек 46, 47 и 48, включенное состояние которых свидетельствует о соответствующих переменных в наборе теста без инверсии, включенное с инверсией. В качестве ключей 10, И и 12 используются размещенные в них электромагнитные реле 49, 50 и 51.

В исходном положении все коммутирующие элементы устройства находятся в выключенном или нейтральном положении. С помощью коммутирующих элементов в блок 2 вводится дизъюнктивная нормальная форма логической

функции диагностируемой схемы. Для получения наборов разрыва подают напряжение источника питания последовательным включением коммутирующих элементов коммутатора 7 переменных разрыва, а для полз чения наборов шунтирования - последовательным включением коммутирующих элементов коммутатора 8 переменных шунтирования. При каждом включении коммутирующих элементов индикатор 9 тестовых наборов отображает информацию о состоянии переменных в тестовом наборе, выявляющем неисправность соответствующей переменной. В результате объединения полученных наборов разрыва и шунтирования получают полный диагностический тест.

ли

Формула изобретения

Устройство для получения диагностических тестов бесповторных комбинационных схем, содержащее блок управления, коммутатор переменных логической функции, выход которого подключен ко входу индикатора тестовых наборов, и коммутатор инверсных переменных логической функции, управляющий вход которого подключен к выходу блока управления,

отличающееся тем, что, с целью повышения быстродействия путем сокращения логических операций п операций ввода данных, в него введены коммутаторы столбцов, строк, переменных разрыва, переменных шунтирования и ключи, причем входы коммутаторов строк и переменных логической функции подключены к соответствующим выходам коммутатора столбцов, управляющие входы которого через коммутатор переменных шунтирования и через коммутатор переменных разрыва соединены с выходом блока управления, выходы коммутатора строк через коммутатор переменных шунтирования соединены со входами соответствующих ключей, выходы и управляющие входы которых соединены соответственно со входами индикатора тестовых наборов п с выходами коммутатора инверсных переменных логической функции.

LOSSt.

+ 1

о cU

-Ь°

II

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска неисправностей бесповоротных комбинационных схем | 1974 |

|

SU526834A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1976 |

|

SU748420A1 |

| Устройство для получения диагностических тестов логических блоков | 1977 |

|

SU736103A1 |

| Устройство для формирования тестов дискретных автоматов | 1975 |

|

SU642711A1 |

| Устройство для получения тестов бесповторных комбинационных схем | 1975 |

|

SU570897A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| Устройство для формирования тестов бесповоротных комбинационных схем | 1974 |

|

SU607220A1 |

| Устройство для получения минимальных диагностических тестов бесповторных комбинационных схем | 1973 |

|

SU458830A1 |

| Устройство для получения тестов бесповоротных комбинационных схем | 1974 |

|

SU526895A1 |

| Устройство для диагностирования бесповторных комбинационных схем | 1976 |

|

SU684556A1 |

Авторы

Даты

1977-03-15—Публикация

1975-05-04—Подача