исправной схемы и фиксацию наборов, на которых эти значения различаются. .

Поставленная цель достигается тем, что устройство содержит последовательно соединенные дешифратор, четвертый ког/гмутатор и шифратор, а также элементы И, первые входы которых подключены к соответствуюим выходам второго и третьего коммутаторов, вторые входы - к первым выходам первого коммутатора, а выходы - ко вторым входам соответствуклдих ключевых элементов, выход каждого из которых соединен с выходом одного из других ключевых элементов, и с одним из входов дешифратора, вторые выходы первого коммутатора подключены ко входам второго и третьего коммутаторов, а третий йыход - ко второ у входу четвертоi o коммутатора, соединенного вторым ЁЙЙсодом с первым входом блока сравнения и памяти с индикацией, второй вход которого подключен к четвёртому выходу первого коммутатора.

В устройстве реализуется алгоритм построения наборов полного диагностического теста ,комбинационных- схем, основанный на построении для каждой конъюнкции прямой и инверсной контрольной или эквивалентной нормальной формы функций ПКНФ и ИКНФ, провёряю1дей совокупности наборов разрыва и шунтирования. , . :

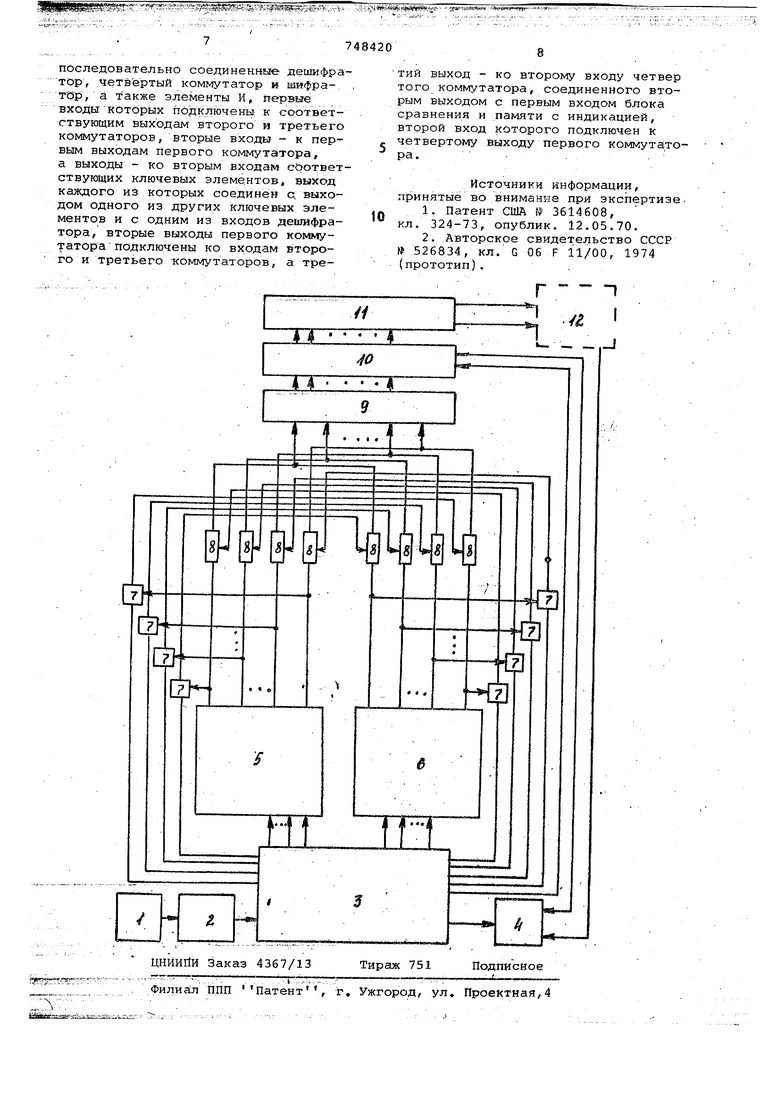

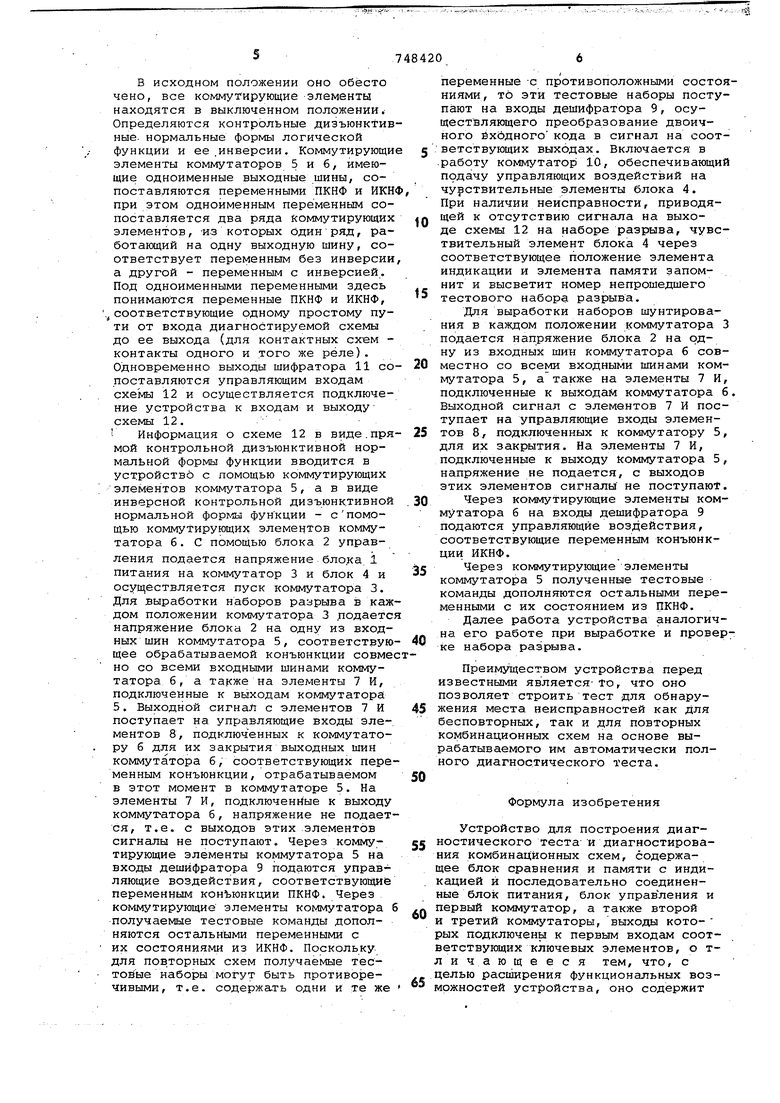

Блок-схема устройства представлена на чертеже.

Она содержит блок 1 питания, блок 2 управления, первый коммутатор 3, блок 4 сравнения памяти с индикацией второй и третий коммутаторы 5 и 6, элементы 7 И, ключевые элементы 8, дешифратор 9, четвертый коммутатор 10, шифратор 11 и диагностируемую схему 12.

Блок 2 управления служит для подачи напряжения блока 1 на вход коммутатора 3, на блок 4 для фиксации непрошедших наборов и для управления работой коммутатора 3.

Коммутатор 3 предназначен для подачи Напряжения на шины коммутаторов 5 и б и на входы элементов 7 И. В каящоЫ пбложетнйй комК1утатора 3™ йЬдаетсй Питание на одну из входных шин коммутатора 5 (6) совместно со всем входными шинами коммутатора б (5). Одновременно с подачей питания на любую из шин коммутатора 5 (б) подается питание на входы всех элементов .7 И, стоящих в выходных цепях коммутатора 5 (6). Питание на первый коммутатор 3 подается Через нулевое (исходное) положение коммутатора 10.

Блок 4 содержит чувствительные элементый № срМнШйй-1ыходныхсй:гналов схемы 12 и коммутатора 10,

а также содержитнаборы элементов памяти и индицирующих элементов.

Элементы памяти и индицирующие элементы разбиты на две группы. Одна группа фиксирует непрошедшие.наборы разрыва, другая - непрошедшие наборы шунтирования. При тестовой кманде. Выявляющей разрыв элементов,, и при отсутствии сигнала с схемы 12 и при тестовой команде, выявляющей шунтирование элементов, и при наличии сигнала с выхода схемы 12 срабатывает элемент памяти блока 4 и индицирующий элемент.

Коммутаторы 5 и б предназначены для коммутации переменных прямой и инверсной контрольных нормальных форм функции соответственно.

Коммутаторы 5 и б выполнены матричными. В матричных коммутаторах используется принцип двухпроводной логики. Коммутирующие элементы их, например однополюсные переключатели соответствуют переменным логической функции и её инверсии. Все коммутирующие элементы, объединенные с одной входной шиной, соответствуют переменным одной конъюнкции ПКНФ или ИКНФ. Коммутаторы 5 и б имеют одну группу выходных шин.

Элементы 7 И представляют собой многополюсники с двумя входами и одним выходом (выполнены по стандартному типу). На один вход элемента 7 И подается напряжение с коммутатора 3, а на другой вход - с одного из выходов коммутаторов 5 или б.

Элементы 8, стоящие в выходных цепях одного из коммутаторов 5 и б, управляющими входами подключены к выходам соответствующих элементов 7 И, подключенных к выходам другого коммутатора 5 или б,а-их выходы подключены к входам дешифратора 9. Дешифратор 9 выполнен, например матричным и служит для преобразования двоичного кода на входе в терминах состояний переменных ПКНФ и ИКНФ в сигналы, соответствующие состоянию входных переменных схемы.

Коммутатор 10 служит для управления работой чувствительных ,э.ле-. ментов и с переходом на единичное положение разрывает цепь питания коммутатора 3, который остается в отключенном положении до прихода коммутатора 10 в положение О, а совместно с шифратором 11, выполненным, например, матричным, служит для последовательного преобразования сигналов на выходе дешифртора 9 в двоичные коды, подаваемые в виде тестовых наборов на входы схемы 12,(вьщеляет все физически реализуемые наборы из каждого выходного набора дешифратора 9).

Устройство работает следующим образом.

В исходном положении оно обёсто чено, все коммутирующие элементы находятся в выключенном положении. Определяются контрольные дизъюнктивные, нормальные формы логической функции и ее.инверсии. Коммутирующие элементы коммутаторов 5 и б, имеющие одноименные выходные шины, сопоставляются переменными ПКНФ и ИКНФ, при этом одноименным переменным сопоставляется два ряда коммутирующих элементов, -и-з которых одинряд, работающий на одну выходную шину, соответствует переменным без инверсии, а другой - переменным с инверсией. Под одноименными переменными здесь понимаются переменные ПКНФ и ИКНФ, соответствующие одному простому пути от входа диагностируемой схемы до ее выхода (для контактных схем контакты одного и того же реле). Одновременно выходы шифратора 11 сопоставляются управляющим входам схемы 12 и осуществляется подключение устройства к входам и выходу схемы 12.

Информация о схеме 12 в виде.прямой контрольной дизъюнктивной нормальной формы функции вводится в устройство с помощью коммутирующих элементов коммутатора 5, а в виде инверсной контрольной дизъюнктивной . нормальной формы функции - спомощью коммутирующих элементов коммутатора 6. С помощью блока 2 управления подается напряжение бло;ка i питания на коммутатор 3 и блок 4 и осуществляется пуск коммутатора 3. Для выработки наборов разрыва в каждом положении коммутатора 3 подается напряжение блока 2 на одну из входных шин коммутатора 5, соответствующее обрабатываемой конъюнкции совмест но со всеми входными шинами коммутатора 6, а также на элементы 7 И, подключенные к выходам коммутатора 5. Выходной сигнал с элементов 7 И поступает на управляющие входы эле-, ментов 8, подключенных к коммутатору б для их закрытия выходных шин KoiviMyTaTopa б, соответствующих переменным конъюнкции, отрабатываемом в этот момент в коммутаторе 5. На элементы 7 И, подключенные к выходу коммутатора 6, напряжение не подается, т.е. с выходов этих элементов сигналы не поступают. Через коммутирующие элементы коммутатора 5 на входы дешифратора 9 подаются управляющие воздействия, соответствующие переменным конъюнкции ПКНФ. Через коммутирующие элементы коммутатора 6 получаемые тестовые команды дополняются остальными переменными с их состояниями из ИКНФ. Поскольку для пов.торных схем получаемые тестовые наборы могут быть противоречивыми, т.е. содержать одни и те же

переменные -с противоположными состояниями, то эти тестовые наборы поступают на входы дешифратора 9, осуществляющего преобразование двоичного ёходного кода в сигнал на соответствующих выходах. Включается в .работу коммутатор 10, обеспечивающий подачу управляющих воздействий на чувствительные элементы блока 4. При наличии неисправности, приводящей к отсутствию сигнала на выхоoде схемы 12 на наборе разрыва, чувствительный элемент блока 4 через соответствующее положение элемента индикации и элемента памяти запомнит и высветит номер непрошедшего

5 тестового набора разрыва.

Для выработки наборов шунтирования в каждом положении коммутатора 3 подается напряжение блока 2 на одну из входных шин коммутатора б сов0местно со всеми входными шинами коммутатора 5, а также на элементы 7 И, подключенные к выходам коммутатора б. Выходной сигнал с элементов 7 И поступает на управляющие входы элемен5тов 8, подключенных к коммутатору 5, для их закрытия. На элементы 7 И, подключенные к выходу коммутатора 5, напряжение не подается, с выходов этих элементов сигналы не поступают.

Через коммутирующие элементы ком0мутатора б на входы дешифратора 9 подаются управляющие воздействия, соответствующие переменным конъюнкции ИКНФ.

Через коммутирующие элементы

5 коммутатора 5 полученные тестовые команды дополняются остальными переменными с их состоянием из ПКНФ.

Далее работа устройства аналогична его работе при выработке и провер0ке набора разрыва.

Преимуществом устройства перед известными является-то, что оно позволяет строить тест для обнару5жения места неисправностей как для бесповторных, так и для повторных комбинационных схем на основе вырабатываемого им автоматически полного диагностического теста.

0

Формула изобретения

Устройство для построения диагностического теста и диагностирова55ния комбинационных схем, содержащее блок сравнения и памяти с индикацией и последовательно соединенные блок питания, блок управления и первый коммутатор, а также второй

60 и третий коммутаторы, выходы которых подключены к первым входам соответствующих ключевых элементов, о тличающееся тем, что, с целью расширения функциональных воз65можностей устройства, оно содержит

последовательно соединенные дешифратОр, четвёртый коммутатор и шифра-. TtSp, а также элементы И, первые входыКоторых подключены; к соответствующим выходам второго и третьего коммутаторов, вторые входы - к первым выходам первого коммутатора, а выходы - ко вторым входам соответствующих ключевых элементов, выход каждого из которых соединен сз, выходом одного из других ключевых элементов и с одним из входов дешифратора, вторые выходы первого коммутатора подключены ко входам второго и третьего -коммутаторов, а тре7484208

тий выход - ко второму входу четвер того коммутатора, соединенного вторым выходом с первым входом блока сравнения и памяти с индикацией, второй вход которого подключен к четвертому выходу первого коммутатора.

Источники информации, принятые во внимание при экспертизе1. Патент США № 3614608, кл. 324-73, опублик. 12.05.70.

2. Авторское свидетельство СССР № 526834, кл. G 06 F 11/00, 1974 (прототип). .

-,

/г

-te

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| Устройство для поиска неисправностей бесповоротных комбинационных схем | 1974 |

|

SU526834A1 |

| Устройство для получения тестов бесповторных комбинационных схем | 1975 |

|

SU570897A1 |

| Устройство для формирования тестов дискретных автоматов | 1975 |

|

SU642711A1 |

| "Устройство для формирования тес-TOB КОМбиНАциОННыХ лОгичЕСКиХ блО-KOB | 1979 |

|

SU836635A1 |

| Устройство для получения тестов бесповоротных комбинационных схем | 1974 |

|

SU526895A1 |

| Устройство для получения диагностических тестов логических блоков | 1977 |

|

SU736103A1 |

| Устройство для формирования тестов бесповоротных комбинационных схем | 1974 |

|

SU607220A1 |

| Устройство для получения диагностических тестов бесповторных комбинационных схем | 1975 |

|

SU550639A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

Авторы

Даты

1980-07-15—Публикация

1976-05-03—Подача