1

Изобретение относится к адаптивным устройствам автоматического регулирования и служит для определения корреляционной функции .непрерывного случайного сигнала, заданного дискретой последовательностью со случайной частотой следования.

Процедура адаптации коррелятора заключается в получении вполне определенного набора параметров его по мере поступления входного сигнала. По окончании процедуры адаптации импульсная функция коррелятора будет описывать корреляционную функцию сигнала с минимальной средпеквадратической погрешностью.

Известные корреляторы 1 не обеспечивают возможности измерения в условиях априорной неопределенности корреляционной функции непрерывного случайного сигнала, заданного дискретной последовательностью импульсов со случайной частотой следования из-за отсутстВИЯ элементов адаптации и синхронизации, пО: пытка их применения для решения задачи ведет к недопустимым погрешностям.

Известно адаптивное устройство 2, содержащее блок вычитания, блок синхронизации, вход которого соединен со входом блока линейных фильтров, вход которого является входом устройства, а выходы блока линейных фильтров подключены соответственно к первой группе входов первого блока умножения,

выходы которого через соответствуюш,ие усилители с переменным коэффициентом и масштабные блоки соединены с первой группой входов второго блока умнол ения, вторая группа входов которого подключена к соответствуюш,им выходам блока линейных фильтров, выходы второго блока умножения соединепы с соответствуюш,ими входами сумматора, вторая группа входов первого блока умножения подключена к выходу блока вычитания.

Такое устройство непригодно для онределения корреляционной функции сигнала, заданного дискретной последовательностью со случайной частотой следования импульсов из-за отсутствия синхронизации между временем ирихода импульса и моментом выработки сигнала ошибки на корректировку адаптируемых параметров коррелятора.

Целью изобретения является расширение функциональных возможностей коррелятора, т. е. получение оценки корреляционной функции непрерывного случайного сигнала, заданного случайной дискретной последовательностью импульсов.

Для этого в предлагаемое устройство дополнительно введены три запоминаюш,ие ячейки, входы первой и второй запоминаюш,ей ячейки подключеиы к выходу сумматора, а выходы - к. первому входу блока вычитания, второй вход которого соединен с выходом третьей запоминающей ячейки, вход которой соединен со входом устройства, управляющие входы запоминающих ячеек подключены к соответствующим выходам блока обнаружении и синхронизации.

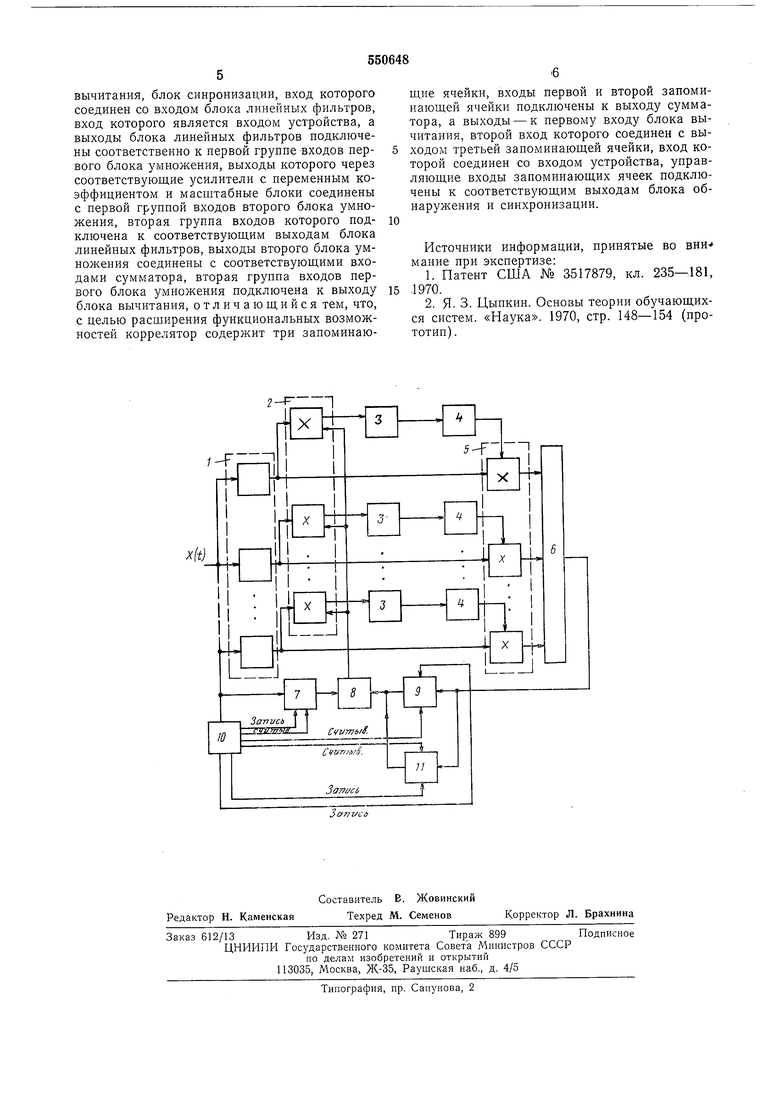

На чертеже изображена блок-схема предлагаемого коррелятора.

Он состоит из блока линейных фильтров 1, первого блока умножения 2, усилителей J с переменным коэффициентом усиления, масштабных блоков 4, второго блока умножения 5, сумматора 6, запоминающей ячейки 7, блока вычитания 8, запоминающей ячейки 9, блока 10 синхронизации, запоминающей ячейки И.

Блок линейных фильтров состоит из т (где т - число фильтров, определяющее точность восстановления корреляционной функции сигнала) параллельных линейных фильтров, выходы которых связаны со входами блоков умножения 2 и 5. Отдельный блок 2 (о) представляет собой сочетание усилителей постоянного тока и квадраторов, с помощью которых перемножение двух величин осуществляется по известной схеме: квадрат суммы двух величин минут квадрат разности между ними. Вторые входы блока связаны с выходами блока вычитания 8. Выходы блока 2 связаны со входами усилителей с переменным коэффициентом усиления 3, представляющим соОои набор усилителей постоянного тока, коэффициент передачи которых изменяется за счет варьирования сопротивлением в цепи обратной связи усилителя.

Выходы блока 6 соединены со входами масштабного блока 4, состоящего из наоора т параллельных элементов аналоговой долговременной памяти. Со входами блока умножения 5 связаны масштабный блок 4 и блок фильтров 1. Выходы блока 5 присоединены к сумматору 6. Выход сумматора b связан со входами запоминающих ячеек У и 11, выходы которых в свою очередь присоединены к одному из входов блока вычитания 8. Между другим входом блока вычитания и выходом устройства включена запоминающая ячейка 7. Дополнительно ко входу устройства подключен блок синхронизации 10, выходы которого связаны с управляющими входами запоминающих ячеек 7, 9 и 11. Блок обнаружения синхронизации представляет собой сочетание порогового устройства на базе триггера Шмидта, времязадающих одновибраторов, управляемого коммутатора на базе триггера и вентилей.

Исходный сигнал с вполне определенными, но неизвестными параметрами, заданный дискретной последовательностью имнульсов, поступает одновременно на входы блока линейных фильтров 1, запоминающей ячейки 7 и блока сихронизации 10. Последний на каждый входной импульс вырабатывает импульсы управления, поступающие на ячейки 7, 9, 11. Импульсы управления на каждую из запоминающих ячеек поступают по двум управляющим линиям: линии команды на запись и линии команды на считывание.

С началом входного импульса блок 10 вырабатывает управляющий импульс на запись, поступающий на запоминающие ячейки 7 и 9. Снустя определенное время, определяемое быстродействием схемы запоминания, блок 10 вырабатывает управляющий импульс на считывание, ноступающий на схемы ячейки 7 и И. С приходом нового импульса процедура повторяется, за исключением того, что теперь импульс на запись поступает на ячейку 11, а

импульс на считывание идет на ячейку 9. Таким образом, осуществляется черезпериодное управление ячейками 9 и И.

С приходом очередного импульса на вход коррелятора его значение, запомненное ячейкой 7, по сигналу с блока обнаружения сигнала и синхронизации иередается на один HJ входов блока вычитания 8. На другой вход блока вычитания поступает сигнал либо с ячейки 9, либо 11, равный сумме произведений

первоначальных коэффициентов аь -, о-т на отклик фильтров /I(T) .../т(т), соответствующий предыдущему входному импульсу. Разностный сигнал с выхода блока 8 поступает на блок умнол ения 2. На другие входы блока

приходят сигналы с выхода фильтров. Произведения сигналов через усилители с переменным коэффициентом усиления 5 поступают на масштабные блоки 4. Здесь осуществляется суммирование пришедших сигналов с весом

со значениями коэффициентов на предыдущем цикле адаптации. На этом один цикл корректировки весов аь ..., а заканчивается. По мере поступления входных сигналов циклы корректировки повторяются в описанном по

рядке. 1ак будет продолжаться до тех пор, пока в устройстве не установится с заданной погрешностью набор вполне определенных ко эффициентов аь..., ит- На этом процедура адаптации коррелятора для входпого сигнала с онределенными нараметрами закаичивается.

Полученная при этом импульсная функция устройства будет описывать с заданной среднеквадратической погрешностью корреляционную функцию входного сигнала.

Для сигнала с новыми параметрами процедура адаптации повторяется.

Если в устройство вместо запомипающих ячеек 7, 9 и 11 включить соответственно коммутаторы сигналов, то будет получен адаптивный фильтр для восстановления непрерывного случайного процесса, заданного дискретной последовательностью со случайной частотой следования импульсов.

После осуществления процедуры адантации фильтра в соответствии с вышеоиисанным порядком работы схемы будет получен такой набор коэффициентов Сь ..., йт, который будет обеспечивать восстановление входного сигнала с минимальной среднеквадратической погрешностью.

Формула изобретения

Адаптивный коррелятор случайной импульсной носледовательности, содержащий блок

вычитания, блок синронизации, вход которого соединен со входом блока линейных фильтров, вход которого является входом устройства, а выходы блока линейных фильтров подключены соответственно к первой группе входов первого блока умножения, выходы которого через соответствующие усилители с переменным коэффициентом и масштабные блоки соединены с первой груииой входов второго блока умножения, вторая группа входов которого подключена к соответствующим выходам блока линейных фильтров, выходы второго блока умножения соединены с соответствующими входами сумматора, вторая груииа входов первого блока умножения подключена к выходу блока вычитания, отличающийся тем, что, с целью расширения функциональных возможностей коррелятор содержит три запоминающие ячейки, входы первой и второй запоминающей ячейки подключены к выходу сумматора, а выходы - к первому входу блока вычитания, второй вход которого соединен с выходом третьей запоминающей ячейки, вход которой соединен со входом устройства, управляющие входы запоминающих ячеек подключены к соответствующим выходам блока обнаружения и синхронизации.

Источники информации, принятые во вни- мание при экспертизе:

1.Патент США № 3517879, кл. 235-181, 1970.

2.Я. 3. Цьшкин. Основы теории обучающихся систем. «Наука. 1970, стр. 148-154 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Взаимный коррелятор | 1976 |

|

SU619931A1 |

| Аналого-цифровой коррелятор | 1981 |

|

SU1019462A1 |

| Цифровой автокоррелятор | 1982 |

|

SU1020835A1 |

| СПОСОБ ЛАЗЕРНОЙ ЛОКАЦИИ И ЛАЗЕРНОЕ ЛОКАЦИОННОЕ УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2183841C1 |

| Коррелятор | 1975 |

|

SU525119A1 |

| Цифровой автокоррелятор | 1983 |

|

SU1149277A1 |

| Устройство для определения коэффициентов разложения корреляционной функции по системе ортонормированных базисных функций | 1980 |

|

SU900295A1 |

| Коррелятор | 1982 |

|

SU1042030A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР ЧАСТОТНЫХ СВОЙСТВ ЛИНЕЙНОЙ СИСТЕМЫ | 2003 |

|

RU2242013C2 |

1Зо77г

Авторы

Даты

1977-03-15—Публикация

1975-07-24—Подача