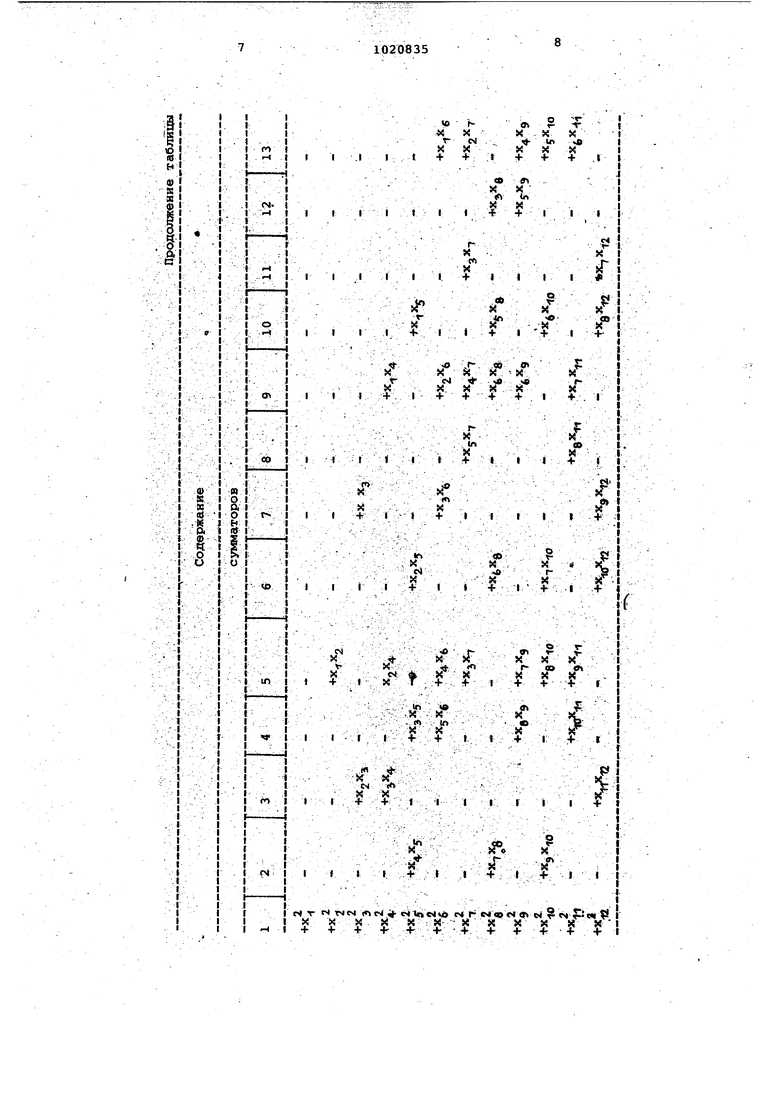

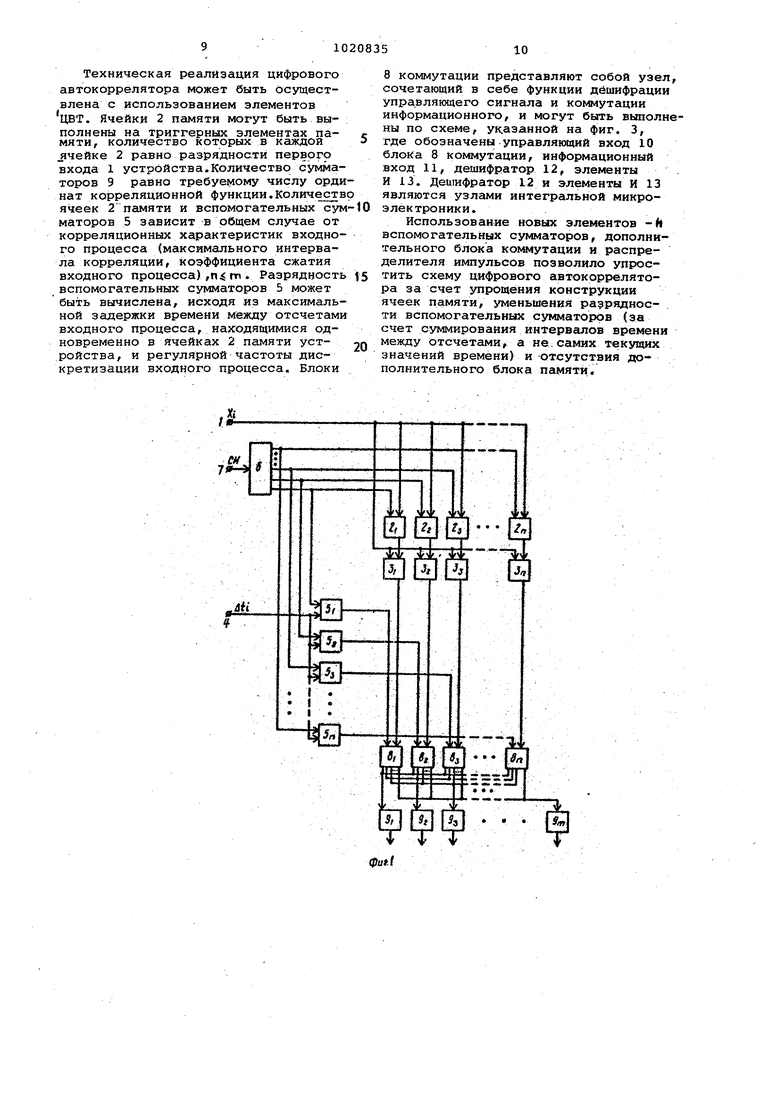

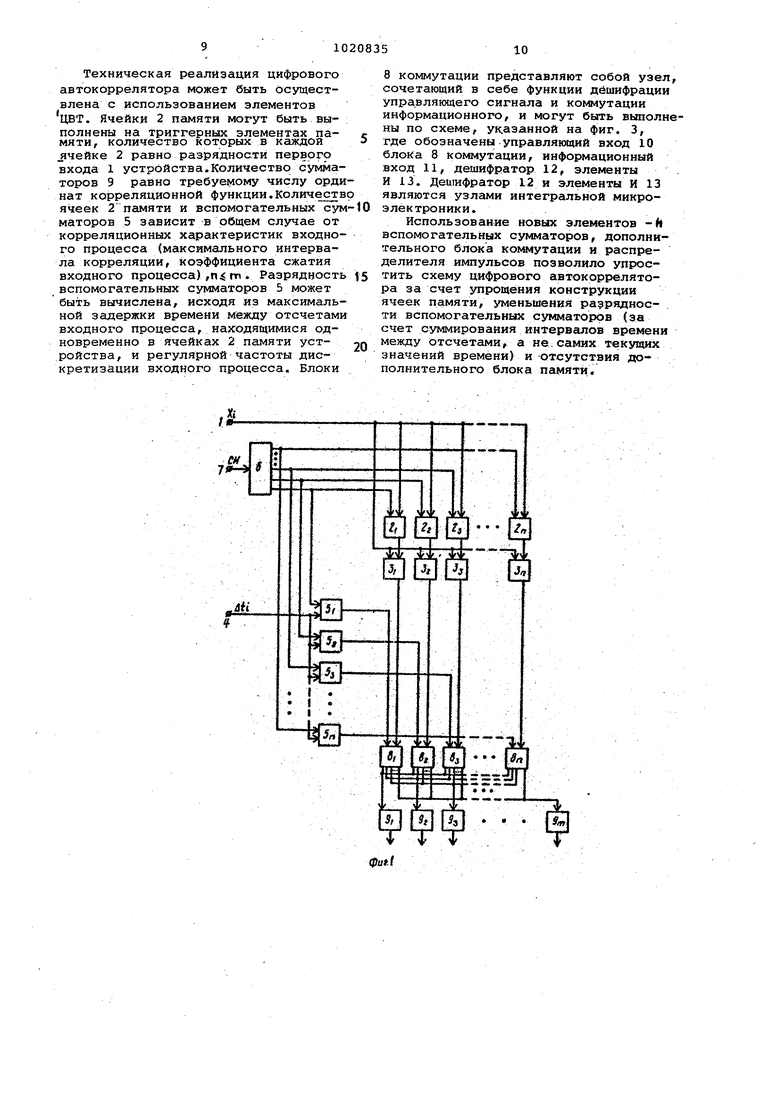

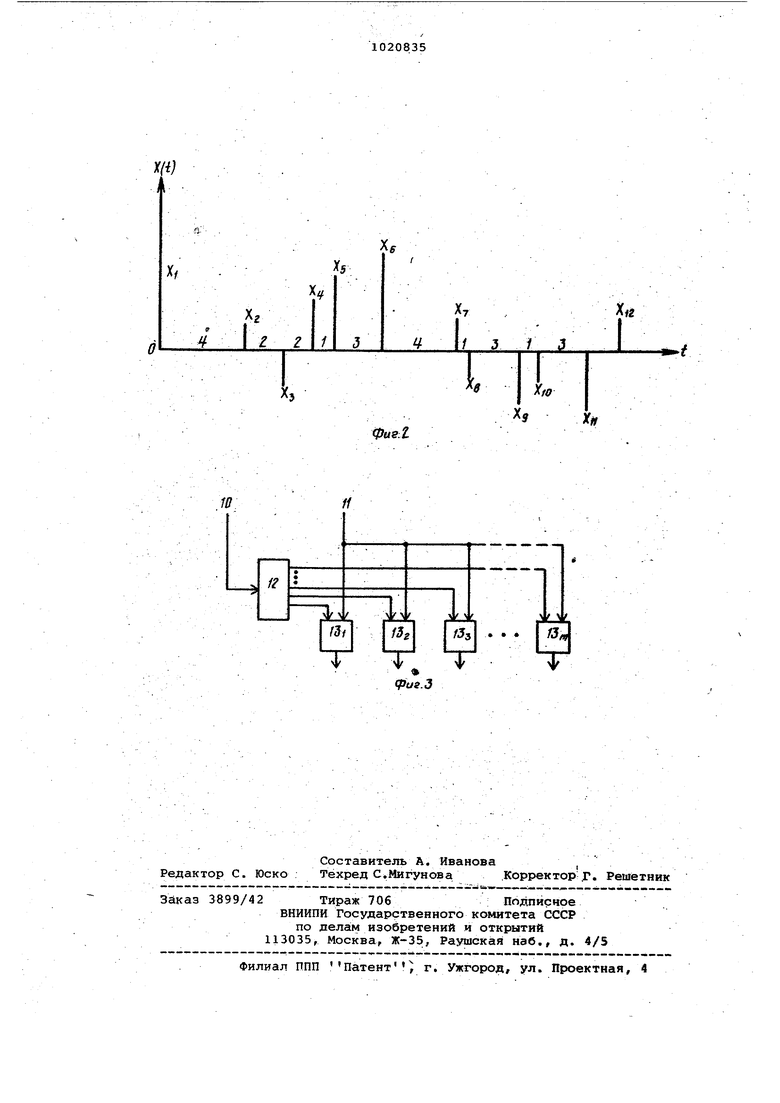

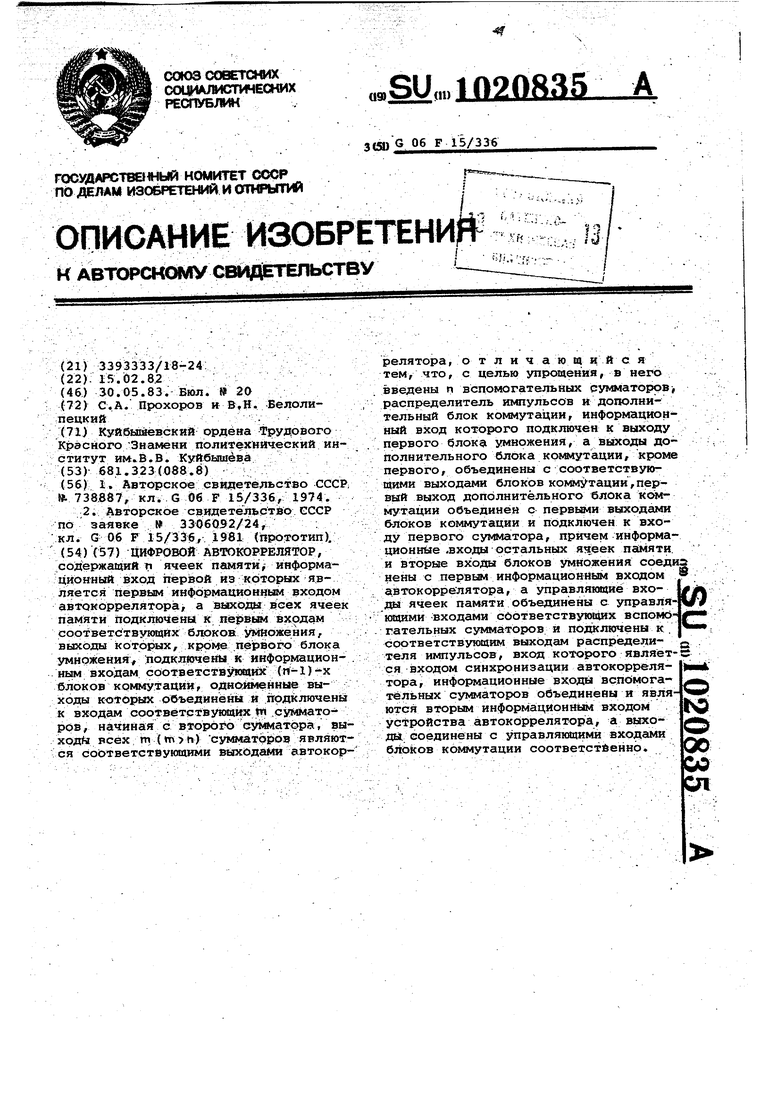

Изобретение относится к измерени характеристик случайных процессов и предназначено для определения корре ляционной функции текущего стационарного случайного процесса, представленного неравноотстоящими отсче тами, в реальном масштабе времени. Известен адаптивный коррелометр, содержащий два аналогоцифровых преобразователя, блок умножения, генератор импульсов, блок памяти, два н копителя, счетчик, блок усреднения, блок задания погрешности, два сумма тора, дополнительный счетчик, накап ливающий сумматор TI 3Указанный адаптивный коррелометр предполагает регулярную дискретиза.цию. входного процесса и не позволяе вычислять корреляционную функцию процесса с нерегулярным шагом дискретизации. Наиболее близким по технической сущности к предлагаемому является цифровой коррелятор, содержащий два блока памяти, состоящих из п последовательно соединенных ячеек памяти каждый,п блоков умножения, (h-l) бл ков вычитаний (п.-1) блоков коммута ции, m сумматоров. Первым входом коррелятора являет вход первого блока памяти. Выход пе вой ячейки первого блока памяти под ключен к первым входам блоков умножения, вторые входы которых соединен с выходами соответствующих ячеек пер вого блока памяти. Вход первого сумматора соединен с выходом первого блока умножения. Вторым входом коррелятора является вход второго блока памяти, выходы ячеек которого, кр ме первой, подключены к первым входам соответствующих блоков вычитания вторые входы которых подключены к выходу первой ячейки второго блока памяти. Выходы блоков вычитания подключены к первым входам соответствующих блоков коммутации, вторые входы которых соединены с выходами соответ ствующих блоков умножения, кроме пер вого. Выходы блоков коммутации подключены к входам соответствующих сум маторов, кроме-первого Сз. Однако для вычисления временных задержек требуется большая разрядность ячеек второго блока памяти и блоков вычитания, так как на второй вход устройства подается абсолютное значение зреме и входного процесса. Кроме того, блоки памяти должны обес печивать параллельные сдвиги содержи мого ячеек, что усложняет их конструкцию. Наличие второго блока памяти и блоков вычитания усложняет корРелятор. Цель изобретения - упрощение устройства. Указанная цель достигается тем, что в цифровой автокоррелятор, содержащийh ячеек памяти, информационный вход первой из которых является первым информационным входом автокоррелятора, а выходы всех ячеек памяти подключены к первым входам соответствующих блоков умножения, выходы которых, кроме первого блока умножения, подключены к информационным входам соответствующих (n-l)-x блоков коммутации, одноименные выходы которых объединены и подключены к входам соответствующих m сумматороз, начиная с второго сумматора, выходы всех гп (туп) сумматоров являются соответствующими выходами автокоррелятора, введены п вспомогательных сумматоров, распределитель импульсов и дополнительный блок коммутации, информационный вход которого подключен к выходу первого блока умножения, а выходы дополнительного блока коммутации, кроме первого, объединены с.соответствующими выходами блоков коммутации, первый выход дополнительного блока коммутации объединен с первыми выходами блоков коммутации и подключен к входу первого сумматора, причем информационные входы остальных ячеек памяти и вторые входы блоков умножения соединены с первым информационным входом автокоррелятора, а управляющие входы ячеек памяти объединены с управляющими входами соответствующих вспомогательных суммато.ров и подключены к соответствующим выходам распределителя импульсов, вход-которого является входом синхронизации автокоррелятора, информационные входы вспомогательных сумматоров объединены и являются вторым информационным входом автокоррелятора, а выхрды соединены с управляющими входами блоков коммутации соответственно. На фиг, 1 представлена структурная схема устройства; на фиг. 2 график входного случайного процесса; на фиг, 3 - структурная схема блока коммутации. Первый вход 1 устройства подключен к информационным входам каждой из Г) Ячеек 2 памяти и вторым входам каждого из п блоков 3 умножения, первые входы которых подключены к выходам соответствующих ячеек 2 памяти. Второй вход 4 устройства подключен к первым входам вспомогательных сумматоров 5, вторые входы которых объединены с управляющими входами соответствующих ячеек 2 памяти и подключены к соответствующим выходам распределителя б импульсов, вход которо- го является третьим входом 7 устройства. Выходы вспомогательных сумматоров 5 подключены к управляющим, а выходы блоков 3 умножения к информационным входам соответствукяцих блоков 8 коммутации, выходы которых Подключены к входам m соответствующих сумматоров 9. Выходы С5п 1маторов являются выходами устройства. Цифровой автокоррелятор работает следующим образом. г , - . Перед началом работы ячейки 8 памяти, а также сумматоры 9 и вспомогательные сумматоры 5 обнулены. На третий вход 7 устройства поступают синхроимпульсы, по которым осуществляется прием текущих значений входного процесса в ячейки 2 памяти и суммирование текущих интервалов времени между отсчетами входного процес са во вспомогательных схадматорах 5. Причем в С1бщем случае входной прЬцесс представлен нерааноотстоящими отсчетами времени. Запись текущих значений входного процесса и суммирование текших интервалов времени осущестйляётся в сортве тствйи с арин ципом циркуляционной организации памяти. Согласно этому принципу с приходом ii-ro синхроимпульса на третий вход 7 устройства на первый -вход 1 устройства nocTyrjaeт текущее значенйе входного процесса к, а на второй вход 4 устройствапоступает теку щий интервал времени ;;.t - -t.. Ра пределитель 6 импульсов осуществляет прследовательную Запись текущегр зна чения X.J входногЬ процесса в ячейку 2 памяти с HOMepbM |(tJn,o 3rt+ и раз решает обНулевие вспомогательного сумматора 5 с таким же номером. В остальных всйомогательных суммато ах 5 йройсходйт суммирование At с содеря анием этих сумматоров 5. Таким , образом, с приходом ч-госинхроим : пульса в ячейках 2 памяти находятся следукадие текущие значения входного процессам в первой X|.jri.,; во второй t-i+2 -J J «М в; (j-H)-fl xr,;j ..Л х.... Аналогично осуществляется последо ва.тельность обнуления вспомогательны сумматоров 5. На выходе блоков 3 умн жения формируются частичные произве дения соответственно; а выходе первого .X|; на вьиоде второго X. ;...; на выходе j-ro на выходе Т)+1)-го х.„ х ;... ; на выходе и-го X4-J Xj. На выхода вспомогательных сумматоров 5 фopмиpsrютcя задержки времени между отсчетами входного процесса соответственно; на выходе первого: V.,.....t. t,-t .j ; на выходе BTOporoj t, j+it| .+...+Л. t на выходе jj -то О, на выходе (j-bl)-rol4t..,.2..4t, t.-t..:,i на выходе п-го At. .. .+4t. ..„+At, ; r HТаким образом, с приходом на третий вход 7 устройства и-го синхроимпульса на информационные входы блоков 8 коммутации подаются частичные произведения с выходов соответствующих блоков 3 умножения, а на управляющие входы блоков 8 коммутации подаются соответствующие .им временные задержки. Поскольку время не убывает, то указанньзе задержки не равны между собой. Каждый блок 8 коммутации выдает частичное произведение, находящееся на его информационном входе, на свой определенный выход и далее на определенный сумматор 9, номера которых соответствуют Коду временной задержки, находящемуся н управляющем входе указанного блока коммутации. Таким образом, адресом Кс1ждого частичного произведения является код соответствующей временной задержки и вследствие неравенства временных задержек частичные произведения пересылаются в разные сумматоры 9, число которых m в общем случае больше числа п ячеек памяти. Частичное произведение х с выхода блока 3 умножения пересылается всегда в первый сумматор 9, так как В J-M вспомогательном сумматоре 5 находится нулевая 3 epkKa. После прихода последнего N-го синхроимпульса и последней пары -Хщ и tu в супинаторах 9 находятся суммы, которые после усреднения дают искомые ординаты оценки корреляционной функции входного процесса,представленного нерав HOOT стоящими отсчетами времени, Для пояснения работы устройства Представлена таблица соответствия содержимого составных блоков авто.коррелятора синхроимпульсам, приходящим на третий вход 7 устройства. Техническая реализация цифрового автокоррелятора может быть осуществлена с использованием элементов цвт. Ячейки 2 памяти могут быть выполнены на триггерных элементах памяти, количество которых в каждой ячейке 2 равно разрядности первого входа 1 устройства.Количество сумматоров 9 равно требуемому числу орди нат корреляционной функции.Количеств ячеек 2 памяти и вспомогательных сум маторов 5 зависит в общем случае от корреляционных характеристик входного процесса (максимального интервала корреляции, коэффициента сжатия входного процесса),. Разрядность вспомогательных сумматоров 5 может быть вычислена, исходя из максимальной задержки времени между отсчетами входного процесса, находящимися одновременно в ячейках 2 памяти устройства, и регулярной частоты дискретизации входного процесса. Блоки 8 коммутации представляют собой узел, сочетающий в себе функции дешифрации управляющего сигнала и коммутации информационного, и могут быть выполнены по схеме, указанной на фиг, 3, где обозначены управлякяций вход 10 блока 8 коммутации, информационный вход 11, дешифратор 12, элементы . И 13. Дешифратор 12 и элементы И 13 являются узлами интегральной микроэлектроники. Использование новых элементов -И вспомогательных сумматоров, дополнительного блока коммутации и распределителя импульсов позволило упростить схему цифрового автокоррелятора за счет упрощения конструкции ячеек памяти, уменьшения разрядности вспомогательных сумматоров (за счет суммирования интервалов времени между отсчетами, а не самих TeKjmuix значений времени) и отсутствия дополнительного блока памяти.

Xf

У#

фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой автокоррелятор | 1983 |

|

SU1104529A1 |

| Коррелятор | 1982 |

|

SU1042030A1 |

| Цифровой автокоррелятор | 1981 |

|

SU968819A1 |

| Цифровой автокоррелятор | 1983 |

|

SU1149277A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Коррелятор | 1984 |

|

SU1173419A1 |

| Коррелятор | 1989 |

|

SU1665386A1 |

| Коррелятор | 1987 |

|

SU1444813A1 |

| Устройство для вычисления структурной и интервальной функций | 1984 |

|

SU1166135A1 |

| Аналого-цифровой коррелятор | 1981 |

|

SU1019462A1 |

ЦИФРОВОЙ АВТОКОРРЕЛЯТОР, сойерчкащий Т1 ячеек паавяти, ияформационный вход первой из которых явЛяется первым информационным входом автокоррелятора, а выходы всех ячеек памяти подключены к первым йхрдам соответствующих бдоконунйожёния, выходы которых, кроме первого блока умнржения, йодклйчены к информационным входам соответсТВ5ПШ1Шс (п-1)-х «локов коммутации, одноименные выходы которых объединён и подключены к входам соотвётствувд(х trt .схгмматоров, начиная с второго еумматор;, выходи всех m () cyMMaTojiOB являются соответствующими клхбдами автокоррелятора, о т л и ч а ю щ и и с я тем, что, с целью упрощения, в него . введены п вспомогательных сумматоров, распределитель импульсов и дополнительный блок коммутации, информационный вход которого подключен к выходу первого блока умножения, а выходы дополнительного блока коммутации, кроме первого, объединены с соответствующими выходами блоков коммутации, первый выход дополнительного блока коммутации объединен с первьвчи выходами блоков коммутации и подключен к входу первого сумматора, причем информационные .входа остальных ячеек памяти. и вторые входы блоков умножения соедиа йены с первым информационным входом ® автокоррелятора, а управлянюшё входы ячеек памяти объединены е управлЯ-1, кзщими входами сйЬтветствукмцих вспомб-|| гательных сумматоров и по Бключены к соответствующим выходам распредели- V, теля импульсов, вход которого являет-с ся входом синхронизации автокоррёлятора, информационные входы вспомогательных сумматоров объединены и являЧ ISD ЭО ются вторым информационным входом устройства автокоррелятора, а выходы: соедине ны с управлякйцими входами блоков коммутации соответстйенно. :«д сд

If

W

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское еввдетельство СССР № | |||

| МУСОРОСОЖИГАТЕЛЬНАЯ НАКЛОННАЯ ШАХТНАЯ ПЕЧЬ | 1923 |

|

SU738A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свндетёльстйо ессР по заявке 3306092/24 кл | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1983-05-30—Публикация

1982-02-15—Подача