элементов И и входом второго формирователя импульсов, выход которого подключен к первым входам блока синхронизации и блока запрета, второй вход которого соединен с выходом первого формирователя импульсов, а выход - с вторым входом первого триггера и вторыми входами соответствующих элементов И. Выходы этих элементов И подсоединены к соответствующим входам группы триггеров, выходы которых соединены через третий формирователь импульсов с первым входом второго триггера и с входами формирователя импульсов, первого блока считывания и с первыми входами третьего и четвертого элементов И, вторые входы которых подключены к выходу второго триггера, а выходы через счетчик грубого отсчета - к одним входам второго блока считывания. Другой вход второго блока считывания соединен с выходами первого блока считывания и блока синхронизации, второй вход которого подключен к выходу первого элемента ИЛИ и к второму входу второго триггера, третий вход блока синхронизации - с первым входом первого элемента И, выходы счетчика точного отсчета - с входа У1и третьего блока считывания.

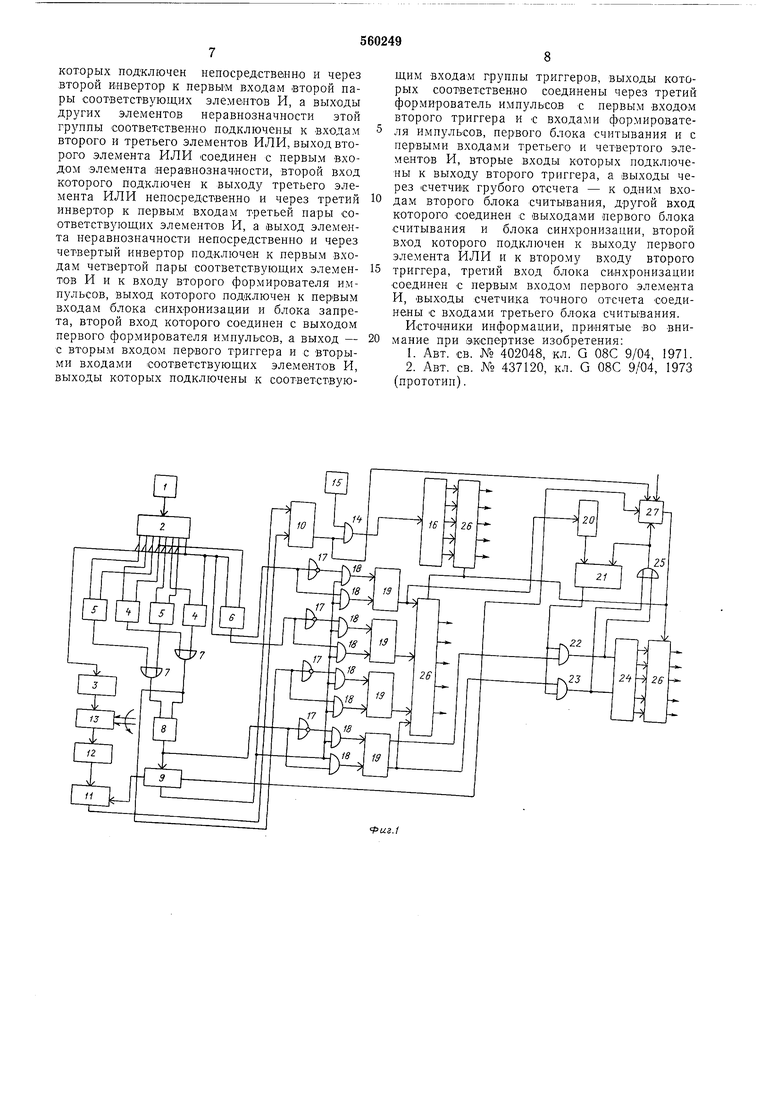

На фиг. 1 представлена функциональная схема преобразователя перемещения в код; на-фиг.2 - временные диаграммы его работы.

Выход генератора 1 импульсов (фиг. 1) через фазорасщепитель 2 подключен к входам формирователя 3 питающего напряжения и к элементам 4, 5 и 6 неравнозначности. Входы каждого из элементов 4 и 5 соединены с выходами фаз фазорасщепителя 2, смещенными

но фазе на - , где п - число фаз, причем п

входы элементов 4 подключены к нечетным выходам, а элементов 5 - к четным выходам. Сдвиг фаз между соседними четными и нечетными выходами фазорасщепителя 2 равен - . п

При наличии больщего количества фаз, чем /г 8, входы элементов 6 должны подключаться к выходам, смещенным по фазе на

1б7С32я9«-1,г

При необходимость в элементе 6 отпадает. Таким образом, элементы 4, 5 и 6 имеют входы, которые по фазе смещены взаимно на величину

к2я4те2 те

« п п п

т. е. временные сдвиги, пропорциональные степеням числа 2.

Выходы элементов 4, 5 неравнозначности через элементы ИЛИ 7 подключены к входам элемента 8 неравнозначности, выход элемента 8 через формирователь 9 коротких импульсов - к одному входу триггера 10 временного интервала и блока 11 запрета, выход которого связан с другим входом триггера 10 временного интервала.

Другой вход блока 11 запрета через формирователь 12 фазовых импульсов соединен с

выходом фазового датчика 13 перемещения, подключенного к формирователю 3 питающего напряжения и сочлененного с контролируемым объектом (на фиг. 1 не показан).

Выход триггера 10 временного интервала

через элемент И 14, к другому входу которого подключен выход генератора 15 эталонной частоты, соединен со счетным входом счетчика 16 точного отсчета.

Выходы элементов неравнозначности 6 и 8,

ИЛИ 7 и одной фазы фазорасщенителя 2 через инверторы 17 и непосредственно подключены к первым входам элементов И 18, другие входы которых связаны с выходом блока 11 запрета, выходы элементов И 18 - к входам триггеров 19 промежуточного отсчета.

Выход триггера 19 старшего разряда промежуточного отсчета через последовательно соединенные формирователь 20 коротких импульсов и триггер 21 подключен к первым

входам элементов И 22 и 23, другие входы которых соединены с выходами триггера 19 младщего разряда промежуточного отсчета, а выходы - с входами сложения и вычитания реверсивного счетчика 24 грубого отсчета

и через элемент ИЛИ 25 с другим входом триггера 21. Выходы триггеров 19 промежуточного отсчета, счетчика 16 точного отсчета, реверсивного счетчика 24 грубого отсчета соединены с первыми входами блока 26 считывания, к другим входам которого подключен блок 27 синхронизации, входы последнего - соответственно с выходами формирователя 9 коротких импульсов, элемента ИЛИ 25 и триггера 10 временного интервала.

Работает преобразователь следующим образом. Генератор 1 импульсов вырабатывает прямоугольные импульсы с частотой /.

На выходе фазорасщепителя 2 выделяются импульсы Kj,- бвф (фиг. 2), смещенные по

фазе на я/ -относительно начала

я

координат (первой фазы) п, имеющие ту же частоту со 2-/.

На выходах элементов 4, 5 и 6 неравнозначности выделяются сигналы И,з, , t/2,4, , t/1,5 (индексы обозначают порядковый номер фазы фазорасщепителя) в соответствии с логическим равенством , где а, b - входные сигналы элемента неравнозначности,

с - выходной сигнал того же элемента.

Сигналы с выходов элементов 4 и 5 логически су.ммируются и на выходе элемента ИЛИ 7 образуются последовательности и.мпульсы

, U-jb с частотой которые после элемента 8 неравнозначности преобразуются в последовательность импульсов с частотой п/.

С выходов фазорасщепителя 2 напряжение поступает на формирователь 3, который питает фазовый датчик 13 перемещения.

На выходе фазового датчика 13, являющегося фазовращателем, в зависимости от углового перемещения 9 выходное напряжение Us изменяется по закону

«т /„с08((йг -в),

где т - коэффициент модуляции;

UH - амплитуда напряжения питания.

В момент времени перехода через нуль Lv формирователь 12 формирует короткие импульсы, проходящие на блок 11 запрета, на второй вход которого поступают короткие импульсы i/9 с формирователя 9, полученные в результате разделения фронтов импульсов t/s с элемента 8 нерав«означности.

ЕСли эти импульсы не совпадают по времени, блок 11 запрета выдает импульсы и, которые поступают на триггер 10 временного интервала, открывают элемент И 14 и импульсы эталонной частоты Un с генератора 15 Подаются на вход счетчика 16 точного отсчета, работающего в режиме вычитания. Как только на другой вход триггера 10 временного интервала поступает импульс с выхода формирователя 9 коротких импульсов, триггер временного интервала перебрасывается в другое положение, элемент И 14 закрывается, счет импульсов в счетчике 16 точного отсчета прекращается и он фиксирует код точного отсчета. Фазовый импульс с блока 11 запрета также поступает «а первые входы элементов И 18, на другие входы которых подаются прямые и инверсные напряжения с выходов фазы фазорасщепителя и элемента 6 .неравнозначности (f/i,o), элемента ИЛИ 7 (), элемента 8 неравнозначности (t/s), которые, как видно из приведенной диаграммы (фиг. 2), образуют временную кодовую маску, в которой положение фазового импульса однозначно соответствует определенно му коду (числу). Триггер 19 промежуточного отсчета запоминает положение фазового импульса в моменты его отсутствия. ЕСли фазовый датчик ГЗ перемещения не меняет положения, состояние триггеров не изменяется в последующие циклы работы.

Блок 11 запрещает прохождение фазового импульса в системе точного и про.межуточного отсчетов в моменты переброса триггеров 10 и 19, совпадаюш.ие с моментами прихода фазового импульса, и исключает таким образом, передачу искаженной информации, С триггеров 19 старшего и младшего разрядов промежуточного отсчета снимаются сигналы 19а и UiQb (фиг. 2) при перемещении подвижной части фазового датчика 13 в одну сторону (увеличения 9). В моменты времени сброса «1 триггера старшего разряда промежуточйого отсчета другой формирователь коротких импульсов (20) формирует импульс С/2о, который запоминается в триггере 21 до момента фор.мированяи кода в младшем разряде промежуточного отсчета.

В зависимости от того, в какую сторону изменился код .в младщем разряде: в стороя;возрастания (появление «О на единичном выходе триггера 19 младшего разряда промежуточного отсчета) или уменьшения (появление там же «I), возникает импульс t/22 на выходе соответствующего элемента И 22 или И 23, который поступает на шину (+) или (-) реверсивного счетчика 24 грубого отсчета и через элемент ИЛИ 25 возвращает триггер 21 в исходное нулевое положение.

Как видно из приведенной диаграммы работы преобразователя, считывание кода со счетчиков грубого, точного и триггеров промежуточного отсчета может производиться в моменты времени, когда не происходит заполнения счетчика точного отсчета и переброса триггеров в грубом и промежуточном отсчете, совпадающие с моментами прихода импульсов Uc, с формирователя 9.

Блок 27 синхронизации с учетом информации с триггера 10 временного интервала, формирователя 9 коротких импульсов, элемента ИЛИ 25 и импульса запроса формирует импульс опроса, поступающий на вход блока 26. с которого считываегся код в момент прихода импульса опроса. Так как заполнение счетчика 16 точного отсчета происходит в интервале времени менее чем в п раз меньшем периоде напряження питания фазового датчика 13 перемещения, опрос счетчиков может быть произведен во времени с задержкой, в п раз меньшей, чем у аналогичных устройств.

Предлагаемый преобразователь перемещения в код обладает более высоким быстродействием съема информации по сравнению с аналогичными устройствами.

Формула изобретения

Преобразователь перемещения в код, содержащий формирователь питающего напряжения, подключенный через фазовый датчик перемещения к входу первого формирователя импульсов, генератор импульсов, счетчик грубого отсчета, выход второго формирователя импульсов соединен с первым входом первого триггера, подключенного к первому входу первого элемента И, в-ыход которого соединен с входом счетчика точного отсчета, выходы третьего и четвертого элементов И подключены к входам первого элемента ИЛИ, отличающийся тем, что, с целью повышения быстродействия съема информации, в него введены блок запрета, элементы неравнозначности, блоки считывания, блок синхронизации, фазорасщепитель и генератор эталонной частоты, подключенный к второму входу первого элемента И, генератор импульсов соединен с входом фазорасщепителя, одни выходы которого соответственно подключены к входу формирователя питающего напряжения и непосредственно и через первый инвертор к первым входам первой пары соответствующих элементов И, другие выходы фазорасщепителя соединены с входами группы элементов неравнозначности, выход одного из

которых подключен непосредственно и через второй инвертор к первым входам второй нары соответствующих элементов И, а выходы других элементов неравнозначности этой группы соответствеННо подключены к входам второго и третьего элементов ИЛИ, выход второго элемента ИЛИ соединен с первым входом элемента неравнозначности, второй вход которого подключен к выходу третьего элемента ИЛИ непосредственно и через третий инвертор к первым входам третьей пары соответствующих элементов И, а выход элемента неравнозначности непосредственно и через четвертый инвертор подключен к первым входам четвертой пары соответствующих элементов Инк входу второго формирователя и.мпульсов, выход которого подключен к первым входам блока синхронизации и блока запрета, второй вход которого соединен с выходом первого формирователя импульсов, а выход - с вторым входом первого триггера и с вторыми входами соответствующих элементов И, выходы которых подключены к соответствующим входам группы триггеров, выходы которых соответственно соединены через третий формирователь импульсов с первым входом второго триггера и с входами формирователя импульсов, первого блока считывания и с первыми входами третьего и четвертого элементов И, вторые входы которых подключены к выходу второго триггера, а выходы через счетчик грубого отсчета - к одним входам второго блока считывания, другой вход которого соединен с выходами первого блока считывания и блока синхронизации, второй вход которого подключен к выходу первого элемента ИЛИ и к второму входу второго

триггера, третий вход блока синхронизации соедипен с первым входом первого элемента И, выходы счетчика точного отсчета соединены с входами третьего блока считывания. Источники информации, принятые во внимание при экспертизе изобретения:

1.Авт. св. N° 402048, кл. G 08С 9/04, 1971.

2.Авт. св. Ко 437120, кл. С 08С 9/04, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Фотоэлектрический преобразователь угол-код | 1984 |

|

SU1197081A1 |

| Преобразователь уго-код | 1972 |

|

SU439836A1 |

| Преобразователь перемещение-код | 1974 |

|

SU525141A1 |

| Преобразователь перемещений в код | 1978 |

|

SU763939A1 |

| Ультразвуковой измеритель перемещений | 1989 |

|

SU1619027A1 |

| Преобразователь углового перемещения в код | 1975 |

|

SU556472A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942095A1 |

| Преобразователь угол-код | 1983 |

|

SU1116447A1 |

| Преобразователь перемещения в код | 1980 |

|

SU886025A1 |

| Измерительный преобразователь линейных перемещений | 1988 |

|

SU1552002A1 |

Авторы

Даты

1977-05-30—Публикация

1974-12-26—Подача