1

Изобретение относится к радиоэлектронике и может использоваться в различной аппаратуре, содержащей мпогокаокадиые делители частоты, напр;имер в устройствах формирования опорных частот.

Известно устройство для деления частоты с обиаружением устойчивых отказов, содержащее счетчики, блоки установки иелых чисел, триггеры и логические элементы . Но в таком устройстве с увеличением коэффициента деления делителя увеличивается объем схем контроля.

Известно также устройство, содержащее счетчики, вход одного из которых подключен к входной шине, а выход другого соединен с одним из входов устройства контроля {2. Однако это устройство не обладает достаточной надежностью в работе.

Цель изобретения - повыщение надежности устройства в работе.

Это достигается тем, что в предлагаемый делитель частоты введены элементы И и //(-триггеры, к /-входу иервого из которых подключен выход первого счетчика, а к /-входу iBTOporo - выход второго счетчика, установочные входы счетчиков соединены через один из элементов И с лрямььми выходами //(-триггеров, на /(-1входы которых подан входной сигнал, при этом одни в.ходы второго и третьего элементов И соединены с выхода2

ми первого //(-триггера, вторые их входы подключены к входной шине, выход второго подключен к входу второго счетчи,ка, а выход третьего - к первому входу четвертого элемента И, второй вход которого соединен с прямым выходом второго //(-триггера, а устройство контроля содержит контрольный //(-триггер, элемент 2И-ИЛИ н элемент запрета, причем выход третьего элемента И и выход второго //(-триггера подключены через элемент запрета к: /(-входу контрольного //(-триггера, /-вход которого соединен с первым входом элемента 2И-ИЛИ, второй и третий входы которого иодключены к выходам коитрольного //(-триггера, а четвертый вход - к выходу третьего элемента И.

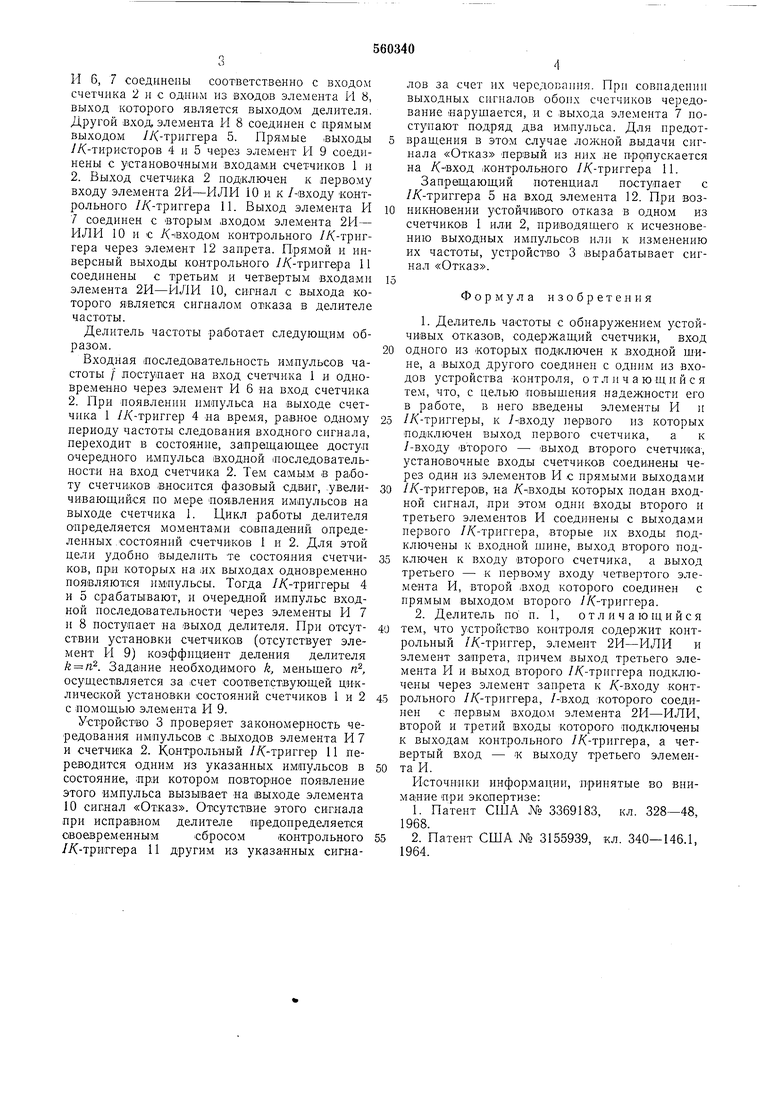

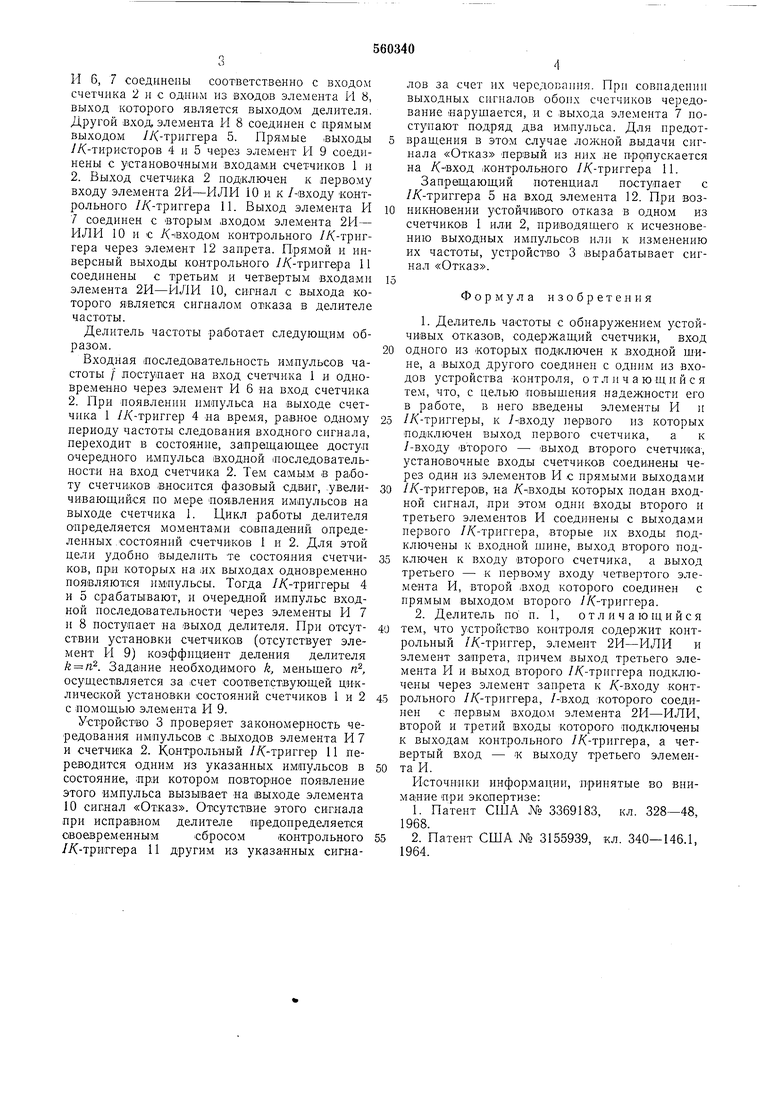

На чертеже представлена структурная электрическая схема предлагаемого делителя частоты с обнаружением устойчивых отказов.

Делитель частоты содержит два счетчика 1 и 2 с одинаковыми коэффициентами деления п и устройство 3 контроля. Выход счетчика 1 соединен с /-входом //(-триггера 4, а выход счетчика 2 - с /-входом //(-триггера 5, /(-входы этих триггеров управляются входными сигналамп, которые поступают также на вход счетчика 1 п на однп из входов элементов И 6 и 7. Другие входы элементов И 6, 7 соединены соответственно с инверсным и прямым выходами //(-триггера 4. Выходы элементов

И 6, 7 соединены соответственно с входом счетчика 2 и с одним из входов элемеита И 8, выход которого является выходо-м делителя. Другой вход, элемента И 8 соединен с прямым выходо.м //(-триггера 5. Прямые выходы //(-тирИСторов 4 и 5 через элемент И 9 соединены с установочными входами счетчиков 1 и 2. Выход сч.етчика 2 иодключен к первому входу элемента 2И-ИЛИ 10 и к /-входу контрольного //(-триггера 11. Выход элемента И 7 соединен с вторым входом элемента 2И- ИЛИ 10 и с /(-1ВХОДОМ контрольного /Д-триггера через элемент 12 заирета. Прямой и инверсный выходы контрольного //(-триггера 11 соедннены с третьим и четвертым входами элемента 2И-ИЛИ 10, сигнал с выхода которого являет1ся сигналом отказа в делятеле частоты.

Делитель частоты работает следующим образом.

Входная последовательность импульсов частоты / лостунает на вход счетчика 1 и одновременно через элемент И 6 на вход счетчика 2. При появлении импульса на выходе счетчика 1 //(-триггер 4 на время, равное одному периоду частоты следования входного сигнала, переходит в состояние, запрещающее доступ очередного импульса входной 1носледовательности на вход счетчика 2. Тем са1мы,м в работу счетчиков вносится фазовый сдвиг, .увеличивающийся по мере появления импульсов на выходе счетчика 1. Цикл работы делителя определяется моментами совнадений определенных .состояний счетчиков 1 и 2. Для этой цели удобно выделнть те состояния счетчиков, ири которых на ;их выходах одновременно появляются импульсы. Тогда /Д-триггеры 4 и 5 срабатывают, и очередной импульс входной иоследовательиости через элементы И 7 и 8 поступает на выход делителя. При отсутствии установки счетчиков (отсутствует элемент И 9) коэффициент деления делителя k n. Задание необходимого k, меньшего п, осуществляется за счет соответствующей циклической установки состояний счетчиков 1 и 2 с помощью элемеита И 9.

Устройство 3 проверяет законО|Мерность чередования импульсов с выходов эле.мента И 7 и счетчика 2. Контрольный //(-триггер 11 переводится одним из указанных импульсов в состояние, при котором повторное появление этого импульса вызывает на выходе элемеита 10 сигнал «Отказ. Отсутст1вие этого сигнала при исправном делителе предопределяется своевременнымсбросом контрольного

//(-триггера 11 другим из указанных сигналов за счет их черсдоваиия. При совиадении выходных сигиалов обоих счетчиков чередование нарушается, и с выхода элемента 7 постуиают подряд два им1иульса. Для иредотвращения в это-м с-тучае ложиой выдачи сигнала «Отказ первый из них не пропускается на Д-вход .контрольного /Д-триггера 11.

Запрещающий иотенциал поступает с /Д-триггера 5 на вход элемента 12. При возиикновении устойчивого отказа в одном из счетчиков 1 или 2, приводящего к исчезиовению выходных импульсов или к измеиению их частоты, устройство 3 вырабатывает сигнал «Отказ.

Формула изобретения

1. Делитель частоты с обиаружением устойчивых отказов, содержащий счетчики, вход

одного из которых подключен к входной щине, а выход другого соединен с одним из входов устройства коитроля, отличающийся тем, что, с целью повышения надежности его в работе, в него введены элементы И и

/Д-триггеры, к /-входу первого из которых подключен выход первого счетчика, а к /-входу второго - выход второго счетчика, установочные входы счетчиков соединены через один из элементов П с ирямыми выходами

/Д-триггер01В, на /(-входы которых иодан входной сигнал, при этом одни входы второго и третьего элементов И соединены с выходами первого /Д-трнггера, вторые их входы подключены к входной щине, выход второго подключ-ен к входу второго счетчика, а выход третьего - к первому входу четвертого элемеита И, второй .вход которого соединен с прямым выходом второго //(-триггера.

2. Делитель по п. 1, от л и ч а ю и; и йс я

тем, что устройство контроля содержит коитрольиый /Д-триггер, элем.ент 2И-ИЛИ и элемент запрета, причем -выход третьего элемеита PI и выход второго /Д-триггера иодключены через элемент запрета к Д-входу контрольного //(-триггера, /-вход которого соединен с первым входом элемеита 2И-ИЛИ, второй и третий входы которого подключены к выходам контрольного /Д-триггера, а четвертый вход - к выходу третьего элемеита И.

Источники информации, принятые во внимание при экспертизе:

1. Патент США № 3369183, кл. 328-48, 1968.

2. Патент США № 3155939, кл. 340-146.1, 1964. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервируемый генератор | 1982 |

|

SU1027850A1 |

| УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ ПОСТЕПЕННЫХ ОТКАЗОВ ЭЛЕКТРОННЫХ ПРИБОРОВ | 1971 |

|

SU428361A1 |

| Устройство для определения координат точечных световых объектов | 1974 |

|

SU526928A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1986 |

|

SU1339857A1 |

| Устройство для измерения девиации частоты линейно частотно-модулированного колебания | 1983 |

|

SU1190281A1 |

| Устройство для моделирования вероятностного графа | 1985 |

|

SU1273959A2 |

| Устройство для измерения амплитуды переменного напряжения | 1984 |

|

SU1185254A1 |

| Преобразователь перемещения в код | 1984 |

|

SU1236611A1 |

| СЕЛЕКТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ | 1993 |

|

RU2072627C1 |

Авторы

Даты

1977-05-30—Публикация

1974-05-22—Подача