Изобретение относится к импульсной техямке и может быть использовано в цифровой измерительной аппаратуре, в устройствах вычислительной техники, промышленной автоматики и телемеханики.

Известен управляемый делитель частоты следования импульсов, содержащий счетчик импульсов на триггерах, счетный вход которого подключен к входной шине, а нулевые выходы соединены с первыми входами соответствующих элементов совпадения, вторые входы которых подключены к шинам управления кодом коэффициента деления, а выходы - к соответствующим входам первого элемента ИЛИ, выход которого соединен с единичным входом основного

триггера второй элемент ИЛИ, первый вход которого соединен с входной шиной, остальные входы - с единичными выходами соответствующих триггеров счетчика импульсов, s выход - с нулевым входом основного триггера, дополнительный триггер нулевой вход которого соединен с нупевым входом основного триггера, первый и второй элементы 2И-Н Е, первые входы котг ых подключены к входной шине, а вторые - соответственно к единичным выходам основного и дополнительного триггера, D вход дополнительного триггера соединен с единичным выходом основного триггера причем выход второго элемента 2И-НЕ является выходом делителя и соединен с нуле-ч

ю Ч

выми входами триггеров счетчика импульсов, а выход первого элемента 2И-НЕ подключен к С-входудополнительноготриг- герэ.

Недостатком делителя является сравнительно низкая ремонтопр годностч, обусловленная тем, что выход из строя (отказ) любого из триггеров устройства приводит к отказу устройства в целом.

Наиболее близким по технической сущности к предлагаемому является управляемый делитель частоты следования импульсов, содержащий счетчик импульсов на триггерах, основной, дополнительный и резервный триггеры, ч етыре элемента 2И-НЕ, элемент ИЛИ, элемент 4 - РАВНОЗНАЧНОСТЬ - ИЛ И-НЕ, три элемента И, два элемента И/И-НЕ, пять элементов И-ИЛИ/И- ИЛИ-НЕ, три элемента НЕ, пять элементов 2-2И-ИЛИ, элемент 2И-ИЛИ-НЕ, четыре элемента 2И-ИЛИ/2И-ИЛИ-НЕ, причем шины управления кодом коэффициента деления подключены к вторым входам соответствующих групп РАВНОЗНАЧНОСТЬ элемента 4 - РАВНОЗНАЧНОСТЬ - ИЛИ-НЕ, счетный вход устройства соединен с первым входом первого элемента И, с первым входом элемента ИЛИ, с первым входом второго элемента 2И-НЕ, с вторым входом первой структуры И первого элемента 2И-ИЛ1Л и с первым входом второго элемента И/ИгНЕ, тины управления работой триггеров устройства подключены к входам соответствующих элементов НЕ, к соответствующим входам первого элемента И/И-НЕ и к соответствующим входам второй структуры И элементов И-ИЛИ/И-ИЛИ-НЕ, выходы элементов НЕ подключены также к соответствующим входам вторых структур И элементов 1/1- ИЛИ/И-ИЛИ-НЕ, инверсный выход элемента И/И-НЕ соединен с вторым входом первого элемента И и с вторым входом первой структуры И первого элемента 2И- ИЛИ/2И-ИЛЙ-НЕ, выход первого элемента И соединен со счетным входом первого триггера счетчика импульсов, прямой выход которого соединен с первым входом первой структуры И первого элемента 2И-ИЛИ/2И- ИЛИ-НЕ, прямой выход первого элемента И/И-НЕ соединен с первым входом второй структуры И первого элемента 2И-ИЛИ/2И- ИЛИ-НЕ, с первым входом первой структуры И первого элемента 2И-ИЛИ и с входом первой структуры И первого элемента И- ИЛИ/И-ИЛИ-НЕ, инверсный выход которого соединен с вторым входом первой структуры И второго элемента 2И-ИЛИ/2И- ИЛИ-НЕ и с вторым входом второй структуры И первого элемента 2И-ИЛИ, выход

которого соединен со счетным входом второго триггера счетчика импульсов, выход которого соединен с вторым входом второй структуры И первого и с первым входом

первой структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ, прямой выход первого элемента И-ИЛИ/И-ИЛИ-НЕ соединен с первым входом второй структуры И второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с первым

0 входом первой структуры И второго элемента 2И-ИЛИ и с входом первой структуры И второго элемента И-ИЛИ/И-ИЛИ-НЕ, инверсный выход которого соединен с вторым входом первой структуры И третьего эле5 мента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй структуры И второго элемента 2И-ИЛИ, выход которого соединен со счетным входом третьего триггера счетчика импульсов, прямой выход которого соединен

0 с вторым входом пторой структуры И второго и с первым входом первой структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход второго элемента И-ИЛИ/И- ИЛИ-НЕ соединен с первым входом второй

5 структуры И третьего элемента 2И- ИЛИ/2Й-ИЛИ-НЕ, с первым входом первой структуры И третьего элемента 2И-ИЛИ и с входом первой структуры И третьего элемента И-ИЛИ/И-ИЛИ-НЕ, выход третьего

0 элемента 2И-ИЛИ соединен со счетным входом четвертого триггера счетчика импульсов, выход которого соединен с вторым входом второй структуры И третьего и с первым сходом первой структуры И четвертого

5 элементов 2И-ИЛИ/2И-ИЛИ-НЕ, инверсным выход третьего элемента И-ИЛИ/И- ИЛИ-НЕ соединен с вторым входом первой структуры И четвертого элемента 2И- ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй

0 структуры И третьего элемента 2И-ИПИ, прямой выход третьего элемента И-ИЛИ/И- ИЛИ-НЕ соединен с первым входом первой структуры И четвертого элемента 2И- ИЛИ/2И-ИЛИ-НЕ, с вторым входом второго

5 элемента И, с первым входом первой структуры И элемента 2И-ИЛИ-НЕ и с входом первой структуры И четвертого элемента И- ИЛИ/И-ИЛИ-НЕ, инверсный выход которого соединен с вторым входом первой

0 структуры И четвертого элемента 2И-ИЛИ, с первым входом третьего элемента 2И-НЕ и С первым входом второй структуры И элемента 2И-ИЛИ-НЕ, прямой выход четвёртого элемента И-ИЛИ/И-ИЛИ-ИЕ соединен с

5 первым входом второй структуры И четвертого элемента 2И-ИЛИ, с первым входом четвертого элемента 2И-НЕ и с входом первой структуры И пятого элемента И-ИЛИ/И- ИЛМ-НЕ, инверсный выход которого соединен с вторым входом первой структу517S7Q976 I

ры И пятого элемента 2И-ИЛИ, с втррьпиц элемента И, прямой выход четвертого эле- входом первого элемента 2И-ЙЕ и с первым мента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с входом третьего элемента И, прямой выхрд;Г пятым входом элемента ИЛИ, инверсный пятого элемента,И-ИЛЙ/И-ИЛИ-Н соед№;; выход четвертого элемента 2И-ИЛИ/2И- нен с первым йходом второй структущ „5 ,, ИЛИ-НЕ соединен с первым входом четвер- пятргр элемента 2Й-И)Чй, выход ретьего. 0 той структуры РАВНОЗНАЧНОСТЬ элемента 2И-ШЙ , соединен . с инверсным, элемента 2-РАВ HQ3H АЧ НОСТЬ-ИЛ И-Н Е, S-входом основного триггера, счетный вход выход которого соединен с.втором ВУОДОМ которого соединен с выходом второго дле- . третьего элемента 2И-НЕ и с вторым входом мента И, выход элемента 2И-ЙЛИ-НЕ ре-;110 четвертого элемента 2И-НЕ, выход четвер- динен с инверсным R-вхбдом рсновнрго . того элемента 2И-ИЛИ соединен с вторым триггера, прямой выход которого соединен . входом второго элемента Й/И-НЕ, с вторым с вторым входов второй структуры И четвер;,; входом третьего элемента И и с Р-ВХОДОМ того элемента 2И-ИЛИ/2И:ИЛИ-НЕ и с пер- ;j резервного триггера, выход элемента ИЛИ вым входом Нёрвой структуры И четвертого j5 соединен с вторым входом второй структу- элемента 2И-ИЛИ, прямой и инверсны.й.вы-. ры И элемента 21/1-ИЛЙ-НЕ и с R-входом кокы вго дгр мен /у -НЁ со д н ц I дополнительного и резервного триггеров, соответствёнйр с. пё|)вчым входом первргр ( выход пятого элемента Sl/j-binИ соединен с элемента2И;НЕ сосчетным входом резер;;- ; вторым входом второго элемента 2Й-ИЛИ. внрго триггера; выход четвертого элемента j 20 выход которого является выходом делителя 2И-НЕ соединение инверсн ым S-вхрдрм др-;..; и соединен с нулевыми входами fpi rrepcm полнительйрготриггера, счетный вход котог/. счетчика и с вторым вхоДбм гТёр вбйструктур рого соеДинёьГс вьГхрдрм первого .элеме.нтё,,. ры И элемента 2И-ИЛИ-НЕ.: ; г 2И-НЕ, выход ЧретьргЬ элемента И среди-д,5, :.ч:-:/ bi /

нен с О-входом дрпрлнитёльнрго триггера,, 25 Устройство позволяет при отказе од- прямой Bbi o pToporp соединен Ctвтр|зЫм ь.,; ного из триггеров счетчика импульс ов, или входом второй.чСтр уктуры Л ч/ётверУогаэ е основного и дополнитйл ьного триггеров, мента 2И-ЙЛЙ и Ь пё рвым входом п р. автоматически восстановить работоспо-. структур ы И Н ятб го элементаi , собность устройства „путем подачи соот- прямой выход резервного триггера среди-.ДО ветствующего кода на щйну управления нен с вторым входом второй структуры ( рабртрспрсобной .структурой устройст- пятргЬ Элбмейта 2Й-ЙЛИ, прямой выхрд , ва.; r.ii.vustif ; JHU i,V; -

первого элемента 2И-ЙЛИГ/2Й-1/1ЛЙ-ЙБ,со-1,;,.Недостатком известного устройства

единен с .вторым входом элемента ИЛЙ(, :ин-г:,, является нербходимрсть проведения версный выход .первого элемента 35 .специальных диагностических процедур 2И-ИЛИ/2И-ИЛЙ-НЁ; соединен с пёрвы1м м..л для выявления отказ/авшего::триггера и входом первой структуры РАВНОЗНАЧ- J . средств для реконфигурации работоспо- НОСТЬ элемента 4 рАВН03НАЧНЬ€Т (:г собной структуры устройства ., ИЛИ-НЕ, с первым входом втр ррЙ . . ;.|: ,,,.. ., ...Hcwq.-j йохиь -; структуры И первого элемента 2И-ЙЯИ. Цель изобретения, - повышение экс-, вторым вх6д6м:первой структуры Й торо-- плуатационной отказоустойчивости уст- го элемента 2И-ИЛИ, прямой выход втррр-,,. ройства путем включения, в структуру го .элемёнт:а 2И-Й Л И/2И-ЙЛ Й;Н Ё е vv| триггера каждого разряда счетчика, основ- соединен с четвертым входом элемента.., ного, дополнительнргр,и резервного триг- ИЛИ, инверсный выход второго элемента 45 геров, средств встроенного ..контроля за 2И-ИЛИ/2Й-ИЛИ-НЕ соединен с первым, правильностью срабатыдания и автомати- входом второй структуры РАВНОЗ.йДЧ,:у;,7 зации процесса реконфигурации рабрто- НОСТЬ элемента 4-pABH03HA4HOCTfirj,M,, способной структуры устройства, ИЛИ-НЕ, с первым входом второй...i v Поставленная цель до.сти.гаетс.ягтем, структуры И второго элемента 2И-ЙЛЙИсг р что управляемыД дештель частоты слё вторым входом первой структуры И третье дования импульсов, срдержащий счетчик го элемента 2И-ИЛИ, прямой выход третье - ;. : импульсов, на триггерах, основной, до- го элемента 2И-ИЛ И/2И-И Л ИлНЕ соединен7 ., полнительный и резервный триггеры, чсгы- с третьим входом элемента ИЛИ, инверс, ре элемента,,И,/пять элеме нтрв 2И-ИЛИ, ный выход третьего элемента 2И-ИЛИ( пять элементов 2й-ЙЛИ7||И-ИЛЙ-НЕ, четы- ИЛИ-НЕ соединен с первым входом третье u i ре элемента И-ЙЁ, первый элемент ИЛИ и структуры РАВНОЗНАЧНОСТЬ элемрнта, элемент 4-РАВЩзЩчШСТ -ИлМ-НЕ.. РАВНОЗНАЧНОСТЬ-ИЛИ-НЁ, с первым причем шины управления кодом коэффици- ВХОДОРЛ второй структуры И третьего эл -. ента деления подключен к первым входам мента 2И-ИЛИ и с первым входом второго; соответствующих структур РАВН03НАЧНОСТЬ элемента 4-РАВНОЗНАЧНОСТЬ- ИЛИ-НЕ, счетный вход устройства соединен с вторым входом первой структуры И первого элемента 2И-ИЛИ, с перьым входом первого элемента И, с первым входом первого элемента ИЛИ и с первым входом четвертого элемента И-НЕ, выход первого элемента И соединен со счетным входом первого триггера счетчика импульсов, выхб- ды первого-третьего элементов 2И-ИЛИ соединены соответственно со счетным входом второго-четвертого триггеров счетчика импульсов, прямой выход первого триггера счетчика импульсов соединен с первым входом первой структуры И первого эпемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход которого соединен с вторым входом первого элемента ИЛИ, инверсный выход первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом первой структуры РАВ- НОЗНАЧНОСТЬ элемента 4-РАВНО- ЗНАЧНОСТЬ-ИЛИ-НЕ и с первым входом второй структуры И первого и с вторым входом первой структуры И второго элемента 2И-ИЛИ, прямой выход второго триггера счетчика импульсов соединен с вторым входом второй структуры И первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с первым входом первой структуры И второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход которого соединен с третьим входом первого элемента ИЛИ, инверсный выход второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом второй структуры РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧ- НОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И второго и с вторым входом первой структуры И третьего элементов 2И- ИЛИ, прямой выход третьего триггера счетчика импульсов соединен с вторым входом второй структуры И аторого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с первым входом первой структуры И третьего элемента 2И- ИЛИ/2И-ЙЛИ-НЕ, прямой выход которого соединен с четвертым входом первого элемента ИЛИ, инверсный выход третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом третьей структуры РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧ- НОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И третьего элемента 2И-ИЛИ и с первым входом второго элемента И, прямой выход четвертого триггера счетчика импульсов соединен с вторым входом второй структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с первым входом первой структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход которого соединен с пятым входом первого элемента ИЛИ, ,ь|й выход четвертого

элемента 2И-ИЛИ/2И-ИЛИ-НР соединен с вторым входом четвертой структуры РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧ- НОСТЬ-ЙЛИ-НЕ, выход которого соединен

с первым входом первого элемента И-НЕ и с вторым входом второго элемента И-НЕ, прямой выход основного триггера соединен с вторым входом второй структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ

0 и с первым входом первой структуры И четвертого эпемента 2И-ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с D-входом дополнительного триггера, пря5 мой выход дополнительного триггера соединен с вторым входом второй структуры И четвертого и с первым входом первой структуры И пятого элемента 2И-ЙЛИ, прямой выход резервного триггера соеди0 лен с вторым входом второй структуры И пятого элемента 2И-ИЛИ выход которого соединен с вторым входом четвертого элемента И-НЕ, выход которого является выходом делителя, и соединен с R-входа5 ми первого-четвертого трип еров счетчика импульсов, с первым входом первой структуры И пятого элемента 2И-ИЛИ/2И- ИЛИ-НЕ, инверсный выход которого соединен с R-входом основного триггера,

0 выход первого элемента ИЛИ соединен с вторым входом второй структуры И пятого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с R-входа- ми дополнительного и резервного триггеров, выходы первого и второго элементов

5 И-НЕ соединены соответственно с S-входа- ми основного и дополнительного триггеров, выход второго элемента И соединен со счетным входом основного триггера, выход третьего элемента И-НЕ соединен со счет0 ным входом дополнительного триггера, выход третьего элемента И соединен с D-входом дополнительного триггера, дополнительно содержит элемент И/И-НЕ, два элемента ИЛИ, пять элементов ИЛИ/ИЛИ5 НЕ, элемент НЕ, пять элементов И, а каждый триггер в своей структуре содержит элемент И, восемь элементов И-НЕ, четыре элемента НЕ. элемент И/И-НЕ и элемент 7И-ИЛИ, причем инверсный S-вход каж0 дого триггера соединен с первым входом элемента И, с входом третьего элемента НЕ, с первыми входами третьего л восьмого элементов И-НЕ, с третьим входом пер- вой, с пятым входом второй, с четвертым

5 входом третьей и с четвертым входом четвертой структур И элемента 7И-ИЛИ, D- вход каждого триггера соединен с первым входом первого элемента И-НЕ, с входом второго элемента НЕ и с вторым входом третьей структуры И элемента 7И-ИЛИ

V-вход каждого триггера соединен с вторым входом элемента И третий вход которого соединен со счетным входом каждого триггера инверсный R-вход каждого триггера соединен с четвертым входом элемента И, с входом четвертого элемента НЕ, с третьими входами четвертого и восьмого элементов И-НЕ, с четвертым входом первой, с шестым входом второй, с пятым входом третьей и с пятым входом четвертой структур И элемента 7И-ИЛИ, вход RF установки в исходное состояние средств функционального контроля каждого триггера соединен с первым входом седьмой структуры И элемента 7И-ИЛИ, выход элемента И каждого триггера соединен с вторым входом первого и второго элементов И-НЕ и с входом первого элемента НЕ, выход которого соединен с входами элемента И/И-НЕ, с вторыми входами пятого и шестого элементов И- НЕ, с пятым входом первой и с третьим входом второй структуры И элемента 7И- ИЛИ, выход первого элемента И-НЕ соединен с первым входом второго и с вторым входом третьего элементов И-НЕ, выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ, выход которого соединен с третьим входом третьего, с первым входом шестого элементов И-НЕ, с вторым входом первой, с первым входом третьей и с первым входом пятой структур И элемента 7И-ИЛИ выход третьего элемента И-НЕ соединен с первыми входами четвертого и пятого элементов И-НЕ, с вторым входом второй, с первым входом четвертой и с первым входом шестой структур И элемента 7И-ИЛИ, выходы пятого и шестого элементов И-НЕ соединены соответственно с вторыми входами седьмого и восьмого элементов И-НЕ, прямой выход элемента И/И-НЕ каждого триггера соединен с шестым входом первой и с четвертым вхбдом второй структуры И элемента 7И- ИЛИ, инверсный выход элемента И/И-НЕ соединен с третьими входами третьей и четвертой структур И элемента 7И-ИЛИ, выход второго элемента НЕ соединен с вторым входом четвертой структуры И элемента 7И-ИЛИ, выходы третьего и четвертого элементов НЕ каждого триггера соединены соответственно с вторыми входами пятой и шестой структур И элемента 7И-ИЛИ, выход седьмого элемента И-НЕ является прямым выходом каждого триггера и соединен с первым входом восьмого элемента И-НЕ и с первым входом первой структуры И элемента 7И-ИЛИ выход восьмого элемента И-НЕ является инверсным выходом каждого триггера и соединен с третьим

входом седьмого элемента И-НЕ и с первым входом второй структуры И элемента 7И ИЛИ, выход которого является выходом От каз каждого триггера и соединен с вторым 5 входом своей седьмой структуры И та кто вый вход делителя частоты следования им пульсов дополнительно соединен с первым входом элемента И/И-НЕ делителя, выход Отказ первого триггера счетчика

0 импульсов соединен с входом элемента НЕ, с первым входом первой структуры И первого элемента 2И-ИЛЙ, с первым входом второй структуры И первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с первым входом чет5 вертого элемента И и с первым входом первого элемента ИЛИ/ЙЛИ-НЕ, выход элемента НЕ делителя соединен с вторым входом первой структуры Л первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом

0 первого элемента И, выход Отказ второго триггера счетчика импульсов соединен с вте- рым входом четвертого элемента И и с вторым входом первого элемента ИЛИ/ИЛИ-НЕ, выход четвертого элемента И соединен с пер5 вым входом третьего элемента ИЛИ, инверсный выход первого элемента ИЛИ/ИЛИ-НЕ соединен с вторым входом первой структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй

0 структуры И первого элемента 2И-ИЛИ прямой выход первого элемента ИЛИ/ИЛИ-НЕ соединен с первым входом второй структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ, с первым входом первой

5 структуры И второго элемента 2И-ИЛИ, с первым входом пятого элемента И и с первым входом второго элемента ИЛИ/ИЛИ- НЕ, выход Отказ третьего триггера счетчика импульсов соединен с вторыми

0 входами шестого элемента И и второго элемента ИЛИ/ИЛИ-НЕ, выход шестого элемента И соединен с вторым входом третьего элемента ИЛИ, инверсный выход второго элемента ИЛИ/ИЛИ-НЕ соединен с вторым

5 входом первой структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй структуры И второго элемента 2И-ИЛИ, прямой выход второго элемента ИЛИ/ИЛИ-НЕ соединен с первым входов

0 второй структуры И третьего элемента 2И

ИЛИ/2И-ИЛИ-НЕ, с первым входом первой

структуры И третьего элемента 2И-ИЛ, и с

первыми входами седьмого элемента И v

третьего элемента ИЛИ/ИЛИ-НЕ, выход От5 каз четвертого триггера счетчика импульсов соединен с вторыми входами третьего элемента ИЛИ/ИЛИ-НЕ и седьмого элемента И выход которого соединен с третьим входом третьего элемента ИЛИ, инверсный выход третьего элемента ИЛ И/ИЛИ-НЕ соединен с

вторым входом первой структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй структуры И ретьего элемента 2И-ИЛИ, прямой выход третьего элемента ИЛИ/ИЛИ-НЕ соединен с первым входом второй структуры И четвертого элемента 2И-И7Ш/2И-ИЛИ-НЕ, с первыми входами восьмого элемента И и четвертого элемента ИЛИ/ИЛИ-НЕ, с вторым входом второго элемента И и с вторым входом первой структуры И пятого элемента 2И-ИЛИ/2И- ИЛИ-НЕ, выход Отказ основного триггера соединен с вторыми входами четвертого элемента ИЛИ/ИЛИ-НЕ и восьмого элемента И, выход которого соединен с четвертым входом третьего элемента ИЛИ, инверсный выход четвертого элемента ИЛИ/ИЛИ-НЕ соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ и с вторым входом первого элемента И-НЕ и с первым входом второй структуры И пятого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход четвертого элемента ИЛИ/ИЛИ-НЕ соединен с первым входом второй структуры И пятого элемента 2И-ИЛИ, с первым входом второго элемента И-НЕ и с первыми входами девятого элемента И и пятого элемента ИЛИ/ИЛИ-НЕ, выход Отказ дополнительного триггера соединен с вторыми входами пятого элемента ИЛИ/ИЛИ-НЕ и девятого элемента И, выход которого соединен с пятым входом третьего элемента ИЛИ, инверсный выход пятого элемента ИЛИ/ИЛИ-НЕ соединен с вторым входом первой структуры И шестого элемента 2И- ИЛИ, с вторым входом третьего элемента И- НЕ и с первым входом третьего элемента И, прямой выход пятого элемента ИЛИ/ИЛИ- НЕ соединен с первым входом второй структуры И шестого элемента 2И-ИЛИ и с первыми входами десятого элемента И и второго элемента ИЛИ, выход Отказ резервного триггера соединен с вторыми входами второго элемента ИЛИ и десятого элемента И, выход которого соединен с шестым входом третьего элемента ИЛИ, выход второго элемента ИЛИ является выходом Частичный отказ делителя, прямой выход элемента И/И-НЕ делителя соединен с первым входом третьего элемента И-НЕ, инверсный выход элемента И/И-НЕ соединен со счетным входом резервного триггера, выход четвертого элемента 2И-ИЛИ соединен с вторым входом элемента И/И-НЕ и с D-вхо- дом резервного триггера, выход четвертого элемента И-НЕ является информационным выходом делителя, выход третьего элемента ИЛИ является выходом Отказ делителя.

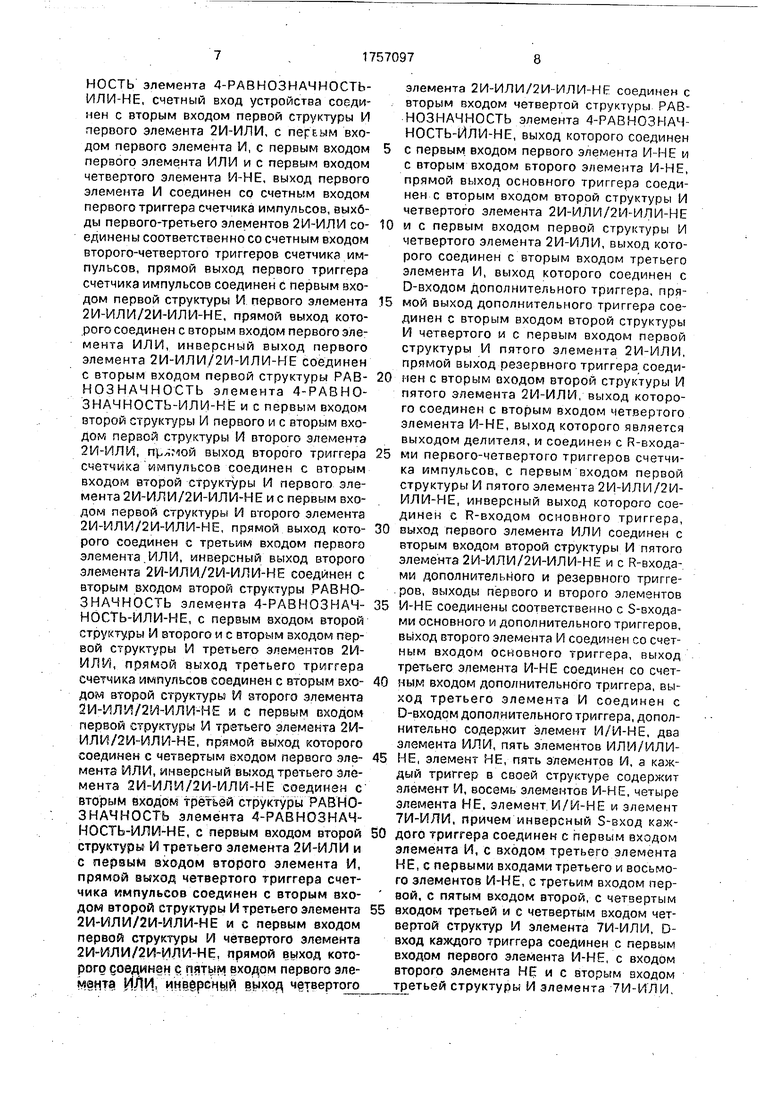

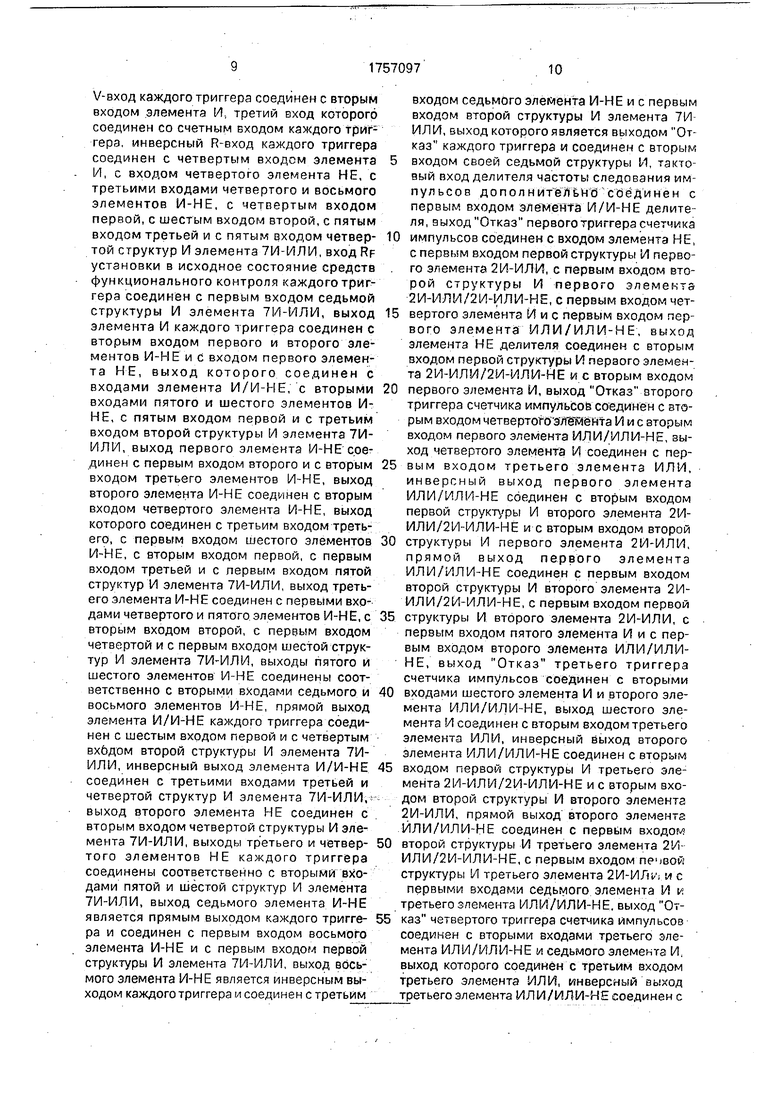

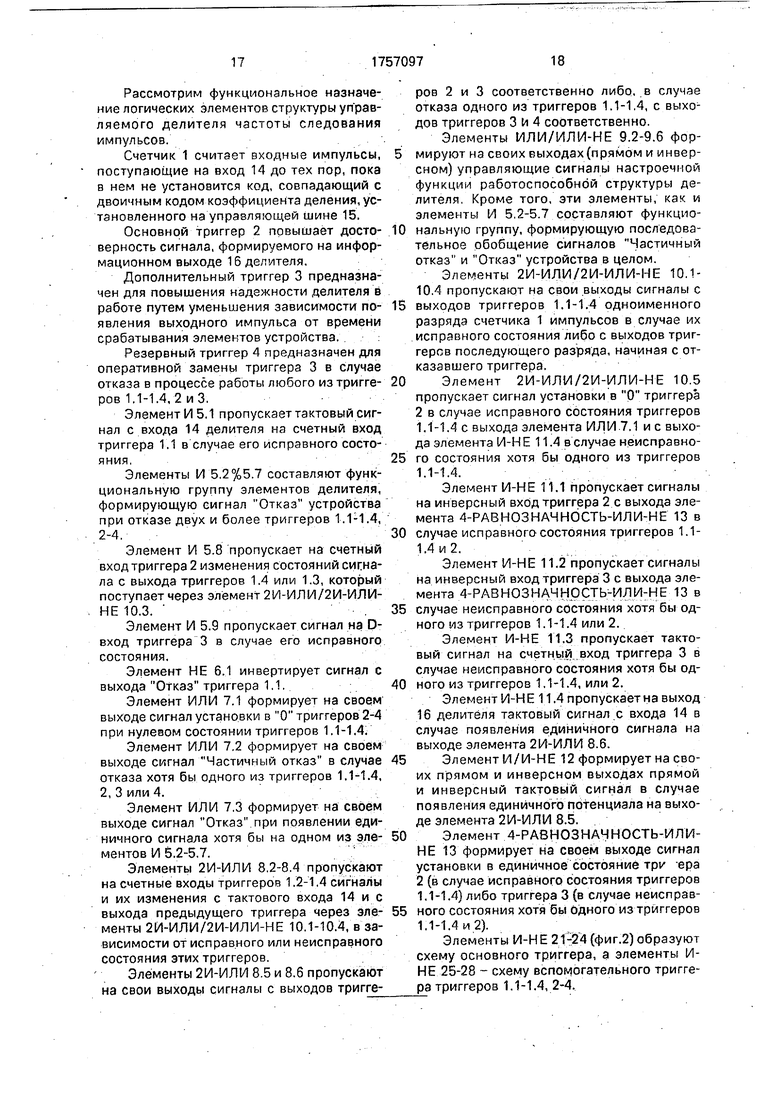

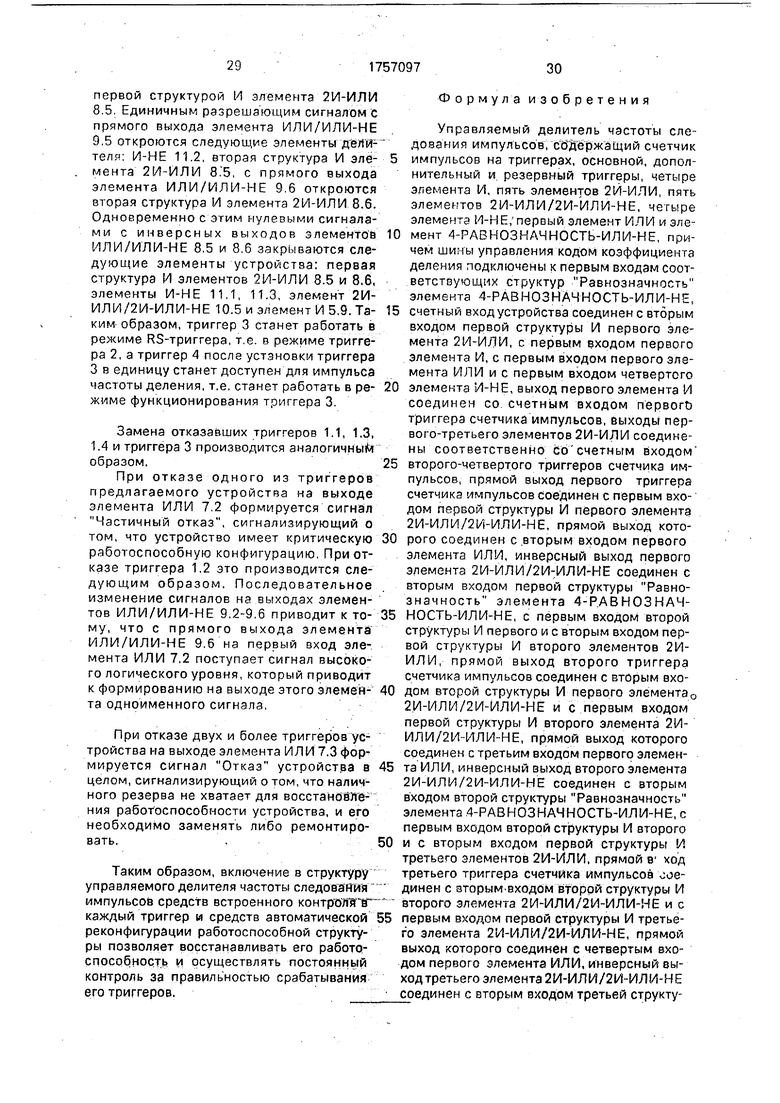

На фиг. 1 приведена структурная схема предла/аемр.го делителя чадтоты следова

й

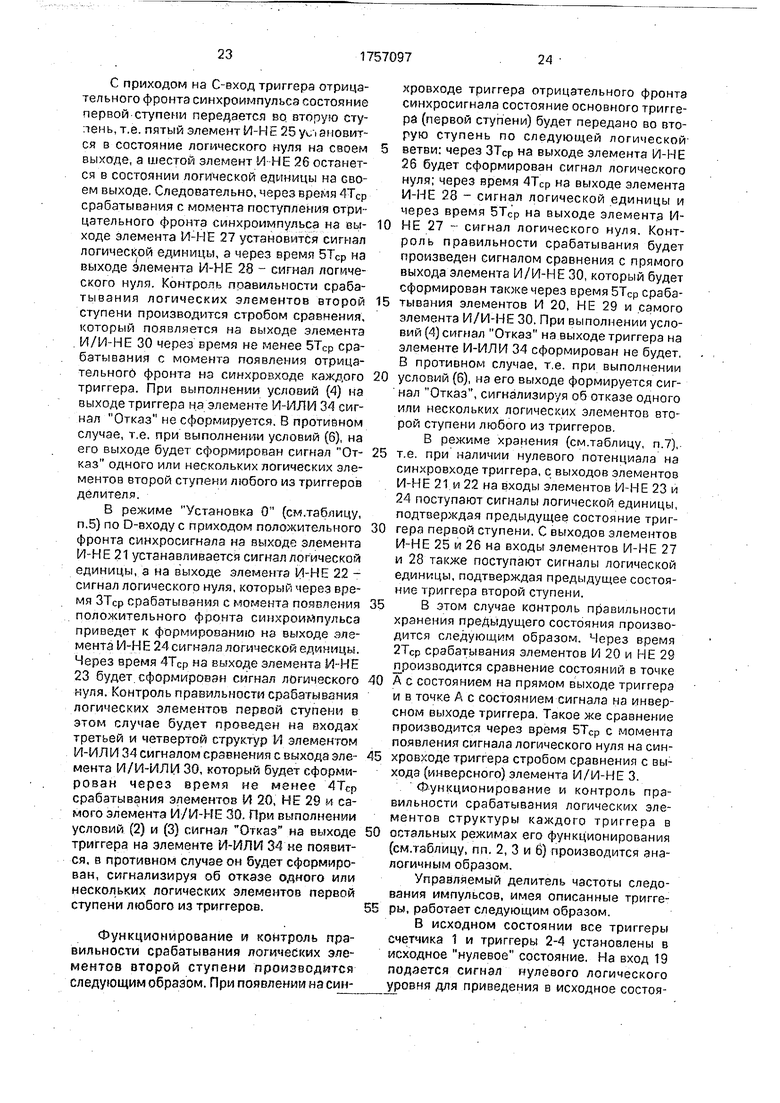

ния импульсов; на фиг. 2 - функциональная схема каждого триггера; ча фиг 3 - временные диаграмма работы каждого триггера.

Управляемый делитель частоты следования импульсов содержит счетчик 1 импульсов с триггерами 1.1-1.4, основной 2, дополнительный 3 и резервный 4 триггеры, элементы И 5.1-5.9. элемент НЕ б 1, элемен- 10 ты ИЛИ 7.1-7.3, элементы 2И-ИЛИ 82-8.6, элементы ИЛИ/ИЛИ-НЕ 9.2-9.6, элементы 2И-ИЛИ/2И-ИЛИ-НЕ 10.1-10.5, элементы И-НЕ 11.1-11.4, элемент И/И-НЕ 12, элемент 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13.

15 Тактовый вход 14 соединен с первым входом элемента И/И-НЕ 12, с вторым входом первой структуры И элемента 2И-ИЛИ 8,2, с первым входом элемента И 5.1, с первым входом элемента ИЛИ 7.1 и с первым

20 входом элемента И-НЕ 11.4.

Вход 15 управления кодом деления частоты следования импульсов соединен соответственно с соответствующими первыми входами структур РАВНОЗНАЧНОСТЬ эле25 мента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13.

Выход элемента И 5.1 соединен со счетным входом триггера 1.1, прямой выход которого соединен с первым входом первой

структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.1, прямой выход которого соединен с вторым входом элемента ИЛИ 7.1. Выход Отказ триггера 1.1 соединен с входом элемента НЕ 8.1, с первым входом второй

структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.1, с первым входом первой структуры И элемента 2И-ИЛИ 8.1, с первым входом элемента И 5.2 и с первым входом элемента ИЛИ/ИЛИ-НЕ 9.2. Выход элемента НЕ 6.1

соединен с вторым входом первой структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.1 и с вторым входом элемента И 5.1. Инверсный выход элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.1 соединен с вторым входом первой

структуры РАВНОЗНАЧНОСТЬ элемента 4- РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13, с первым входом второй структуры И элемента 2И- ИЛИ 8.2 и с вторым входом первой структуры И элемента 2И-ИЛИ 8.3.

Выход элемента 2И-И ПИ 8.2 соединен со счетным входом триггера 1,2, прямой выход которого соединен с вторым входом второй структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.1 и с первым входом первой структуры И

элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.2. Выход Отказ триггера 1.2 соединен с вторым входом элемента И 5.2 и с вторым входом элемента ИЛИ/ИЛИ-НЕ 9.2. Выход элемента И 5.2 соединен с первым входом элемента ИЛИ 7.3. Инверсный выход элемента

ИЛИ/ИЛИ-НЕ 9.2 соединен с вторым входом первой структуры И элемента 2И- ИЛИ/2И-ИЛИ-НЕ 10.2 и с вторым входом второй структуры И элемента 2И-ИЛИ 8.2. Прямой выход элемента ИЛИ/ИЛИ-НЕ 9,2 соединен с первым входом первой структуры И элемента 2И-ИЛИ 8.3, с первым входом элемента И 5.3, с первым входом элемента ИЛИ/ИЛИ-НЕ 9.3 и с первым входом второй структуры И элемента 2И- ИЛИ/2И-ИЛИ-НЕ 10.2, прямой выход которого соединен с третьим входом элемента ИЛИ 7.1. Инверсный выход элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.2 соединен с вторым входом второй структуры РАВНО- ЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧ- НОСТЬ-ИЛИ-НЕ 13, с первым входом второй структуры И элемента 2И-ИЛИ 8.3 и с вторым входом первой структуры И элемента 2И-ИЛИ 8.4.

Выход элемента 2И-ИЛИ 8.3 соединен со счетным входом триггера 8.3, прямой выход которого соединен с вторым входом второй структуры И элемента 2И-ИЛИ/2И- ИЛИ-НЕ 10.2 и с первым входом первой структуры И элемента 2И-ИЛИ/2 И-ИЛИ-НЕ 10.3 Выход Отказ триггера 1.3 соединен с вторым входом элемента И 5.3 и с вторым входом элемента ИЛИ/ИЛИ-НЕ 9.3, инверсный выход которого соединен с вторым входом второй структуры И элемента 2И- ИЛИ 8.3 и с вторым входом первой структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.3. Выход элемента И 5.3 соединен с вторым входом элемента ИЛИ 7.3. Прямой выход элемента ИЛИ/ИЛИ-НЕ 9.3 соединен с первым входом первой структуры И элемента 2И-ИЛИ 8.4, с первым входом элемента И 5.4, с первым входом элемента ИЛИ/ИЛИ- ИЕ 9.4 и с первым входом второй структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.3, прямой выход которого соединен с четвертым входом элемента ИЛИ 7.1. Инверсный выход элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.3 соединен с вторым входом третьей струк- туры РАВНОЗНАЧНОСТЬ элемента 4-РАВ- НОЗНАЧНОСТЬ-ИЛИ-НЕ 13, с первым входом второй структуры И элемента 2И- ИЛИ 8.4 и с первым входом элемента И 5.8.

Выход элемента 2И-ИЛИ 8 4 соединен со счетным входом триггера 1.4, прямой выход которого соединен с вторым входом второй структуры И элемента 2И-ИЛИ/2И- ИЛЙ-НЕ 10.3 и с первым входом первой струк- туры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.4. Выход Отказ триггера 1.4 соединен с вторым входом элемента ИЛИ/ИЛИ-НЕ 9.4 и вторым входом элемента И 5.4, выход которого соединен с третьим входом элемента

ИЛИ 7.3. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 9.4 соединен с вторым входом второй группы входов элемента 2И-ИЛИ 8.4 и с вторым входом первой структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.4. Прямой выход элемента ИЛИ/ИЛИ-НЕ 9.4 соединен с вторым входом элемента И 5.8, с вторым входом первой структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.5, с первым входом элемента И 5.5, с первым входом элемента ИЛИ/ИЛИ-НЕ 9.5 и с первым входом второй структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.4, прямой выход которого соединен с пятым входом элемента ИЛИ 7.1. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 10.4 соединен с вторым входом четвертой структуры РАВНОЗНАЧНОСТЬ элемента 4- РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13.

Выход элемента И-НЕ 11.1 соединен с инверсным S-входом триггера 2, счетный вход которого соединен с выходом элемента И 5.8. Выход элемента2И-ИЛИ/2И-ИЛИ-НЕ 10.5 соединен с инверсным R-входом триггера 2, прямой выход которого соединен с вторым входом второй структуры И элемента 2И-ИЛИ/2И-ИЛ И-НЕ 10.4 и с первым входом первой структуры И элемента 2И-ИЛИ

8.5.Выход Отказ триггера 2 соединен с вторым входом элемента ИЛИ/ИЛИ-НЕ 9.5 и с вторым входом элемента И 5.5, выход которого соединен с четвертым входом элемента ИЛИ 7.3, Инверсный выход элемента ИЛИ/ИЛИ-НЕ 9.5 соединен с вторым входом элемента И-НЕ 11.1, с первым входом второй структуры И элемента 2И-ИЛИ/2И- И Л И-НЕ 10.5 и с вторым входом первой структуры И элемента 2И-ИЛИ 8.5. Прямой выход элемента ИЛ И/ИЛ И-НЕ 9.5 соединен с первым входом элемента И-НЕ 11.2, с первым входом элемента И 5.6, с первым входом элемента ИЛИ/ИЛИ-НЕ 9.6 и с первым входом второй структуры И элемента 2И- ИЛИ 8.5, выход которого соединен с вторым входом элемента И/И-НЕ 12 и с вторым входом элемента И 5.9.

Прямой выход элемента И/И-НЕ 12 соединен с первым входом элемента И-НЕ 11.3, выход которого соединен со счетным входом триггера 3. Выход элемента И-НЕ 11.2 соединен с инверсным S-входом тэиг- гера 3, D-вход которого соединен с вых- юм элемента И 5.9. Прямой выход триггера 3 соединен с вторым входом второй структуры И элемента 2И-ИЛИ 8.5 и с первым входом первой группы входов элемента 2И-ИЛИ

8.6.Выход Отказ триггера 3 соединен с вторым входом элемента ИЛИ/ИЛИ-НЕ 9.6 и с вторым входом элемента И 5.6, выход кбто- рого соединен с пятым входом элемента

ИЛИ 7,3. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 9.6 соединен с вторым вхо- цом элемента И-НЕ 11.3, с первы / входом элемента И 5,9 и с вторым входом первой структуры И элемента 2И-ИЛИ 8,6. Прямой выход элемента ИЛИ/ИЛИ-НЕ9.бсоединен с первым входом элемента И 5,7, с первым входом элемента ИЛИ 7.2 и с первым входом второй структуры И элемента 2И-ИЛИ 8,6, выход которого соединен с вторым входом элемента И-НЕ 11.4.

Инверсный выход элемента И/И-НЕ 12 соединен со счетным входом триггера 4, прямой выход которого соединен с вторым входом второй структуры И элемента 2И- ИЛИ 8.6, Выход Отказ триггера 4 соединен с вторым входом элемента ИЛИ 7.2 и с вторым входом элемента И 5.7, выход которого соединен с шестым входом элемента ИЛИ 7.3. Выход элемента ИЛ И 7.1 соединен с вторым входом второй структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.5 и с инверсными Ro-входами триггеров 3 и 4.

Выход элемента И-НЕ 11.4 является ин- формационным выходом 16 делителя и соединен с первым входом первой структуры И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.5 и с инверсными Ro-входами триггеров 1.1-1.4. Выход элемента ИЛИ 7,2 является выходом 17 Частичный отказ делителя, Выход элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13 соединен с первым входом элемента И-НЕ 11.1 и с вторым входом элемента И-НЕ 11.2. Выход элемента ИЛИ 7.3 является выходом 18 Отказ делителя. Вход 19 установки в исходное состояние средств функционального контроля делителя соединен с Rp-входами триггеров 1.1-1.4, 2-4.

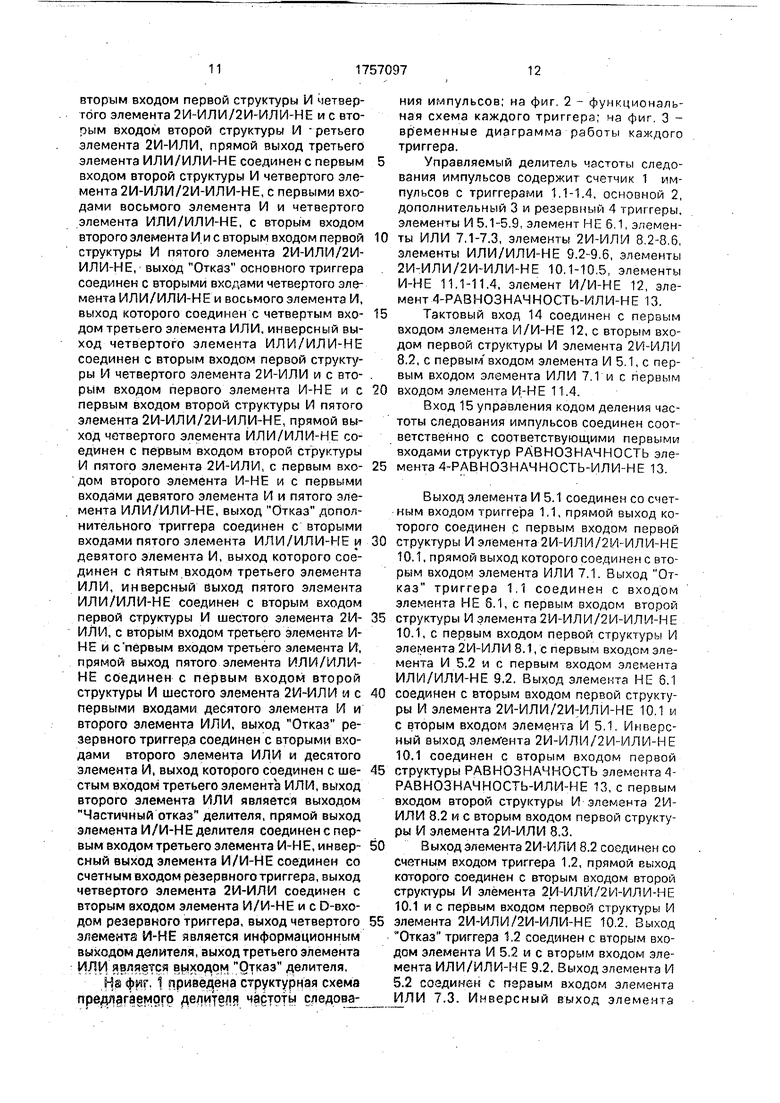

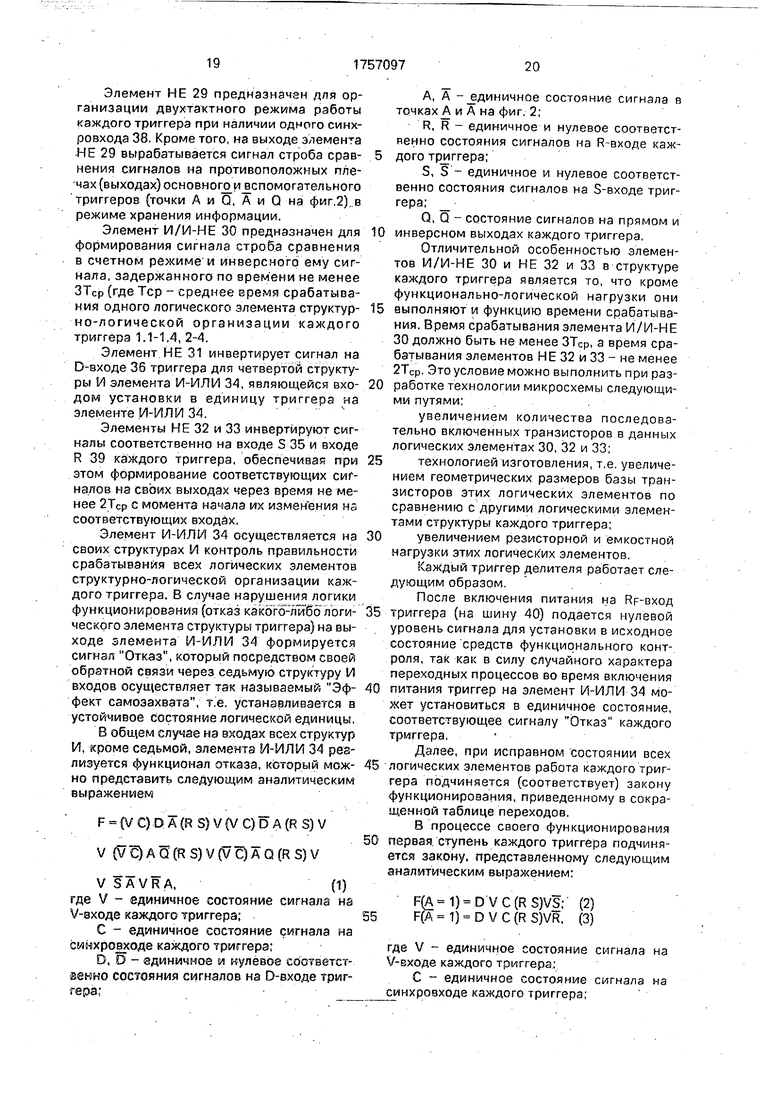

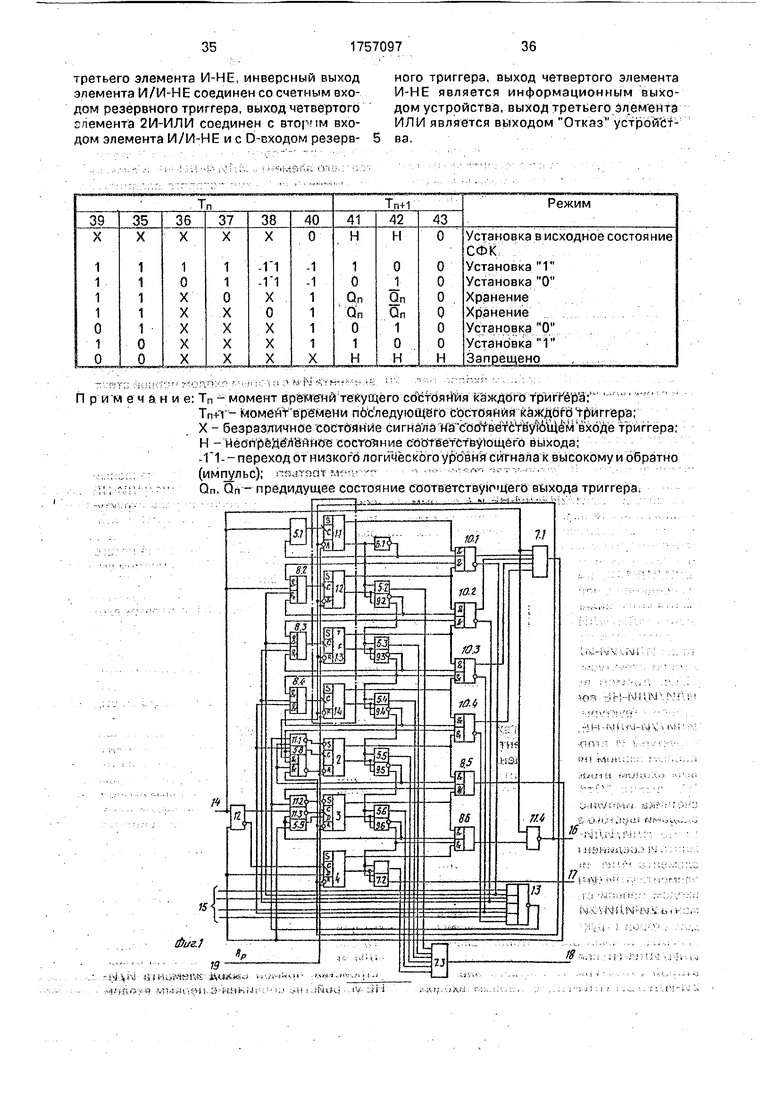

Каждый триггер (фиг.2) содержит элемент И 20, элементы И-НЕ 21-28, элементы НЕ 29, 31-33, элемент И/И-НЕ 30 и элемент 7И-ИЛИ 34.

Инверсный S-вход 35 каждого триггера соединен с первым входом элемента И 20, с входом элемента НЕ 32, с первыми входами элементов И-НЕ 23 и 27, с третьим входом первой, с пятым входом второй, с четвертым входом третьей и с пятым входом четвертой структур И элемента 7И-ИЛИ 34.

D-вход 36 каждого триггера соединен с первым входом элемента И-НЕ 21, с входом элемента НЕ 31 и с вторым входом третьей структуры И элемента 7И-ИЛИ 34.

V-вход 37 и счетный вход 38 каждого триггера соединены соответственны с вторым и третьим входами элемента И 20.

Ro-вход 39 каждого триггера соединен с четвертым входом элемента И 20, с входом элемента НЕ 33, с третьими входами элементов И-НЕ 24 и 28, с четвертым входом

первой, с шестым входом второй, с пятым входом третьей и с пятым входом четвертой структуры И элемента 7И-ИЛИ 34.

Rp-вход 40 каждого триггера соединен с

первым входом седьмой структуры И элемента 7И-ИЛИ 34.

Выход элемента И 20 соединен с вторым входом элемента И-НЕ 21, с вторым

входом элемента И-НЕ 22 и с входом элемента НЕ 29, выход которого соединен с входами элемента И/И-НЕ 30, с вторыми входами элементов И-НЕ 25 и 26, с пятым входом первой и с третьим входом второй

структур И элемента 7И-ИЛИ ЗА.

Выход элемента И-НЕ 21 соединен с вторым входом элемента И-НЕ 23 и с первым входом элемента И-НЕ 22, выход которого соединен с вторым входом элемента

И-НЕ 24.

Выход элемента И-НЕ 23 соединен с первым входом элемента И-НЕ 25, с вторым входом второй, с первым входом четвертой, с первым входом шестой структур И элемента 7И-ИЛИ 34 и с первым входом элемента И-НЕ 24, выход которого соединен с третьим входом элемента И-НЕ 23, с первым входом элемента И-НЕ 26, с вторым входом первой, с первым входом третьей и с первым входом пятой структур И элемента 7Й- ИЛИ 34.

Выходы элементов И-НЕ 25 и 26 соединены соответственно с вторыми входами элементов И-НЕ 27 и 28.

Прямой выход элемента И/И-НЕ 30 соединен с шестым входом первой и с четвертым входом второй структур И элемента 7И-ИЛИ 34. Инверсный выход элемента И/И-НЕ 30 соединен с третьим входом

третьей и с третьим входом четвертой структур И элемента 7И-ИЛИ 34.

Выход элемента НЕ 31 соединен с вторым входом четёертой структуры И элемента 7И-ИЛИ 34. Выходы элементов НЕ 32 и

33 соединены соответственно с вторыми входами пятой и шестой структур И элемента 7И-ИЛИ 34.

Выход элемента И-НЕ 27 является пря- мым выходом 40 каждого триггера и соединен с первым входом элемента И-НЕ 28 и с первым входом первой структуры И элемента 7И-ИЛИ 34. Выход элемента И-НЕ 28 является инверсным выходом 41 каждого триггера и соединен с третьим входом элемента И-НЕ 27 и с первым входом второй структуры И элемента 7И-ИЛИ 34, выход которого является выходом 42 Отказ каждого триггера и соединен с вторым входом своей седьмой структуры И.

Рассмотрим функциональное назначение логических элементов структуры управляемого делителя частоты следования импульсов.

Счетчик 1 считает входные импульсы, поступающие на вход 14 до тех пор, пока в нем не установится код, совпадающий с двоичным кодом коэффициента деления, установленного на управляющей шине 15.

Основной триггер 2 повышает досто- верность сигнала, формируемого на информационном выходе 16 делителя.

Дополнительный триггер 3 предназначен для повышения надежности делителя в работе путем уменьшения зависимости по- явления выходного импульса от времени срабатывания элементов устройства.

Резервный триггер 4 предназначен для оперативной замены триггера 3 в случае отказа в процессе работы любого из тригге- ров 1.1-1.4,2 иЗ.

Элемент И 5.1 пропускает тактовый сигнал с входа 14 делителя на счетный вход триггера 1.1 в случае его исправного состояния,

Элементы И 5.2%5.7 составляют функциональную группу элементов делителя, формирующую сигнал Отказ устройства при отказе двух и более триггеров 1.1-1.4, 2-4.

Элемент И 5.8 пропускает на счетный вход триггера 2 изменения состояний сигнала с выхода триггеров 1.4 или 1.3, который поступает через элемент 2И-ИЛИ/2И-ИЛИ- НЕ 10.3.

Элемент И 5.9 пропускает сигнал на D- вход триггера 3 в случае его исправного состояния.

Элемент НЕ 6.1 инвертирует сигнал с выхода Отказ триггера 1,1.

Элемент ИЛИ 7.1 формирует на своем выходе сигнал установки в О триггеров 2-4 при нулевом состоянии триггеров 1.1-1.4.

Элемент ИЛИ 7,2 формирует на своем выходе сигнал Частичный отказ в случае отказа хотя бы одного из триггеров 1,1-1.4, 2, 3 или 4.

Элемент ИЛИ 7.3 формирует на своем выходе сигнал Отказ при появлении единичного сигнала хотя бы на одном из эле- ментов И 5.2-5.7.

Элементы 2И-ИЛИ 8.2-8.4 пропускают на счетные входы триггеров 1.2-1.4 сигналы и их изменения с тактового входа 14 и с выхода предыдущего триггера через эле- менты 2И-ИЛИ/2И-ИЛИ-НЕ 10.1-10.4, в зависимости от исправного или неисправного состояния этих триггеров.

Элементы 2И-ИЛИ 8.5 и 8.6 пропускают на свои выходы сигналы с выходов триггеров 2 и 3 соответственно либо, в случае отказа одного из триггеров 1.1-1,4, с выходов триггеров 3 и 4 соответственно.

Элементы ИЛИ/ИЛИ-НЕ 9.2-9.6 формируют на своих выходах (прямом и инверсном) управляющие сигналы настроечной функции работоспособной структуры делителя, Кроме того, эти элементы, как и элементы И 5.2-5.7 составляют функциональную группу, формирующую последовательное обобщение сигналов Частичный отказ и Отказ устройства в целом.

Элементы 2И-ИЛИ/2И-ИЛИ-НЕ 10.1- 10.4 пропускают на свои выходы сигналы с выходов триггеров 1,1-1.4 одноименного разряда счетчика 1 импульсов в случае их исправного состояния либо с выходов триггеров последующего разряда, начиная с отказавшего триггера.

Элемент 2И-ИЛИ/2И-ИЛИ-НЕ 10.5 пропускает сигнал установки в О триггера 2 в случае исправного состояния триггеров 1.1-1.4 с выхода элемента ИЛИ 7.1 и с выхода элемента И-НЕ 11.4 в случае неисправного состояния хотя бы одного из триггеров 1.1-1.4.

Элемент И-НЕ 11.1 пропускает сигналы на инверсный вход триггера 2 с выхода элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13 в случае исправного состояния триггеров 1.1- 1.4 и 2.

Элемент И-НЕ 11.2 пропускает сигналы на инверсный вход триггера 3 с выхода элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13 в случае неисправного состояния хотя бы одного из триггеров 1.1-1.4 или 2.

Элемент И-НЕ 11.3 пропускает тактовый сигнал на счетный вход триггера 3 в случае неисправного состояния хотя бы одного из триггеров 1,1-1.4, или 2.

Элемент И-Н Е 11.4 пропускает на выход 16 делителя тактовый сигнал с входа 14 в случае появления единичного сигнала на выходе элемента 2И-ИЛИ 8.6.

Элемент И/И-НЕ 12 формирует на своих прямом и инверсном выходах прямой и инверсный тактовый сигнал в случае появления единичного потенциала на выходе элемента 2И-ИЛИ 8.5.

Элемент 4-РАВНОЗНАЧНОСТЬ-ИЛИ- НЕ 13 формирует на своем выходе сигнал установки в единичное состояние три -ера 2 (в случае исправного состояния триггеров 1,1-1.4) либо триггера 3 (в случае неисправного состояния хотя бы одного из триггеров 1.1-1.4 и 2).

Элементы И-НЕ 21-24 (фиг.2) образуют схему основного триггера, а элементы И- НЕ 25-28 - схему вспомогательного триггера триггеров 1.1-1.4, 2-4.

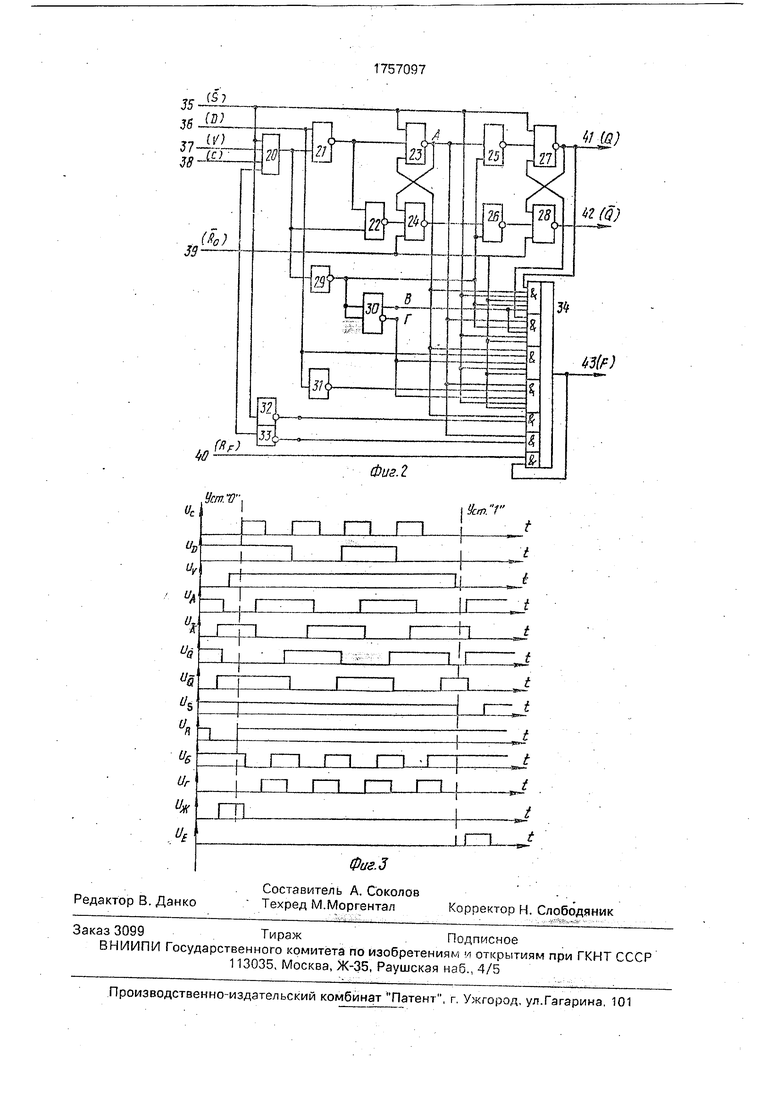

Элемент НЕ 29 предназначен для организации двухтактного режима работы каждого триггера при наличии одного синх- ровхода 38. Кроме того, на выходе элемента НЕ 29 вырабатывается сигнал строба сравнения сигналов на противоположных плечах (выходах) основной) и спомогательного триггеров (точки А и Q, А и Q на фиг.2) в режиме хранения информации.

Элемент И/И-НЕ 30 предназначен для формирования сигнала строба сравнения в счетном режиме и инверсного ему сигнала, задержанного по времени не менее ЗТСр (где Тер - среднее время срабатывания одного логического элемента структурно-логической организации каждого триггера 1.1-1,4, 2-4.

Элемент НЕ 31 инвертирует сигнал на D-входе 36 триггера для четвертой структуры И элемента И-ИЛИ 34, являющейся входом установки в единицу триггера на элементе И-ИЛИ 34.

Элементы НЕ 32 и 33 инвертируют сигналы соответственно на входе S 35 и входе R 39 каждого триггера, обеспечивая при этом формирование соответствующих сигналов на своих выходах через время не менее 2ТСр с момента начала их изменения на соответствующих входах.

Элемент И-ИЛИ 34 осуществляется на своих структурах И контроль правильности срабатывания всех логических элементов структурно-логической организации каждого триггера. В случае нарушения логики функционирования (отказ какого-либо логического элемента структуры триггера) на выходе элемента И-ИЛИ 34 формируется сигнал Отказ, который посредством своей обратной связи через седьмую структуру И входов осуществляет так называемый Эффект самозахвата, т.е. устанавливается в устойчивое состояние логической единицы.

В общем случае на входах всех структур И, кроме седьмой, элемента И-ИЛИ 34 реализуется функционал отказа, который можно представить следующим аналитическим выражением

F - (V С) D A (R S) V (V С) D A (R S) V V (VC)AQ(RS)V(VC)AQ(RS}V

V SAVR А,(1)

где V - единичное состояние сигнала на V-входе каждого триггера;

С - единичное состояние сигнала на синхровходе каждого триггера;

D, D - единичное и кулевое соответственно состояния сигналов на D-входе триггера1

А, А - единичное состояние сигнала в точках А и А на фиг. 2;

R, R - единичное и нулевое соответственно состояния сигналов на R-входе каж- дого триггера;

S, S - единичное и нулевое соответственно состояния сигналов на S-входе триггера;

Q, Q - состояние сигналов на прямом и инверсном выходах каждого триггера,

Отличительной особенностью элементов И/И-НЕ 30 и НЕ 32 и 33 в структуре каждого триггера является то, что кроме функционально-логической нагрузки они выполняют и функцию времени срабатывания. Время срабатывания элемента И/И-НЕ 30 должно быть не менее ЗТСр, а время срабатывания элементов НЕ 32 и 33 - не менее 2Тср. Это условие можно выполнить при раз- работке технологии микросхемы следующими путями:

увеличением количества последовательно включенных транзисторов в данных логических элементах 30, 32 и 33; технологией изготовления, т.е увеличением геометрических размеров базы транзисторов этих логических элементов по сравнению с другими логическими элементами структуры каждого триггера; увеличением резисторной и емкостной нагрузки этих логических элементов

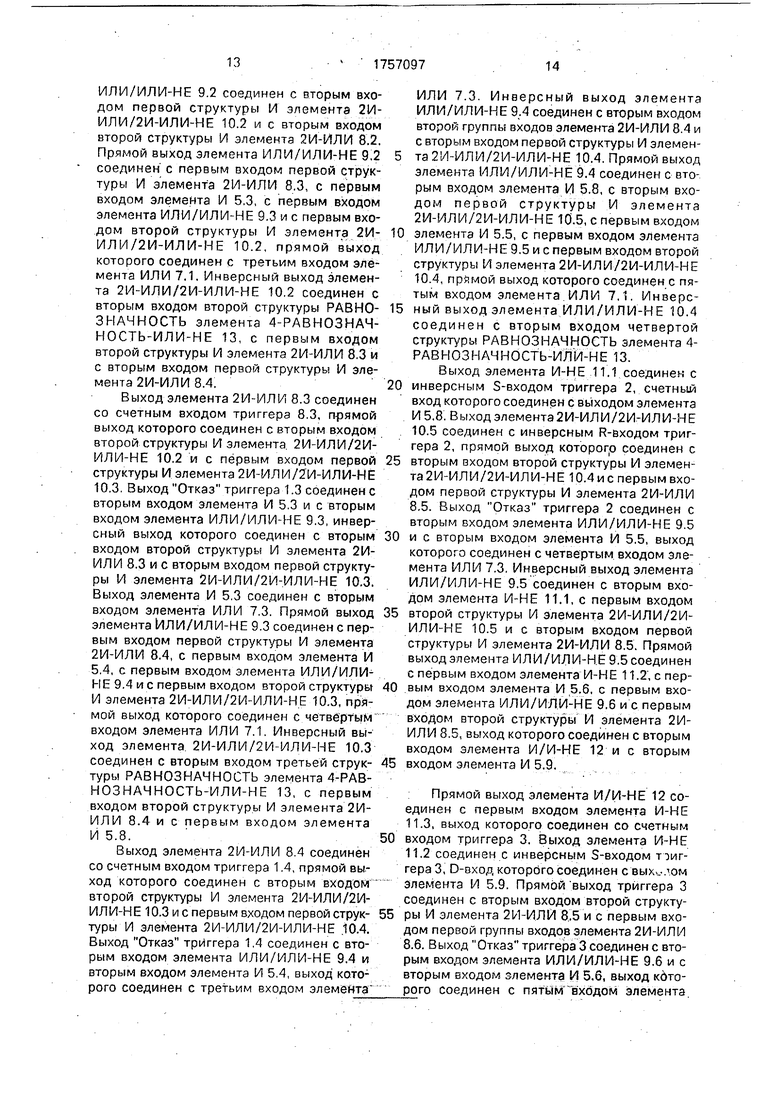

Каждый триггер делителя работает следующим образом

После включения питания на Rp-вход триггера (на шину 40) подается нулевой уровень сигнала для установки в исходное состояние средств функционального контроля, так как в силу случайного характера переходных процессов во время включения питания триггер на элемент И-ИЛИ 34 может установиться в единичное состояние, соответствующее сигналу Отказ каждого триггера,

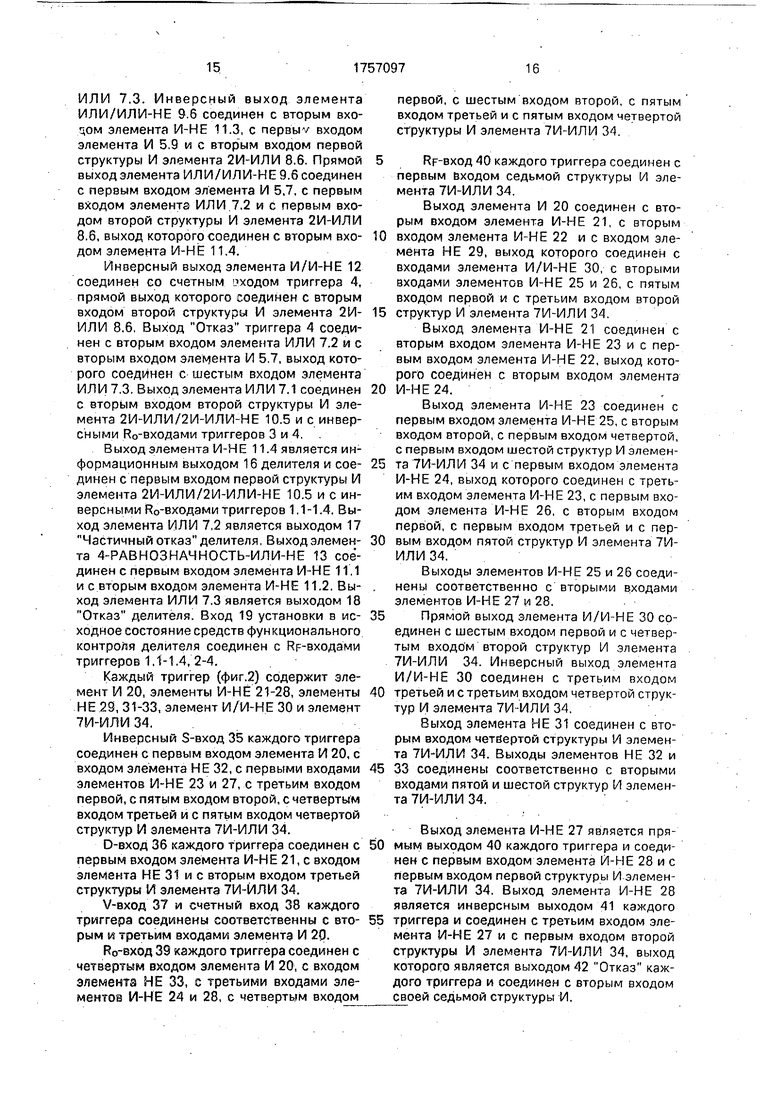

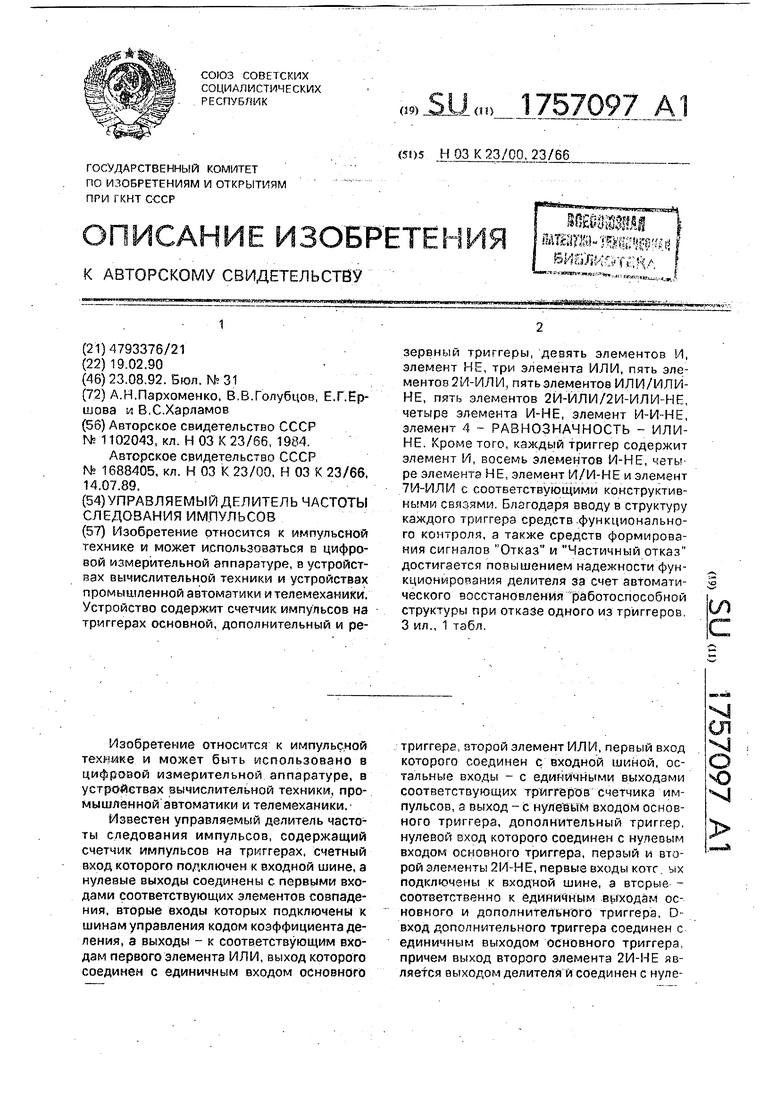

Далее, при исправном состоянии всех логических элементов работа каждого триггера подчиняется (соответствует) закону функционирования, приведенному в сокращенной таблице переходов,

В процессе своего функционирования первая ступень каждого триггера подчиняется закону, представленному следующим аналитическим выражением:

F()DVC(RS)VS; (2) F(A 1) D V С (R S)VR. (3)

где V - единичное состояние сигнала на V-входе каждого триггера:

С - единичное состояние сигнала на синхровходе каждого триггера;

D, D - единичное и нулевое соответственно состояния сигналов нэ D-входе каждого триггера;

А, А - состояние сигналов в точках А и А на фиг.2 каждого триггера;

R, R - единичное и нулевое соответственно состояния сигналов на R-входе каждого триггера;

S, S - единичное и нулевое соответственно состояния сигналов на S-входе каждого триггера.

За выполнением условий выражений (2) и (3) следят третья и четвертая структуры И элемента И-ИЛИ 34.

В процессе своего функционирования вторая ступень (вспомогательный триггер) каждого триггера подчиняется закону, который можно представить следующим аналитическим выражением:

(VC)AQ(RS)(VC)AQ(RS)1 (4)

где V, С - единичное состояние сигнала на выходе элемента НЕ 30 каждого триггера;

Q, Q - состояние сигналов на прямом и инверсном соответственно выходах каждого триггера,

За выполнением условий выражения (4) следят первая и вторая структуры И элемента И-ИЛИ 34.

Функционал отказа любого из логических элементов первой ступени (основного триггера), реализованный в каждом триггере, можно представить следующим аналитическим выражением:

F (V С) D A (R S) V (V С) D A (R S). (5)

В случае нарушения условий функционирования, представленных е выражениях (2) и (3), на выходе элемента И-ИЛИ 34 уже в момент срабатывания логических элементов первой ступени вырабатывается сигнал Отказ любого из триггеров.

Функционал отказа любого из логических элементов второй ступени (вспомогательного триггера), реализованный в техническом решении каждого триггера, можно представить следующим выражением:

F (VC)AQ(RS)V(VC)AQ(RS). (6)

В случае нарушения условий функционирования, представленных в выражении (4), на выходе элемента И-ИЛИ 34 также вырабатывается сигнал Отказ любого из триггеров делителя.

Асинхронный режим функционирования каждого триггера контролируется пятой- и шестой структурами И элемента И-ИЛИ 34. Режим установки 1 контролирует пятая структура И, режим установки О - шестая структура И элемента И-ИЛИ 34. Характерной особенностью этого режима является то, что установка основного и вспомогательного триггеров структуры каж- 5 дого триггера осуществляется одновременно. Вот почему строб сравнения на выходах элементов НЕ 32 и 33 вырабатывается через время не менее 2ТСр, т.е. через время срабатывания элементов И-НЕ 23 и 24, а также

0 элементов И-НЕ 27 и 28. В случае правильного срабатывания всех элементов ни шестая, ни седьмая структуры И не пропустят на свой выход высокий логический уровень сигнала и на выходе элемента И-ИЛИ 34 сигнал

5 Отказ не будет сформирован. В противном случае такой сигнал будет сформирован и он будет означать, что при асинхронной установке триггера в О или 1 произошел отказ какого-либо логического элемента

0 структуры каждого триггера.

Рассмотрим последовательность срабатывания всех элементов логической структуры каждого триггера в его трех основных режимах синхронного функционирования5 хранение,установка установка О.

В Установка 1 (см.таблицу) по D-входу с поступлением положительного фронта синхросигнала на С-вход триггера на выходе первого элемента И-НЕ 21 через

0 время 2Тср срабатывания элементов И 20, И-НЕ 21 установится сигнал логического нуля, Следовательно, через время ЗТСр срабатывания с момента поступления положительного фронта сигнала на С-вход

5 на выходах второго и третьего элементов И-НЕ 22 и 23 установятся сигналы логической единицы и через время 4ТСр срабатывания на выходе четвертого элемента И-НЕ 24 - сигнал логического нуля, Таким обра0 зом через время 4Тср вточке А(фиг.2)будето установлено состояние логической единицы, а вточке А-состояние логического нуля. Контроль правильности срабатывания логических олементов первой ступени каждого

5 триггера осуществляется стробом сравнения с инверсного выхода элемента И/И-НЕ 30, который появляется также через время не менее 4Тср срабатывания элементов И 20, НЕ 29 и самого элемента И/И-НЕ 30.

0 Если входе контроля будет выполнено условие (2) и (3), то третья и четвертая струк уры И элемента И-ИЛИ 34 не пропустят на его выход сигнал логической единицы. При нарушении алгоритма функционирования ло5 гическими элементами первой ступени выполнится условие (4), на выходе однофазного триггера на элементе И-ИЛИ 34 вырабатывается сигнал логической единицы, сигнализируя об отказе первой ступени любого из триггеров делителя.

С приходом на С-вход триггера отрицательного фронта синхроимпульса состояние первой ступени передается во вторую сту- 1ень, т.е. пятый элемент И-Ht 25у.лановит ся в состояние логического нуля на своем выходе, а шестой элемент И НЕ 26 останется в состоянии логической единицы на своем выходе. Следовательно, через время 4ТСр срабатывания с момента поступления отрицательного фронта синхроимпульса на выходе элемента И-НЕ 27 установится сигнал логической единицы, а через время 5ТСр на выходе элемента И-НЕ 28 - сигнал логического нуля. Контроль поавильиости срабатывания логических элементов второй ступени производится стробом сравнения, который появляется на выходе элемента И/И-НЕ 30 через время не менее 5ТСр срабатывания с момента появления отрицательного фронта на синхровходе каждого триггера. При выполнении условий (4) на выходе триггера на элементе И-ИЛИ 34 сигнал Отказ не сформируется. В противном случае, т.е. при выполнении условий (6), на его выходе будет сформирован сигнал Отказ одного или нескольких логических элементов второй ступени любого из триггеров делителя,

В режиме Установка 0 {см.таблицу, п.5} по D-входу с приходом положительного фронта синхросигнала на выходе элемента И-НЕ 21 устанавливается сигнал логической единицы, а на выходе элемента И-НЕ 22 - сигнал логического нуля, который через время ЗТср срабатывания с момента появления положительного фронта синхроимпульса приведет к формированию на выходе элемента И-НЕ 24сигнала логической единицы. Через время 4ТСр на выходе элемента И-НЕ 23 будет сформирован сигнал логического нуля. Контроль правильности срабатывания логических элементов первой ступени в этом случае будет проведен на входах третьей и четвертой структур И элементом И-ИЛИ 34 сигналом сравнения с выхода элемента И/И-ИЛИ 30, который будет сформирован через время не менее 4ТСр срабатывания элементов И 20, НЕ 29 и самого элемента И/И-НЕ 30. При выполнении условий (2) и (3) сигнал Отказ на выходе триггера на элементе И-ИЛИ 34 не появится, в противном случае он будет сформирован, сигнализируя об отказе одного или нескольких логических элементов первой ступени любого из триггеров.

Функционирование и контроль правильности срабатывания логических элементов второй ступени производится следующим образом. При появлении на сиихровходе триггера отрицательного фронта синхросигнала состояние основного триггера (первой ступени) будет передано во вторую ступень по следующей логической

ветви: через ЗТСр на выходе элемента И-НЕ 26 будет сформирован сигнал логического нуля; через время 4ТСр на выходе элемента И-НЕ 28 - сигнал логической единицы и через время 5Тср на выходе элемента И0 НЕ 27 - сигнал логического нуля. Контроль правильности срабатывания будет произведен сигналом сравнения с прямого выхода элемента И/И-НЕ 30, который будет сформирован также через время 5Тср сраба5 тывания элементов И 20, НЕ 29 и самого элемента И/И-НЕ 30. При выполнении условий (4) сигнал Отказ на выходе триггера на элементе И-ИЛИ 34 сформирован не будет, В противном случае, т.е. при выполнении

0 условий (6), на его выходе формируется сигнал Отказ, сигнализируя об отказе одного игш нескольких логических элементов второй ступени любого из триггеров.

В режиме хранения (см.таблицу, п.7),

5 т.е. при наличии нулевого потенциала на синхровходе триггера, с выходов элементов И-НЕ 21 и 22 на входы элементов И-НЕ 23 и 24 поступают сигналы логической единицы, подтверждая предыдущее состояние триг0 гера первой ступени, С выходов элементов И-НЕ 25 и 26 на входы элементов И-НЕ 27 и 28 также поступают сигналы логической единицы, подтверждая предыдущее состояние триггера второй ступени.

5 В этом случае контроль правильности хранения предыдущего состояния производится следующим образом. Через время 2Тср срабатывания элементов И 20 и НЕ 29 производится сравнение состояний в точке

0 А с состоянием на прямом выходе триггера и в А с состоянием сигнала на инверсном выходе триггера. Такое же сравнение производится через время 5Тср с момента появления сигнала логического нуля на син5 хровходе триггера стробом сравнения с выхода (инверсного) элемента И/И-НЕ 3.

Функционирование и контроль правильности срабатывания логических элементов структуры каждого триггера в

0 остальных режимах его функционирования (см.таблицу, пп. 2, 3 и 6} производится аналогичным образом.

Управляемый делитель частоты следования импульсов, имея описанные тригге5 ры, работает следующим образом.

В исходном состоянии все триггеры счетчика 1 и триггеры 2-4 установлены в исходное нулевое состояние. На вход 19 подается сигнал нулевого логического уровня для приведения в исходное состояние средств функционального контроля триггеров. На шинах 15 установлен код, соответствующий выбранному коэффициенту деления. На выходе элемента 4-РАВ- НОЗНАЧНОСТЬ-ИЛИ-НЕ 13 присутствует уровень логического нуля, как и на выходе элемента ИЛИ 7.1.

Коэффициент деления определяется по выражению:

Кя К + 1.

(7)

где К - двоичный код коэффициента деления, поступающий на первые входы структур РАВНОЗНАЧНОСТЬ элемента 13.

В случае исправного состояния триггеров счетчика 1 и триггеров 2, 3, триггер 4 находится в горячем резерве, и сигнал с его прямого выхода заблокирован нулевым логическим сигналом с прямого выхода элемента ИЛИ/ИЛИ-НЕ 9,6, поступающим на первый вход второй структуры И элемента 2И/ИЛИ 8.6. На выходах Отказ триггеров 1.1-1.4, 2-4 присутствуют сигналы логического нуля.

В этом случае деление входных импульсов предлагаемое устройство производит следующим образом,

Так как в случае исправного состояния всех триггеров на их выходах Отказ присутствуют сигналы логического нуля, то открыты элемент И 5.1, вторые структуры И элементов 21/1-ИЛИ 8.2-8.4, элемент И-НЕ 11.1, вторая структура И элемента 2И- ИЛИ/2И-ИЛИ-НЕ 10.5, элемент И-НЕ 11.3, элемент И 5.9, первые структуры И элементов 2И-ИЛИ/2И-ИЛИ-НЕ 10.1-10.4 и первые структуры И элементов 2И-ИЛИ 8.5 и 8.6. Одновременно с этим закрыты первые структуры И элементов 2И-ИЛИ 8.2-8,4, элемент И 5.8, первая структура И элементов 2И-ИЛИ/2И-ИЛИ-НЕ 10.5, вторые структуры И элементов 2И-ИЛИ/2И-ИЛИ-НЕ 10.1- 10.4, 2И-ИЛИ 8.5 и 8.6. В результате этого подсчет входных импульсов производится по следующей логической ветви устройства: с входа 14 устройства через элемент И 5.1 - на счетный вход триггера 1.1; состояние сигнала на прямом выходе триггера 1.1 (и его изменения) через первую структуру И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.1 поступают с его прямого выхода на второй вход элемента ИЛИ 7.1 и с инверсного выхода - на второй вход первой структуры РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧ- НОСТЬ-ИЛИ-НЕ 13, на первый вход второй структуры И элемента 2И-ИЛИ 8.2 и на второй вход первой структуры И элемента 2И- ИЛИ 8,3; так как открыта вторая структура

И элемента 2И-ИЛИ 8.2, то положительный фронт изменения сигнала на инверсном выходе элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.1 будет воздействовать на счетный вхо,с

5 триггера 1.2.

Изменение сигнала на прямом выходе триггера 1.2 через первую структуру И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.2 и вторую структуру И элемента 2И-ИЛИ 8.3 воздейст0 вует на счетный вход триггера 1.3. Изменение сигнала на прямом выходе триггера 1.3 через первую структуру И элемента 2И- ИЛИ/2И-ИЛИ-НЕ 10.3 и вторую структуру И элемента 2И-ИЛИ 8.4 воздействуют нз.счет5 ный вход триггера 1.4,

Счетчик 1 считает входные импульсы до тех пор, пока в нем не установится код, совпадающий с двоичным кодом коэффмци0 ента деления. До этого момента на выходе хотя бы одной из структур РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧНОСТЬ- ИЛИ-НЕ 13 присутствует уровень логической единицы. При установлении в

5 счетчике 1 кода, совпадающего с двоичным кодом коэффициента деления, на выходах всех структур РАВНОЗНАЧНОСТЬ элемента 4-РАВИОЗНАЧНОСТЬ-ИЛИ-НЕ 13 формируются сигналы логического нуля, что

0 приводит к формированию единичного сигнала на выходе элемента 13, который через элемент И-НЕ 11.1 устанавливает в состояние логической единицы триггер 2. Единичный логический уровень сигнала с прямого

5 выхода триггера 2 через первую структуру И элемента 2И-ИЛИ 8.5 и элемент И 5.9 воздействует на D-вход триггера 3 и на второй вход элемента И/И-НЕ 12, в результате чего в момент окончания входного

0 импульса на тактовом входе 14 триггер 3° установится в единичное состояние, которое через первую структуру И элемента 2И- ИЛИ 8.6 будет воздействовать на второй вход элемента И-НЕ 11.4. С приходом оче5 редного входного импульса на выходе элемента И-НЕ 11.4 будет сформирован сигнал нулевого логического уровня, который начинает установку триггеров счетчика 1 в нулевое состояние.

0 Значение сигнала на выходе элемента ИЛ И 7.1 определяется состоянием сиг . лов на выходах триггеров 1.1-1.4 счетчика 1 и значением входного сигнала делителя. При этом, когда на выходнрй шине 16 делителя

5 заканчивается выходной импульс, на выходе элемента ИЛИ 7.1 формируется уровень логического нуля, который устанавливает триггеры 2-4 в нулевое состояние.

В дальнейшем делитель работает аналогично. В результате на выходной шине 16

делителя появляются импульсы с частотой, пропорциональной частоте входных импульсов и обратно пропорциональной двоичному числу плюс единица, код которого установлен на шинах 15 кода управления коэффициентом деления.

Рассмотрим пример восстановления работоспособности устройства при отказе триггера 1.2 счетчика и пример отказа триггера 2 устройства,

В случае отказа триггера 1.2 счетчика 1 на его выходе Отказ формируется сигнал логической единицы, что приводит к смене состояний сигналов на выходах элементов ИЛИ/ИЛИ-НЕ 9,2-9,6. В результате этого на прямых выходах элементов ИЛИ/ИЛИ-НЕ 9,2-9.6 будет сформирован сигнал логиче ской единицы, а на их инверсных выходах - сигнал логического нуля. При этом откроются вторые структуры И элементов 2И- ИЛИ/2И-ИЛИ-НЕ 10,2-10.4, 2И-ИЛИ 8.5 и 8.6 и первые структуры И элементов 2И ИЛИ 8.3 и 8.4, элемент И 5.8, первая структура И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.5, элемент И-НЕ 11.2. Одновременно с этим закрываются следующие логические элементы устройства: вторые структуры И элементов 2И-ИЛ И 8.2-8.4, (заметим, что ос тается закрытой первая структура И элемен та 2И-ИЛЙ 8.2 нулевым сигналом с выхода Отказ триггера 1.1), первые структуры И элементов 2И-ИЛИ/2И-ИЛИ-НЕ 10.2-10,4 и 2И-ИЛИ 8.5 и 8.6, Элемент И-НЕ 11,1. вторая структура И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.5, элемент И-НЕ 11.3 и элемент И 5,9.

При поступлении на вход 14 тактовых импульсов устройство в этом случае работает следующим образом.

С входа 14 устройства импульсы счета через элемент И 5,1 поступают на счетный вход триггера 1.1; состояние сигнала (и его изменения) с прямого выхода триггера 1. через первую структуру И элемента 2И- ИЛИ/2И-ИЛИ-НЕ 10.1 поступаете его прямого выхода на вход элемента ИЛИ 7.1 и с его инверсного выхода - на второй вход первой структуры РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13, на второй вход первой структуры И элемента 2И-ИЛИ 8.3 и через этот элемент - на счетный вход триггера 1,3, На счетный вход триггера 1.2 этот сигнал воздействовать не будет, так как вторая структура И элемента 2И-ИЛИ 8.2 закрыта.

Изменение сигнала на выходе триггера 1.3 через вторую структуру И элемента 2И- ИЛИ/2И-ИЛИ:НЕ 10,2 поступаете его прямого выхода на вход элемента ИЛИ 7.1 и с его инверсного эыхода поступает на второй вход второй структуры РАВНОЗНАЧНОСТЬ

элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13 ичерез первую структуру И элемента 2И-ИЛИ 8.4 на счетный вход триггера 1.4.

Изменение сигнала на выходе триггера 1.4 через вторую структуру И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.3 поступает с его прямого выхода на соответствующий вход элемента ИЛИ 7.1 и с его инверсного

выхода поступает на вход третьей структуры РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ и через первый вход элемента И 5.8 на счетный вход триггера 2.

Изменение сигнала на выходе триггера 2 через вторую структуру И элемента 2И- ИЛИ/2И-ИЛИ-НЕ 10.4 поступает с его прямого выхода н,а вход элемента ИЛИ 7.1 и с его инверсного выхода поступает на вход

четвертой структуры РАВНОЗНАЧНОСТЬ элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 13. Таким образом, триггера 1.2 заменяется триггером 1.3 , триггер 1.3 - триггером 1.4, триггер 1.4 - триггером 2. Так как элемент

И/И-НЕ 12 открыт, то открывается доступ к счетному входу триггера 4, а так как элементы И-НЕ 11.3 и И 5.9 закрыты, то триггер 3 начинает работать как обыкновенный RS- трмггер, т.е. триггер 3 замещает триггер 2, а

триггер 4 - триггер 3.

Далее работа управляемого делителя частоты следования импульсов производится аналогично описанному случаю,

При отказе триггера 2 на его выходе Отказ формируется сигнал единичного логического уровня, что приводит к смене состояний сигналов на прямых и инверсных выходах элементов ИЛИ/ИЛИ-НЕ

9,5 и 9.6. В этом случае на инверсных выходах элементов ИЛИ/ИЛИ-НЕ 9.5 и 9.6 формируются сигналы логического нуля, а на инверсных выходах элементов ИЛИ/ИЛИ-НЕ 9.2-9.4 остаются сигналы

логической единицы. На прямых выходах элементов ИЛИ/ИЛИ-НЕ 9.2-9.4 будут сформированы смгналы логического нуля, а на прямых выходах элементов ИЛИ/ИЛИ-НЕ 9.5 и 9,6 - уровни логической единицы,

В результате этого закроются элемент И-НЕ 11.1 и вторая структура И элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.5, останется закры- тым элемент И 5.8 нулевым сигналом с прямого выхода элемента ИЛИ/ИЛИ-НЕ 9.4, изолировав тем самым по входам триггер 2. Прямой выход триггера 2 будет также изолирован закрытой второй группой входов элемента 2И-ИЛИ/2И-ИЛИ-НЕ 10.4 и

первой структурой И элемента 2И-ИЛИ 8 5 Единичным разрешающим сигналом с прямого выхода элемента ИЛИ/ИЛИ-НЕ 9,5 откроются следующие элементы дтэЛй- теля. И-НЕ 11.2, вторая структура И эле- мента 2И-ИЛИ 8. 5, с прямого выхода элемента ИЛИ/ИЛИ-НЕ 9 6 откроются вторая структура И элемента 2И-ИЛИ 8.6. Одновременно с этим нулевыми сигналами с инверсных выходов элементов ИЛИ/ИЛИ-НЕ 8.5 и 8.6 закрываются следующие элементы устройства: первая структура И элементов 2И-ИЛИ 8.5 и 8.6, элементы И-НЕ 11.1, 11.3, элемент 2И- ИЛИ/2И-ИЛИ-НЕ 10.5 и элемент И 5,9. Та- ким образом, триггер 3 станет работать в режиме RS-триггера, т е. в режиме триггера 2, а триггер 4 после установки триггера 3 в единицу станет доступен для импульса частоты деления, т.е. станет работать в ре- жиме функционирования триггера 3.

Замена отказавших триггеров 1.1, 1.3, 1.4 и триггера 3 производится аналогичный образом.

При отказе одного из триггеров предлагаемого устройства на выходе элемента ИЛИ 7 2 формируется сигнал Частичный отказ, сигнализирующий о том, что устройство имеет критическую работоспособную конфигурацию, При отказе триггера 1,2 это производится следующим образом. Последовательное изменение сигналов на выходах элементов ИЛИ/ИЛИ-НЕ 9.2-9.6 приводит к то- му, что с прямого выхода элемента ИЛИ/ИЛИ-НЕ 9.6 на первый вход элемента ИЛИ 7,2 поступает сигнал высокого логического уровня,который приводит к формированию на выходе этого элемен- та одноименного сигнала,

При отказе двух и более триггеров устройства на выходе элемента ИЛИ 7.3 формируется сигнал Отказ устройства в целом, сигнализирующий о том, что наличного резерва не хватает для восстановления работоспособности устройства, и его необходимо заменять либо ремонтировать..

Таким образом, включение в структуру управляемого делителя частоты следования импульсов средств встроенного контрол ПГ каждый триггер и средств автоматической реконфигурации работоспособной структуры позволяет восстанавливать его работоспособность и осуществлять постоянный контроль за правильностью срабатывания его триггеров.

Формула изобретения

Управляемый делитель частоты следования импульсов, со держащий счетчик импульсов на триггерах, основной, дополнительный и резервный триггеры, четыре элемента И, пять элементов 2И-ИЛИ, пять элементов 2И-ИЛИ/2И-ЙЛИ-НЕ, четыре элемента И-НЕ; первый элемент ИЛИ и элемент 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ, причем шины управления кодом коэффициента деления подключены к первым входам соответствующих структур Равнозначность элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ, счетный вход устройства соединен с вторым входом первой структуры И первого элемента 2И-ИЛИ, с первым входом первого элемента И, с первым входом первого элемента ИЛИ и с первым входом четвертого элемента И-НЕ, выход первого элемента И соединен со счетным входом первого триггера счетчика импульсов, выходы первого-третьего элементов 2И-ИЛИ соединены соответственно со счетным входом второго-четвертого триггеров счетчика импульсов, прямой выход первого триггера счетчика импульсов соединен с первым входом первой структуры И первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход которого соединен с вторым входом первого элемента ИЛИ, инверсный выход первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом первой структуры Равнозначность элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И первого и с вторым входом первой структуры И второго элементов 2Й- ИЛИ, прямой выход второго триггера счетчика импульсов соединен с вторым входом второй структуры И первого элемента0 2И-ИЛИ/2И-ИЛИ-НЕ и с первым входом первой структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ, прямой выход которого соединен с третьим входом первого элемента ИЛИ, инверсный выход второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом второй структуры Равнозначность элемента 4-РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И второго и с вторым входом первой структуры И третьего элементов 2И-ИЛИ, прямой вг ход третьего триггера счетчика импульсов оое- динен с вторым входом второй структуры И второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с первым входом первой структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход которого соединен с четвертым входом первого элемента ИЛИ, инверсный выход третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом третьей структуры Равнозначность элемента 4-РАВНО- ЗИАЧНОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И третьего элемента 2И- ИЛИ и с первым входом второго элемента И, прямой выход четвертого триггера счет- чика импульсов соединен с вторым входом второй структуры И третьего элемента 2И- ИЛИ/2И-ИЛИ-НЕ и с первым входом первой структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход кото- рого соединен с пятым входом первого элемента ИЛИ, инверсный выход четвертого элемента 2И-ИЛИ/2И- Х ЛИ-НЕ соединен с вторым входом четвертой структуры Равнозначность элемента 4-РАВНОЗНАЧ- НОСТЬ-ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И-НЕ и с вторым входом второго элемента И-НЕ, прямой выход основного триггера соединен с вторым входом второй структуры И чет вер- того элемента 2И-ИЛИ/2И-ИЛ И-НЕ и с первым входом первой стоуктуры И четвертого элемента 2И-ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с D-еходом до- полнительного триггера, прямой выход дополнительного триггера соединен с вторым входом второй структуры И четвертого и с первым входом первой структуры И пятого элемента 2И-ИЛИ, прямой выход резервно- го триггера соединен с вторым входом второй структуры И пятого элемента 2И-ИЛИ, выход которого соединен с вторым входом четвертого элемента И-НЕ, выход которого является выходом делителя и соединен с R-входами первого-четвертого триггера счетчика импульсов, с первым входом первой структуры И пятого элемента 2И- ИЛИ/2Й-ИЛИ-НЕ, инверсный выход которого соединен с R-входом основного триггера, выход первого элемента ИЛИ соединен с вторым входом второй структуры И пятого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с R-входами дополнительного и резервного триггеров, выходы первого и второго элемента И-НЕ соединены соответственно с S-входами основного м дополнительного триггеров, выход второго элемента И соединен со счетным входом основного триггера, выход третьего элемента И-НЕ соединен со счетным входом дополнительного триггера, выход третьего элемента И соединен с D-входом дополнительного триггера, о т личающийся тем, что, с целью повышения эксплуатационной отказоустойчиеости, в него введены элемент И/И-НЕ, два элемента ИЛИ, пять элементов ИЛИ/ИЛИ-НЕ, элемент НЕ, пять элементов И, а каждый триггер в своей структуре содержит элемент И, восемь элементов И-НЕ, четыре элемента

НЕ, элемент И/И-НЕ и элемент 7И-ИЛИ причем инверсный S-вход каждого триггера соединен с первым входом элемента И, с входом третьего элемента НЕ, с первыми входами третьего и седьмого элементов И- НЕ, с третьим входом первой, с пятым входом второй, с четвертым входом третьей и четвертой структур И элемента 7И-ИЛИ, D- вход каждого триггера соединен с первым входом первого элемента И-НЕ, с входом второго элемента НЕ и с вторым входом третьей структуры И элемента 7И-ИЛИ, V- вход каждого триггера соединен с вторым входом элемента И, третий вход которого соединен со счетным входом каждого триггера, инверсный R-вход каждого триггера соединен с четвертым входом элемента И, с входом четвертого элемента НЕ, с третьими входами четвертого и восьмого элементов И-НЕ, с четвертым входом первой, с шестым входом второй, с пятым входом третьей и с пятым входом четвертой структур И элемента И-ИЛИ, вход установки в исходное состояние средств функционального контроля каждого триггера соединен с первым входом седьмой структуры 1/ элемента 7И-ИЛИ, выход элемента И каждого триггера соединен с вторым входом первого и второго элементов И-НЕ и с входом первого элемента НЕ, выход которого соединен с входами элемента И/И-НЕ, с вторыми входами пятого и шестого элементов И-ИЕ, с пятым входом первой и с третьим входом второй структуры И элемента 7И-ИЛИ, выход первого элемента И-НЕ соединен с первым входом второго и с вторым входом третьего элементов И-НЕ, выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ, выход которого соединен с третьим входом третьего, с первым входом шестого элемента И-НЕ, с вторым входом первой, с первым входом третьей и пятой структур И элемента 7И- ИЛИ, выход третьего элемента И-НЕ соединен с первыми входами четвертого и пятого элементов И-НЕ, с вторым входом второй, с первыми входами четвертой и шестой структур И элемента 7И-ИЛИ, выходы пятого и шестого элементов И-НЕ соединены соответственно с вторыми входами седьмого и восьмого элементов И-НЕ, прямой выход элемента И/И-НЕ каждого триггера соединен с шестым входом первой и с четвертым входом второй структур И элемента 7И- ИЛИ, инверсный выход элемента И/И-НЕ соединен с третьими входами третьей и четвертой структур И элемента 7И-ИЛИ, выход второго элемента НЕ соединен с вторым входом четвертой структуры И элемента 7И- ИЛИ, выходы третьего и четвертого элемента НЕ каждого триггера соединены соответственно с вторыми входами пятой и шестой структуры И элемента 7И-ИЛИ, выход седьмого элемента И-НЕ является прямым выходом каждого триггера и соединен с первым входом восьмого эпементз И-НЕ и с первым входом первой структуры И элемента 7И-ИЛИ, выход восьмого элемента И-НЕ является инверсным выходом каждого триггера и соединен с третьим входом седьмого элемента И-НЕ и с первым входом второй структуры И элемента 7И-ИЛИ, выход которого является выходом Отказ каждого триггера и соединен с вторым входом своей седьмой структуры И, тактовый вход делителя частоты следования импульсов дополнительно соединен с первым входом элемента И/И-НЕ устройства, выход Оказ первого триггера счетчика импульсов соединен с входом элемента НЕ, с первым входом первой структуры И первого элемента 2И-ИЛИ, с первым входом второй структуры И первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ с первым входом четвертого элемента И и с первым входом первого элемента ИЛИ/ИЛИ-НЕ, выход элемента НЕ устройства соединен с вторым входом первой структуры И первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом первого элемента И, выход Отказ второго триггера счетчика импульсов соединен с вторым входом четвертого элемента И и с вторым входом первого элемента ИЛИ/ИЛИ-НЕ, выход четвертого элемента И соединен с первым входом третьего элемента ИЛИ, инверсный выход первого элемента ИЛИ/ИЛИ-НЕ соединен с вторым входом первой структуры И второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй структуры И первого элемента 2И- ИЛИ, прямой выход первого элемента ИЛИ/ИЛИ-НЕ соединен с первым входом второй структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ, с первым входом первой структуры И второго элемента 2И-ИЛИ, с первым входом пятого элемента И и с первым входом второго элемента ИЛИ/ИЛИ- НЕ, выход Отказ третьего триггера счетчика импульсов соединен с вторыми входами шестого элемента И и второго элемента ИЛИ/ИЛИ-НЕ, выход шестого элемента И соединен с вторым входом третьего элемента ИЛИ, инверсный выход второго элемента ИЛИ/ИЛИ-НЕ соединен с вторым входом первой структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй структуры И второго элемента 2И-ИЛИ, прямой выход второго элемента ИЛИ/ИЛИ-НЕ соединен с первым входом второй структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с первым входом

первой структуры И третьего элемента 2И- ИЛИ и с первыми входами седьмого элемен та И -л третьего элемента ИЛИ/ИЛИ-НЕ, выход Отказ четвертого триггера счетчика 5 импульсов соединен с вторыми входами третьего элемента ИЛИ/ИЛИ-НЕ и седьмо го элемента И, выход которого соединен с третьим входом третьего элемента ИЛИ, ни версный выход третьего элемента

0 ИЛИ/ИЛИ-НЕ соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с вторым входом второй структуры И третьего элемента 2И-ИЛИ, прямой выход третьего элемента

5 ИЛИ/ИЛИ-НЕ соединен с первым вхЪдом второй структуры И четвертого элемента 2И-ИЛИ-НЕ/2И-ИЛИ, с первыми входами восьмого элемента И и четвертого элемента ИЛИ/ИЛИ-НЕ, с вторым входом второго

0 элемента И и с вторым входом первой структуры И пятого элемента 2И-ИЛИ/2И-ИЛИ- НЕ, выход Отказ основного триггера соединен с вторыми входами четвертого элемента ИЛИ/ИЛИ-НЕ и восьмого элемен5 та И, выход которого соединен с четвертым входом третьего элемента ИЛИ, инверсный выход четвертого элемента ИЛИ/ИЛИ-НЕ соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ, с вто0 рым входом первого элемента И-НЕ и с первым входом второй структуры И пятого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход четвертого элемента ИЛИ/ИЛИ-НЕ соединен с первым входом второй структуры

5 И пятого элемента 2И-ИЛИ, с первым входом второго элемента И-НЕ и с первыми входами восьмого элемента И и пятого элемента ИЛИ/ИЛИ-НЕ, выход Отказ дополнительного триггера соединен с это0 рыми входами пятого элементао ИЛИ/ИЛИ-НЕ и восьмого элемента И, выход которого соединен с пятым входом третьего элемента ИЛИ, инверсный выход пятого элемента ИЛИ/ИЛИ-НЕ соединен с

5 вторым входом первой структуры И шестого элемента 2И-ИЛИ, с вторым входом третьего элемента И-НЕ и с первым входом третьего элемейта И, прямой выход пятого элемента ИЛИ/ИЛЙ-НЕ соединен с

0 первым входом второй структуры И шестого элемента 2И-ИЛИ и с первыми входами девятого элемента И и второго злем чта ИЛИ, выход Отказ резервного триггера соединен с вторыми входами второго эле5 мента ИЛИ и девятого элемента И, выход которого соединен с шестым входом третьего элемента ИЛИ, выход второго элемента ИЛИ является выходом Частичный отказ устройства, прямой выход элемента И/И- НЕ устройства соединен с первым входом

третьего элемента И-НЕ инверсный выход элемента И/И-НЕ соединен со счетным входом резервного триггера, выход четвертого олемента 2И-ИЛИ соединен с вторим входом элемента И/И-НЕ и с D-сходом резерв-

ного триггера, выход четвертого элемента И-НЕ является информационным выходом устройства, выход третьего элемента ИЛИ является выходом Отказ устрой ст

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1688405A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

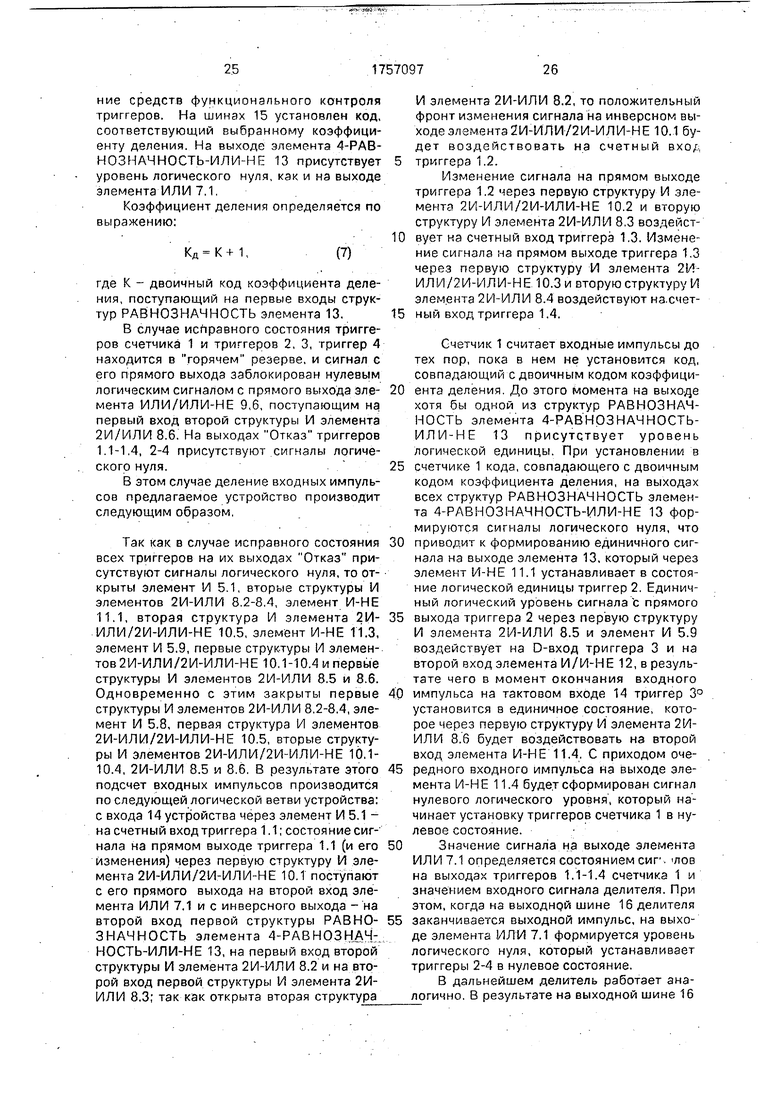

Изобретение относится к импульсной технике и может использоваться в цифровой измерительной аппаратуре, в устройствах вычислительной техники и устройствах промышленной автоматики и телемеханики. Устройство содержит счетчик импульсов на триггерах основной, дополнительный и резервный триггеры, девять элементов И, элемент НЕ, три элемента ИЛИ, пять элементов 2И-ИЛ И, пять элементов ИЛИ/ИЛИ- НЕ, пять элементов 2И-ИЛИ/2И-ИЛИ-НЕ, четыре элемента И-НЕ, элемент И-И НЕ, элемент 4 - РАВНОЗНАЧНОСТЬ - ИЛИ- НЕ Кроме того, каждый триггер содержит элемент И, восемь элементов Й-НЕ, четы ре элемента НЕ, элемент И/И-НЕ и элемент 7И-ИЛИ с соответствующими конструктивными связями Благодаря вводу в структуру каждого триггера средств функционального контроля, а также средств формирования сигналов Отказ и Частичный отказ достигается повышением надежности функционирования делителя за счет автоматического восстановления работоспособной структуры при отказе одного из триггеров 3 ил., 1 табл (Л

1г ч

Примечание: Тп- момент времени текущего состояния каждого триггера1;

Тп+i - момейт времени последующего состояния каждый триггера; X - безразличное состояние сигнала Нй соо гве-г вуШДёй входе триггера- Н - неопределённое состояние соответствующего выхода; Г1- - переход от низкого логического уровня сигнала к высокому и обратно (импульс), Qn, Qn - предидущее состояние соответствующего выхода триггера

.« . г 19

j i i u «j , i « , .k 1 о u , iЧ S

IJ | i

,Mi

Л ixlnPJ

- tП ,., ч

сн-да

L-J , J

1 t J , N tin

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1688405A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-23—Публикация

1990-02-19—Подача