Изобретение относится к электрической связи и может использоваться в регенераторах и оконечных станциях цифровых систем связи совместно с элементами тракта хронирования.

Известное устройство синхронизации регенераторов и оконечных станций систем с временным уплотнением содержит последовательно соединенные преобразователь, дифференцирующий блок, формирователь стробов, элемент задержки и решающий блок, к другим входам которого подключен вход преобразователя.

Однако известное устройство обладает низкой помехоустойчивостью.

Цель изобретения - повышение помехоустойчивости.

Для этого в устройство синхронизации регенераторов и оконечных станций систем с временным уплотнением, содержащее последовательно соединенные преобразователь, дифференцирующий блок, формирователь стробов, элемент задержки и решающий блок, к другим входам которого подключен вход преобразователя, введен анализатор моментов регистрации сигналов, при этом информационный вход анализатора моментов регистрации сигналов соединен с входом преобразователя, тактовый вход - с выходом формирователя стробов, а выход анализатора моментов регистрации сигналов подключен к управляющему входу элемента задержки. Кроме того, анализатор моментов регистрации сигналов содержит блок задержки, вы.ходы которого, кроме одного, через последовательно соединенные блок сравнения, блок накопителей и блок сумматоров подключены к входам делителя напрял.ения, причем один из выходов блока задержки через элемент задержки подключен к входу расширителя импульсов, один

выход которого подключен к входам блока сумматоров и делителя напрял ения, а другой выход - к другому входу блока сумматоров, кроме того, выпрямитель подключен к информационным входам блока сравнения, причем

вход выпрямителя является информационным входом анализатора моментов регистрации сигналов, вход блока задерл ки - тактовым входом, а выход делителя напряжения - выходом анализатора моментов регистрации

сигналов.

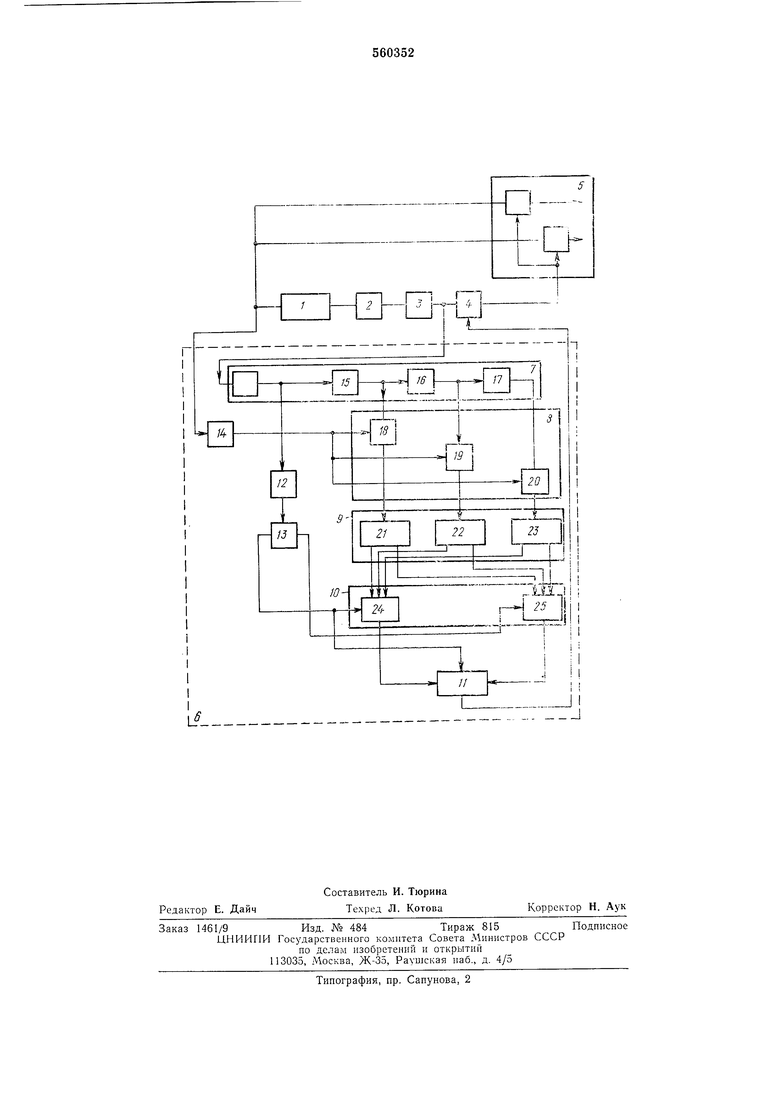

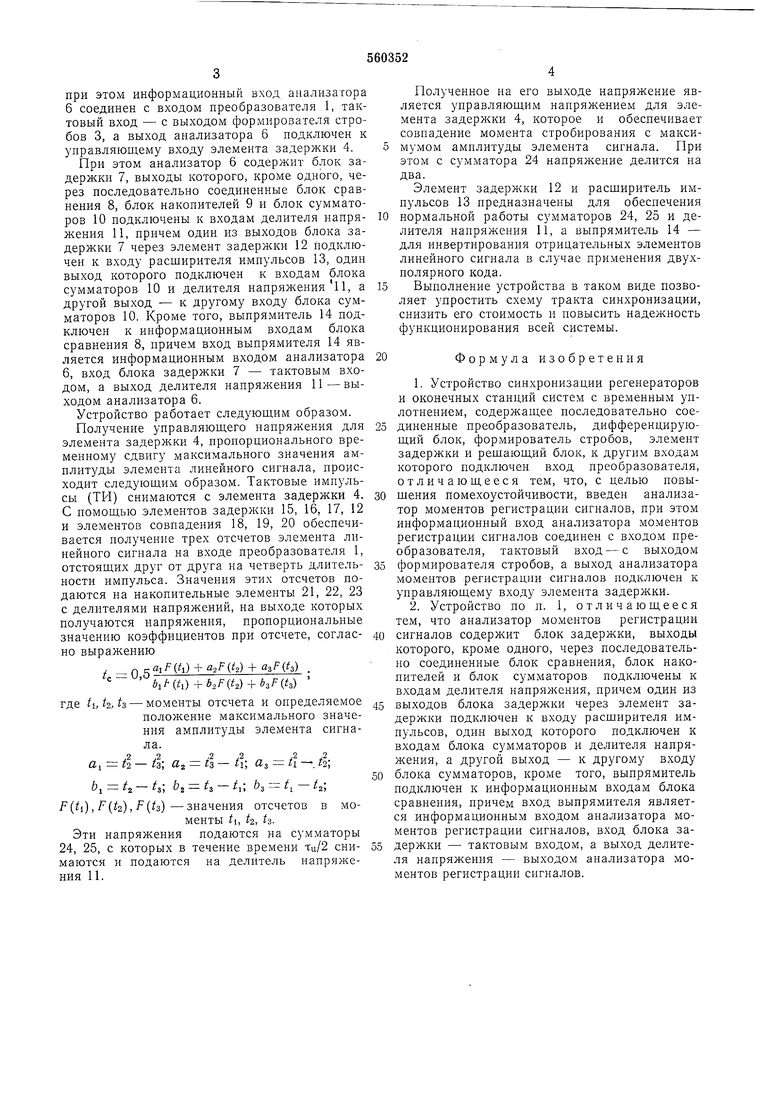

На чертеже представлена структурная электрическая схема предложенного устройства. Устройство содержит последовательно соединенные преобразователь 1, дифференцирующий блок 2, формирователь стробов 3, элемент задержки 4 н решаюший блок 5, к другим входам которого подключен вход преобразователя 1. Устройство содержит также

анализатор 6 моментов регистрации сигналов, при этом информационный вход анализатора 6 соединен с входом преобразователя 1, тактовый вход - с выходом формирователя стробов 3, а выход анализатора 6 подключен к управляющему входу элемента задержки 4. При этом анализатор 6 содержит блок задержки 7, выходы которого, кроме одного, через последовательно соединенные блок сравнения 8, блок накопителей 9 и блок сумматоров 10 подключены к входам делителя напряжения 11, причем один из выходов блока задержки 7 через элемент задержки 12 подключен к входу расширителя импульсов 13, один выход которого подключен к входам блока сумматоров 10 и делителя напряженияИ, а другой выход - к другому входу блока сумматоров 10. Кроме того, выпрямитель 14 подключен к информационным входам блока сравнения 8, причем вход выпрямителя 14 является информационным входом анализатора 6, вход блока задержки 7 - тактовым входом, а выход делителя напряжения 11 - выходом анализатора 6. Устройство работает следующим образом. Получение управляющего напряжения для элемента задержки 4, пропорционального временному сдвигу максимального значения амплитуды элемента линейного сигнала, происходит следующим образом. Тактовые имиульсы (ТИ) снимаются с элемента задержки 4. С помощью элементов задержки 15, 16, 17, 12 и элементов совпадения 18, 19, 20 обеспечивается получение трех отсчетов элемента линейного сигнала на входе преобразователя 1, отстоящих друг от друга на четверть длительности импульса. Значения этих отсчетов подаются на накопительные элементы 21, 22, 23 с делителями напряжений, на выходе которых получаются напряжения, пропорциональные значению коэффициентов при отсчете, согласно выражению п ,;aifft)) + fl3f(3) . - и,О , , ,,, , ,, „ , , , ,,, I 6,/-(1)(У + 6з(« где гьГвДз -моменты отсчета и определяемое положение максимального значения амплитуды элемента сигнала. 222 992 ui з; a - h i; из 1 . 2; b.t - гз; &2 3 - i ,- /2; F(ti), F(t2), F{t3)-значения отсчетов в моменты ti, tz, ti. Эти напряжения подаются на сумматоры 24, 25, с которых в течение времени ти/2 снимаются и подаются на делитель напряжения 11. Полученное на его выходе напряжение является управляющим напряжением для элемента задержки 4, которое и обеспечивает совпадение момента стробирования с максимумом амплитуды элемента сигнала. При этом с сумматора 24 напряжение делится на два. Элемент задержки 12 и расщиритель импульсов 13 предназначены для обеспечения нормальной работы сумматоров 24, 25 и делителя напряжения 11, а выпрямитель 14 - для инвертирования отрицательных элементов линейного сигнала в случае применения двухполярного кода. Выполнение устройства в таком виде позволяет упростить схему тракта синхронизации, снизить его стоимость и повысить надежность функционирования всей системы. Формула изобретения 1. Устройство синхронизации регенераторов и оконечных станций систем с временным уплотнением, содержащее последовательно соединенные преобразователь, дифференцирующий блок, формирователь стробов, элемент задержки и решающий блок, к другим входам которого подключен вход преобразователя, отличающееся тем, что, с целью повыщения помехоустойчивости, введен анализатор моментов регистрации сигналов, при этом информационный вход анализатора моментов регистрации сигналов соединен с входом преобразователя, тактовый вход - с выходом формирователя стробов, а выход анализатора моментов регистрации сигналов подключен к управляющему входу элемента задержки. 2. Устройство по п. 1, отличающееся тем, что анализатор моментов регистрации сигналов содержит блок задержки, выходы которого, кроме одного, через последовательно соединенные блок сравнения, блок накопителей и блок сумматоров подключены к входам делителя напряжения, причем один из выходов блока задержки через элемент заержки подключен к входу расширителя импульсов, один выход которого подключен к входам блока сумматоров и делителя напряжения, а другой выход - к другому входу блока сумматоров, кроме того, выпрямитель одключен к информационным входам блока равнения, причем вход выпрямителя являетя информационным входом анализатора моентов регистрации сигналов, вход блока заержки - тактовым входом, а выход делитея напряжения - выходом анализатора моентов регистрации сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор цифрового сигнала | 1984 |

|

SU1239881A1 |

| Устройство прерывистой радиосвязи | 1989 |

|

SU1748263A1 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1988 |

|

SU1555875A1 |

| Устройство фазирования регенераторов цифрового сигнала | 1978 |

|

SU786036A1 |

| Устройство для формирования последовательности импульсов | 1983 |

|

SU1157676A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1210225A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Цифровой преобразователь импульсного напряжения | 1989 |

|

SU1636783A1 |

| Анализатор интерферограмм | 1989 |

|

SU1660209A1 |

7i.ijU I

Авторы

Даты

1977-05-30—Публикация

1975-05-11—Подача