Изобретение относится к электротехнике связи и может быть использовано в системах передачи дискретной ин(ормации для регенерации цифрового сигнала.

Цель изобретения - повьппение точности регенерации.

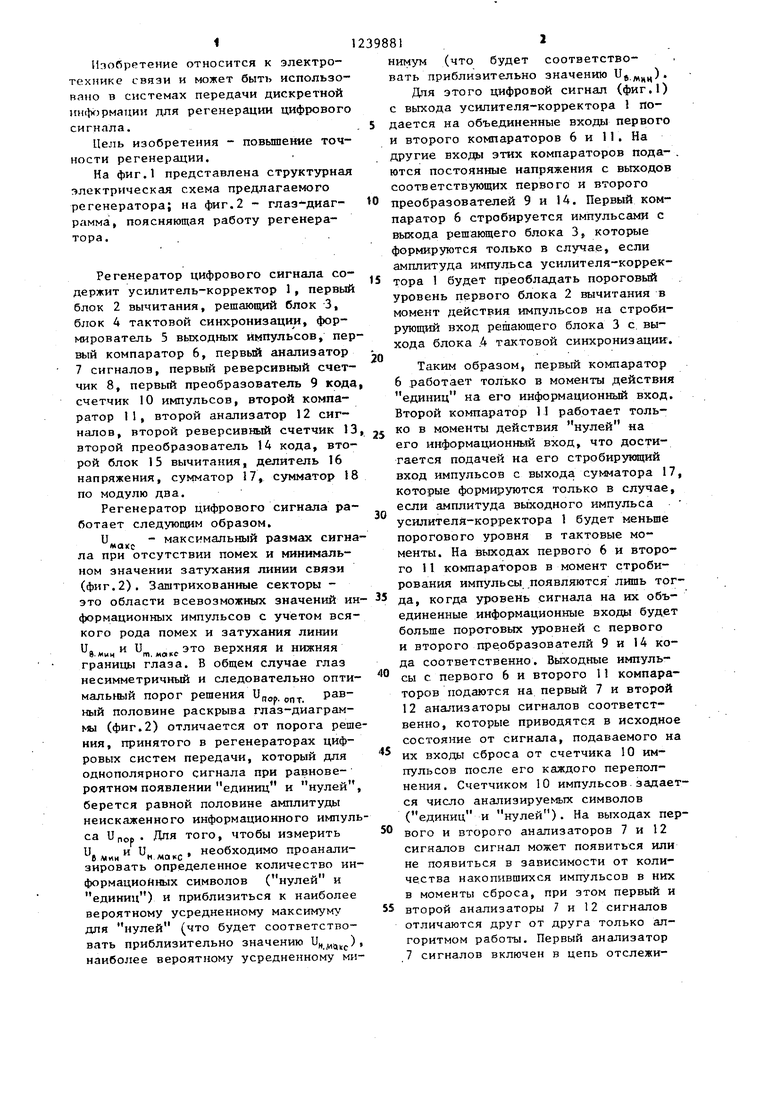

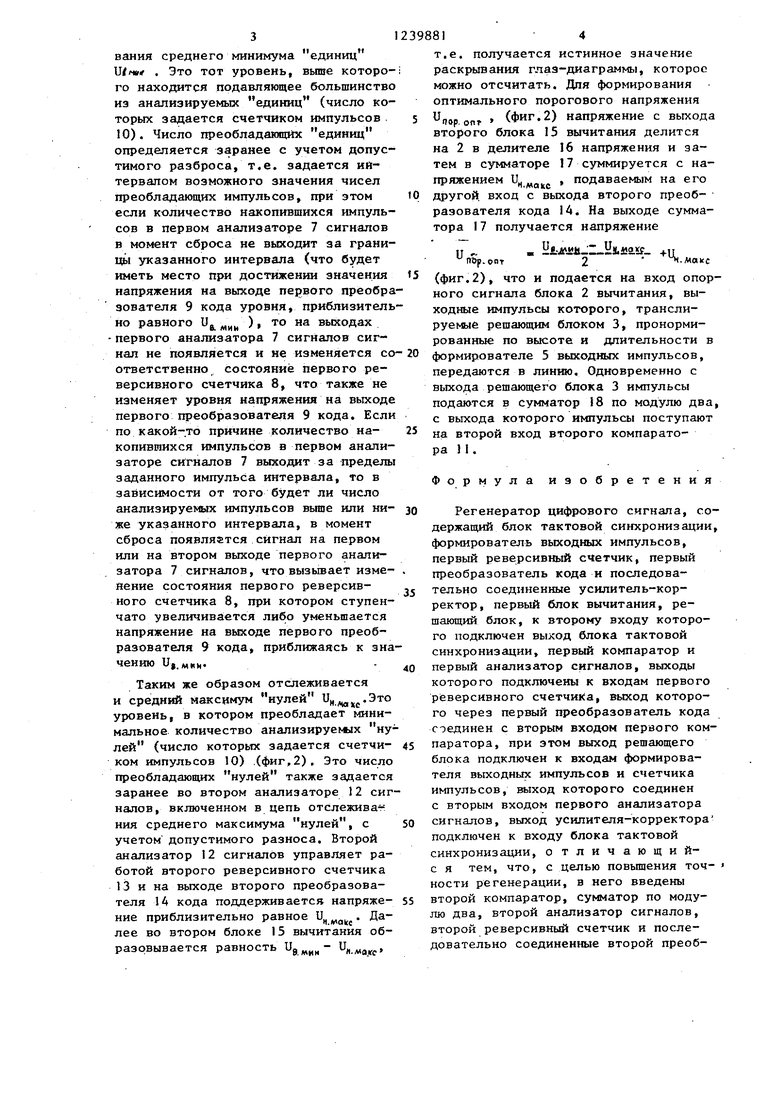

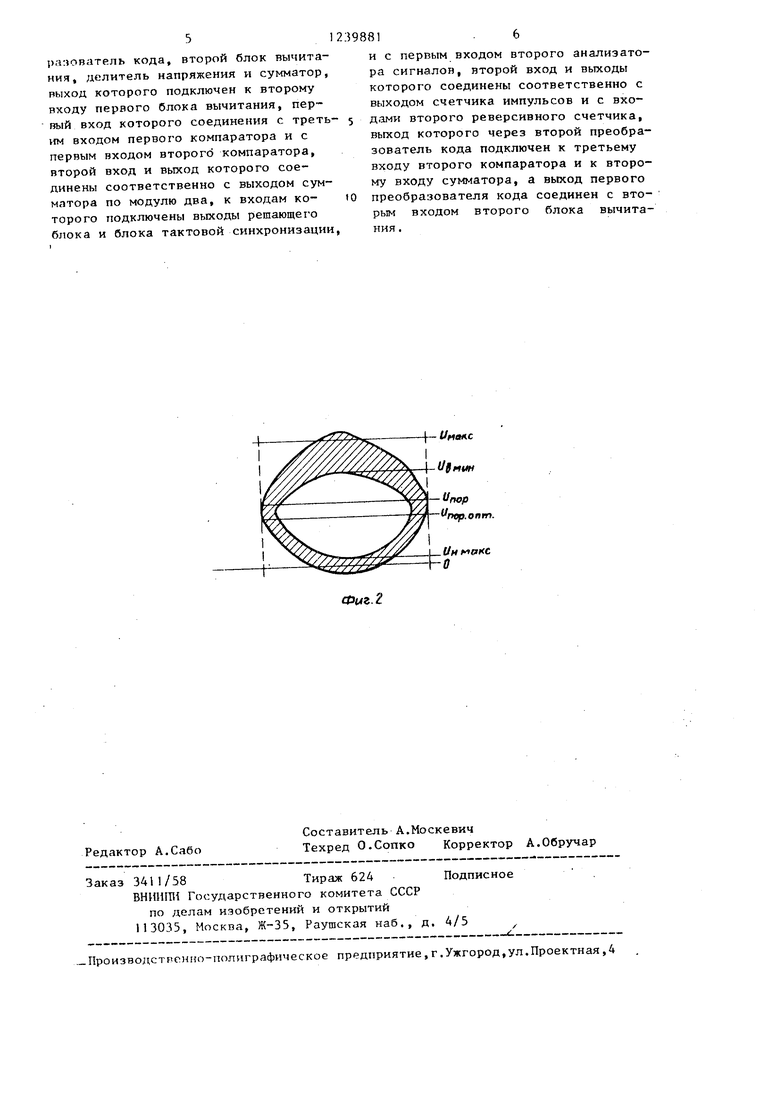

На фиг.1 представлена структурная электрическая схема предлагаемого регенератора; на фиг.2 - глаз диаг- рамма, поясняющая работу регенератора.

Регенератор цифрового сигнала содержит усилитель-корректор 1, первый блок 2 вычитания, решающий блок 3, блок 4 тактовой синхронизации, формирователь 5 выходных импульсов, первый компаратор 6, первый анализатор 7 сигналов, первый реверсивный счетчик 8, первый преобразователь 9 кода, счетчик 10 импульсов, второй компаратор 11 , второй анализатор 12 сигнимум (что будет соответствовать приблизительно значению Для этого цифровой сигнал (фиг с выхода усилителя-корректора п

5 дается на объе,диненные входы перв и второго компараторов 6 и 11. На другие входы этих компараторов по ются постоянные напряжения с выхо соответствующих первого и второго

О преобразователей 9 и 14. Первый к паратор 6 стробируется импульсами выхода решающего блока 3, которые формируются только в случае, если амплитуда импульса усилителя-корр

15 тора 1 будет гсреобладать пороговы уровень первого блока 2 вычитания момент действия импульсов на стро рующий вход решающего блока 3 с. в хода блока А тактовой синхронизац

Таким образом, первый компарат 6 работает только в моменты дейст единиц на его информационный вх Второй компаратор 11 работает тол

20

налов, второй реверсивный счетчик 13, 35 моменты действия нулей на

второй преобразователь 14 кода, второй блок 15 вычитания, делитель 16 напряжения, сумматор 17, сумматор 18 по модулю два.

Регенератор цифрового сигнала работает следующим образом.

максимальный размах сигнала при отсутствии помех и минимальном значении затухания линии связи (фиг.2). Заштрихованные секторы 30

его информационный вход, что дост гается подачей на его стробирующи вход импульсов с выхода сумматора которые форми уются только в случ если амплитуда выходного импульса усилителя-корректора I будет мень порогового уровня в тактовые моменты. На выходах первого 6 и вто го 11 компараторов в момент строб рования импульсы появляются лишь

это области всевозможных значений ин- 35 дд когда уровень сигнала на их объединенные информационные входы будет больше пороговых уровней с первого и второго преобразователи 9 и 14 кода соответственно. Выходные импуль сы с первого 6 и второго 11 компараторов подаются на первый 7 и второй 12 анализаторы сигналов соответственно, которые приводятся в исходное состояние от сигнала, подаваемого на

их входы сброса от счетчика 10 импульсов после его каждого переполнения . Счетчиком 10 импульсов.задается число анализируемых символов (единиц и нулей). На выходах пер вого и второго анализаторов 7 и 12 сигналов сигнал может появиться илн не появиться в зависимости от количества накопившихся импульсов в них в моменты сброса, при этом первый и

55 второй анализаторы 7 н 12 сигналов отличаются друг от друга только алгоритмом работы. Первый анализатор 7 сигналов включен в цепь отслежиформационных импульсов с учетом всякого рода помех и затзгхания линии

й.мии т. макс верХНЯЯ И НИЖНЯЯ

границы глаза. В общем случае глаз несимметричный и следовательно оптимальный порог решения и„„ равный половине раскрыва глаз-диаграммы (фиг.2) отличается от порога решения, принятого в регенераторах цифровых систем передачи, который для однополярного сигнала при равнове- роятном появленни единиц и нулей, берется равной половине амплитуды неискаженного информационного импульса и пор . Дпя того, чтобы измерить

вм«и нма.с- необходимо проанализировать определенное количество информационных символов (нулей и единиц) и приблизиться к наиболее вероятному усредненному максимуму для нулей (что будет соответствовать приблизительно значению UKJUU C наиболее вероятному усредненному минимум (что будет соответствовать приблизительно значению ), Для этого цифровой сигнал (фиг,1) с выхода усилителя-корректора подается на объе,диненные входы первого и второго компараторов 6 и 11. На другие входы этих компараторов пода- . ются постоянные напряжения с выходов соответствующих первого и второго

преобразователей 9 и 14. Первый компаратор 6 стробируется импульсами с выхода решающего блока 3, которые формируются только в случае, если амплитуда импульса усилителя-корректора 1 будет гсреобладать пороговый уровень первого блока 2 вычитания в момент действия импульсов на строби- рующий вход решающего блока 3 с. выхода блока А тактовой синхронизации.

Таким образом, первый компаратор 6 работает только в моменты действия единиц на его информационный вход. Второй компаратор 11 работает толь-

моменты действия нулей на

его информационный вход, что достигается подачей на его стробирующий вход импульсов с выхода сумматора 17, которые форми уются только в случае, если амплитуда выходного импульса усилителя-корректора I будет меньше порогового уровня в тактовые моменты. На выходах первого 6 и второго 11 компараторов в момент строби- рования импульсы появляются лишь тогвания среднего минимума единиц UtMuif , Это ТОТ уровень, выше которого находится подавляющее большинство из анализируемых единиц (число которых задается счетчиком импульсов , 10). Число преобладающих единиц определяется заранее с учетом допустимого разброса, т.е. задается интервалом возможного значения чисел преобладающих импульсов, при этом если количество накопившихся импульсов в первом анализаторе 7 сигналов в момент сброса не выходит за грани- Щ.1 указанного интервала (что будет иметь место при достижении значения напряжения на выходе первого преобразователя 9 кода уровня, приблизительно равного Uj ), то на выходах первого анализатора 7 сигналов сигнал не появляется и не изменяется со ответственно состояние первого реверсивного счетчика 8, что также не изменяет уровня напряжения на выходе первого преобразователя 9 кода. Если по какой-то причине количество на- копившихся импульсов в первом анализаторе сигналов 7 выходит за пределы заданного импульса интервала, то в зависимости от того будет ли число aнaлизиpye aлx импульсов выше или ни- же указанного интервала, в момент сброса ПОЯВЛЯЕТСЯ сигнал на первом или на втором выходе первого анализатора 7 сигналов, что вызывает изме- йение состояния первого реверсивного счетчика 8, при котором ступенчато увеличива ется либо уменьшается напряжение на выходе первого преобразователя 9 кода, приближаясь к значению и,. „ИИ.

Таким же образом отслеживается и средний максимум нулей и.Это уровеиь, в котором преобладает минимальное количество aнaлизиpye ыx нулей (число которых задается счетчи- ком импульсов 10) .(фиг,2). Это число преобладающих нулей также задается заранее во втором анализаторе 12 сигналов, включенном в цепь отслеживат-: НИЛ среднего максимума нулей, с учетом допустимого разноса. Второй анализатор 12 сигналов управляет работой второго реверсивного счетчика 13 и на выходе второго преобразователя 14 кода ггоддерживаетсн напряже- ние приблизительно равное U , Далее во втором блоке 15 вычитания образовывается равность Ug U.Maifc

s tp 15 20 25 зо

5 0 5

5

0

Т.е. получается истинное значение раскрывания глаз-диаграммы, которое можно отсчитать. Для формирования оптимального порогового напряжения . опт (фиг. 2) напряжение с выхода второго блока 15 вычитания делится на 2 в делителе 16 напряжения и затем в сумматоре 17 суммируется с напряжением U... , подаваемым на его другой, вход с выхода второго преобразователя кода 14. На выходе сумматора I7 получается напряжение

и « yi- ytfa-r-ybfioiff- +и

Пир.опт 2 .макс (фиг.2), что и подается на вход опорного сигнала блока 2 вычитания, выходные импульсы которого, транслируемые решающим блоком 3, пронормированные по вьюоте и длительности в формирователе 5 выходных импульсов, передаются в линшо. Одновременно с выхода решающего блока 3 импульсы подаются в сумматор 18 по модулю два, с выхода которого импульсы поступают на второй вход второго компаратора п.

Формула изобретения

Регенератор цифрового сигнала, содержащий блок тактовой синхронизации, формирователь выходных импульсов, первый реверсив№1й счетчик, первый преобразователь кода н последовательно соединенные усилитель-корректор, первый блок вычитания, решающий блок, к второму входу которого подключен выход блока тактовой синхронизации, первый компаратор и первый анализатор сигналов, выходы которого подключены к входам первого реверсивного счетчиКа, выход которого через первый преобразователь кода соединен с вторым входом первого компаратора, при этом выход решающего блока подключен к входам формирователя выходных импульсов и счетчика импульсов, выход которого соединен с вторым входом первого анализатора сигналов, выход усилителя-корректора подключен к входу блока тактовой синхронизации, о тличающий- с я тем, что, с целью повышения точ- ности регенерации, в него введены второй компаратор, сумматор по модулю два, второй анализатор сигналов, второй реверсивный счетчик и последовательно соединенные второй преоб5

ра: ователь кода, второй блок вычитания, делитель напряжения и сумматор, выход которого подключен к второму входу первого блока вычитания, первый вход которого соединения с третьим входом первого компаратора и с первым входом второго компаратора, второй вход и выход которого соединены соответственно с выходом сумматора по модулю два, к входам которого подключены выходы решающего блока и блока тактовой синхронизации.

881. 6

и с первым входом второго анализатора сигналов, второй вход и выходы которого соединены соответственно с выходом счетчика импульсов и с вхо- дами второго реверсивного счетчика, вьпсод которого через второй преобразователь кода подключен к третьему входу второго компаратора и к второму входу сумматора, а выход первого преобразователя кода соединен с вторым входом второго блока вычитания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Цифровая система управления | 1984 |

|

SU1234811A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1540003A2 |

| Преобразователь перемещения в код | 1983 |

|

SU1111189A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| РЕЛЕ НАПРАВЛЕНИЯ МОЩНОСТИ | 2002 |

|

RU2208231C1 |

Изобретение относится к электротехнике связи. Повьппается точность регенерации. Устр-во содержит 1-й блок вычитания (БВ), решающий блок 3, блок тактовой синхронизации 4, формирователь дыходных импульсов 5, 1-й анализатор сигналов (АС) 7, 1-й реверсивный счетчик (PC) 8, 1-й преобразователь кода 9, счетчик импульсов 10. Цель достигается введением следующих блоков: 2-го компаратора II, сумматора по модулю два 18, 2-го АС 12, 2-го PC 13, 2-го преобразователя кода 14, 2-го блока вычитания 15, делителя напряжения 16, сумматора 17. 2 ил. (Л

.

UH макс О

Редактор А.Сабо

Составитель А.Москевич

Техред О.Сопко Корректор А.Обручар

Заказ 3411/58Тираж 624 Подписное .

ВНИИ11Н Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

- -- - - - - ------ -. .--Ж. .-.«,«,.

.-Производстрснио-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

Ф1АЪ.2

| Регенератор цифрового сигнала | 1980 |

|

SU919138A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-06-23—Публикация

1984-03-21—Подача