(54) -УСТРОЙСТВО ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Расширитель импульсов | 1977 |

|

SU687575A1 |

| Формирователь импульсов наносекундной длительности | 1978 |

|

SU705659A1 |

| Преобразователь переменного напряжения в постоянное | 1987 |

|

SU1422331A1 |

| КОММУТАЦИОННОЕ УСТРОЙСТВО | 1997 |

|

RU2175166C2 |

| Формирователь импульсов | 1974 |

|

SU566330A1 |

| Генератор импульсов | 1981 |

|

SU1018195A1 |

| Управляемый преобразователь импульсов | 1981 |

|

SU1023644A1 |

| Устройство с временной автоматической регулировкой усиления | 1989 |

|

SU1778908A1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

| Устройство формирования импульсных последовательностей | 1973 |

|

SU507917A1 |

1

Изобретение относится к электронной технике, подобные устройства применяютс в схемах автоматики и телемеханики, в частности в схемах управления считкой, где в качестве исполнительного механиэма служит однооборотная электромагнитная муфта. Изобретение может быть использовано в электронной, радиотехнической и других отраслях.

Известен формирователь импульсов,

содержащий управляющий и накопительный каск,ады, между которыми включены два последовательно соединенных транзистора разных типов проводимости. Дозирующий конденсатор накопительного каскада подключей к точке соединения коллекторов транзисторов. База одного из транзисторов подключена к нагрузке управляющего каскада непосредственно, а база другого через последовательно и встречно соединенные диоды, точка соединения которых через резистор подключена к шине питани

Однако такое устройство не позволяет получить импульс выходного напряжения большей длительности и мощности..

Известна схема временной задержки на элементах ЭТ-В02, содержащая зарядный конденсатор и формиргукхций каскад, в которой длительность выходного импульса задержанного на время действия входного :сигнала определяется практически зарядным конденсатором и сопротивлением 2 |.

Однако заряд этого конденсатора зависит от уровня входного сигнала, длительность выходного импульса также зависит от уровня входного сигнала. Кроме того, невозможно получить ИМПУЛЬС выходного напряжения большей длительности и мощности.

Цель изобретения - формирование выходного импульса, длительность которого не зависит от уровня входного сигнала.

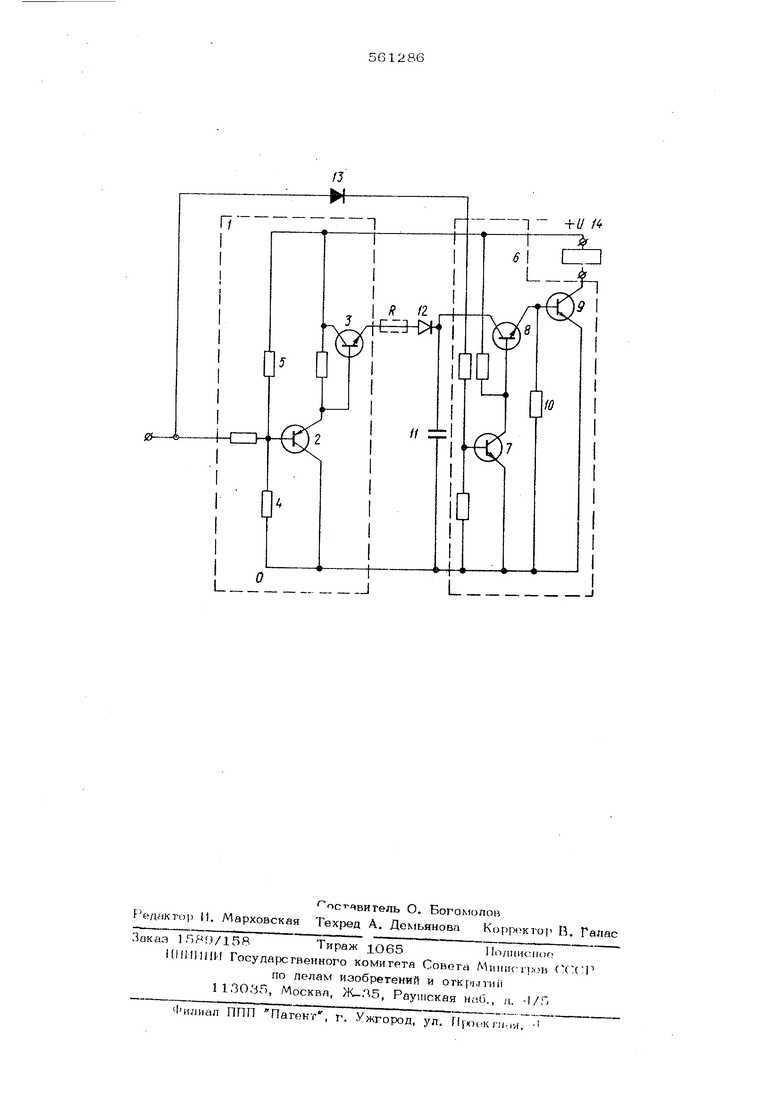

Для этого в устройство задержки, содержащее конденсатор, формирующий каскад выходной каскад с исполнительным реле в качестве нагрузки, введен ключевой каскад на транзисторах разного пшя проводимости, при этом вход одного из них соедийен со входом устройства и чррез диод в Прямом Пр1)1и)) I;; С оХОДЭМ фГ) ) Ij iOHf;r;j каскада, )iii io:iiiein oro ;.;, Ari. . гранoucrojiax, KOJ JieKT0(4K -3viurropvib fi пеГ1еход нгорсло г 1 1НзисгорГ1 ключевого кас;када включен последовательно с коиденсаго.ог-.: между lllинa fи источника пигания, при этом коллекгорно-эмиггериый переход вгооого гранзистора формирующего каскад включен vieKfly кснденсагорок; и входом вьгходного каскада, соединешшм через резистор с общей шиной источника гпгганкя. На чертеже представлена приша-птнальна электрическая схема устройства, Устройство содержит ключево - каскад 1 состоящий из двух транзисторов 2, 3 размой проводимости,резисторов 4, 5, формирующего каскада 6, состоящего из траизисторов 7, S; 9., резистора 10, зарядно-го конденсатора 11, диодов 12, 13 испол нигелыюго механизма 14. В исходном состоянии в ключевом каскаде 1 транзистор 2 открыт смещением, создаваемь М резисторами 4, 5, транзисто 3 закрь Т, так как его база через открьзты переход транзистора 2 соединена с нулево шиной. В фхэрмирующем каскаде 6 транзистор 7 закрь г. транзистор 8 находится в открытом состоянии, но к его выводам коллектир-эмиттер не приложено напря--.. жение, гракзисгор 9 закрыт., При поступлении входного сихиале. на каскад 1 транзистор 2 закрывается, при этом открывается транзистор 3 и происходит заряд комденсатсра 11. Время заряда обусловлено емкостью конденсатора 11, сопротивлением коллектор-эмкттер откры того транзистора 3 и переходом диода 12 включенного в прямом направлении. необходимо отграничить скорость заряда конденсатора 11 вводится дополнительно сопротивление R . Одновременно входной си1нал через диод 13 подается на каскад 6, открывает транзистор 7, транзистор 8 при этом закр вается, транзистор,9 остается в исходном состоянии, состояние транзисторов 7, 8, 9 сохраняется на время действия входного сигнала. После снятия входного сигнала тран. зистор 7 закрывается и открывается транзистор 8, Начинается разряд конденсатора 11 через открытый транзистор 8 и резистор 10 потенциал появляющийся на розисторе 1О открывает транзистор Я. Длительность и моипюсть гп.тзльса, по1),ляюш(-:-гося на ба:ч. Г 1анзистора :) О11р«:-д1. ляогся неличной емкости кокдекса гора 11 и величиной резистора 10 и iie,- cicibHCHr ,-)Г уровня входного сигнала. В сяучае, если . вход подается HecKOJEbко сигналов разной длительности (через схему ИЛМ), выходной им гульс находится после снятия всех входящих сигналов, т. е. будет задержан на время действия наиболее продолжительного входного сигнала. Мслол:ьЗование в предложенной схеме задержки ключевого каскада позволяет по.пучить -; 1ходной импульс, параГЛетрь; ко- горого яе зависят от уровня входного ск нала, дггнтельиость им1г/льса может быть получена от нескольких кя-пгросекунд до де с я гк о в с еку щ, Кроме того, в предложенной схеме задержки выходной импульс уси.гшваетсй транзистором 9 фop;vlиpJl-oш.eгo каскада, вследствие чего не требуе-гск дополнительк:;-;/ формнрзтощих и ycHJiHTe.nbiibix устройств при работе с исполнителькммй меха..иаые лФорм у л а и 3 о б р Устройство задеузжк. содержащее коя-денсатор, форг,:нг)ующнй Хпскад, вьхойно;каскад с испоаиг г яыйЬ: -. jajLe Е качвс- а нагрузки, о т л h ч а .; л е е с я тем, что, с целью форл ирлзанни зтлхояного имггГЪса, дпительность которого ле завискг о-УрОВНЯ входного Ctiy HiMri,;:С -Г. ЙС 1 :iвведен ключевой каскад «s грйкз сгора;: разного типа проводимости, при этом вход одного из них соедикэк со входом устрой, стза и через диод в пркмой проводимости со входом формирующего каскада, выполненного на авук транзисторйх, коллекгорно-эмиттерный переход второго транзисго ра ключевого каскада включен последовательно с конденсатором между шинами источника питания, при этом коллекторно-. -эмиттершлй переход второго транзистора формирующего каскада включен между кон. денсатором и входом выходного каскадар соединенным через резистор с общей и.1иной источника питания. Источники информации, принятые во внк мание при экспертизе; 1.Авторское свидетельство №35 Н 03 К,0б.01.71. 2.ЕгГдипая полупроводниЕхОр,--.;х и упкциогьгиплых эломоьтоо (Э1У )М.Л, Эггергия, 1 Г)ПП,

Авторы

Даты

1977-06-05—Публикация

1975-12-24—Подача