54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ НАНОСЕКУНДНОЙ ДЛИТЕЛЬНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1974 |

|

SU566330A1 |

| Формирователь импульсов наносекундной регулируемой длительности | 1985 |

|

SU1336213A1 |

| Формирователь импульсов | 1977 |

|

SU692071A2 |

| Способ быстрого включения силового транзистора с изолированным затвором и устройства с его использованием | 2018 |

|

RU2713559C2 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВБИБЛ;10.: КЛ | 1972 |

|

SU350140A1 |

| Формирователь импульсов | 1980 |

|

SU921065A1 |

| ФОРМИРОВАТЕЛЬ СУБНАНОСЕКУНДНЫХ ИМПУЛЬСОВ | 2024 |

|

RU2822823C1 |

| ТРАНЗИСТОРНЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU346786A1 |

| ФОРМИРОВАТЕЛЬ ТОКА ВЫБОРКИ | 1973 |

|

SU377869A1 |

| Формирователь высоковольтных прямоугольных импульсов | 1978 |

|

SU771863A1 |

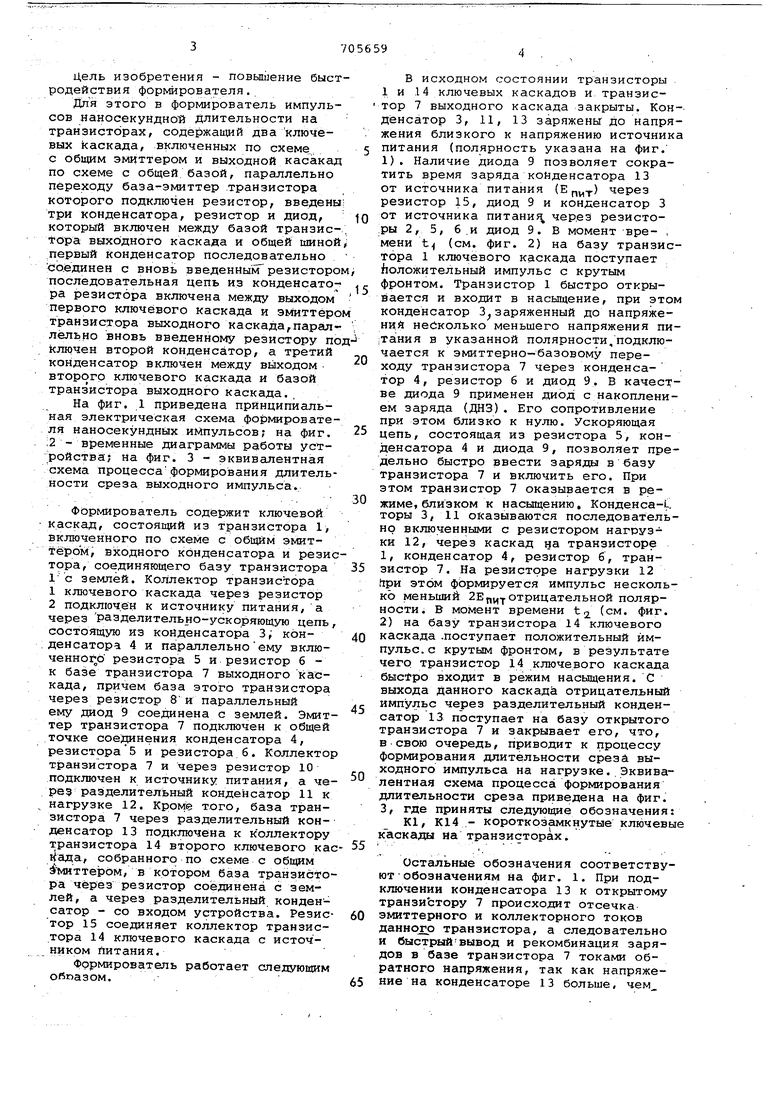

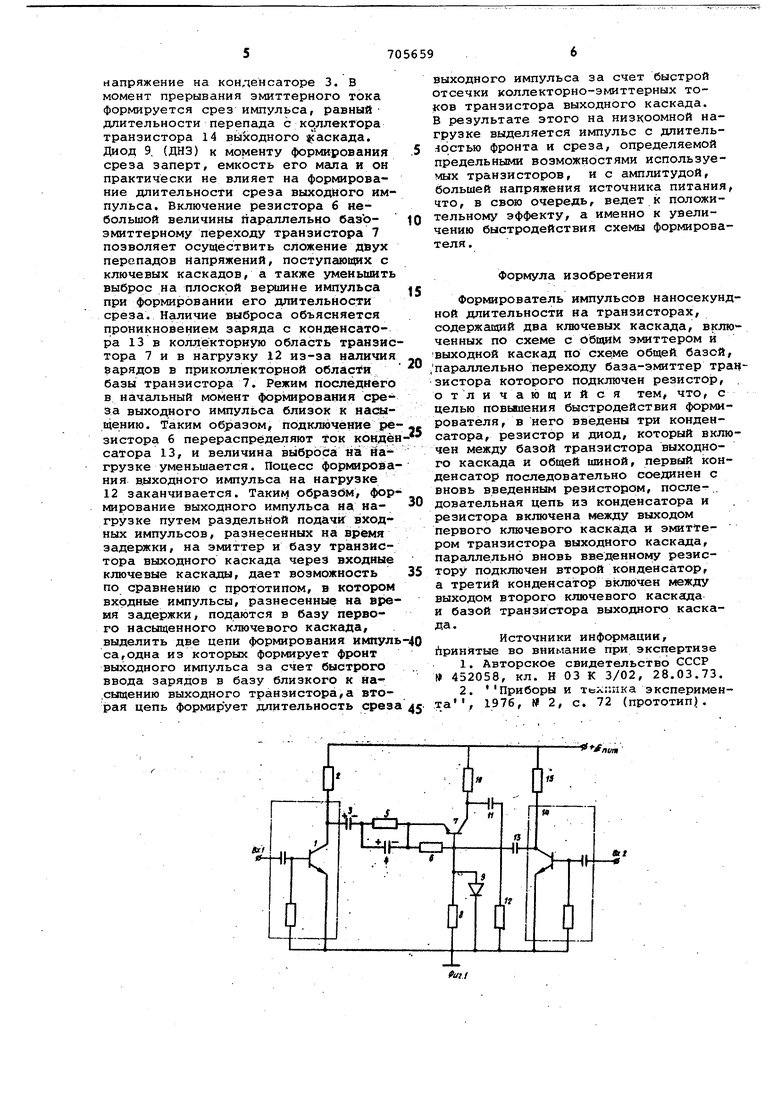

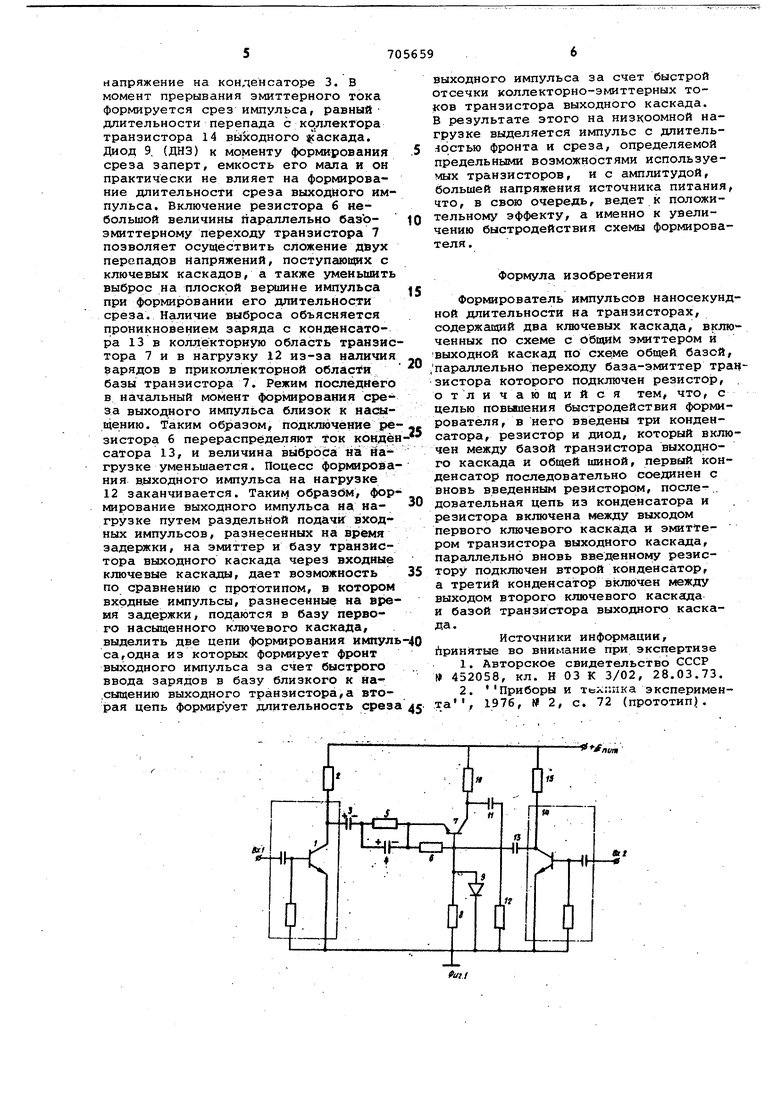

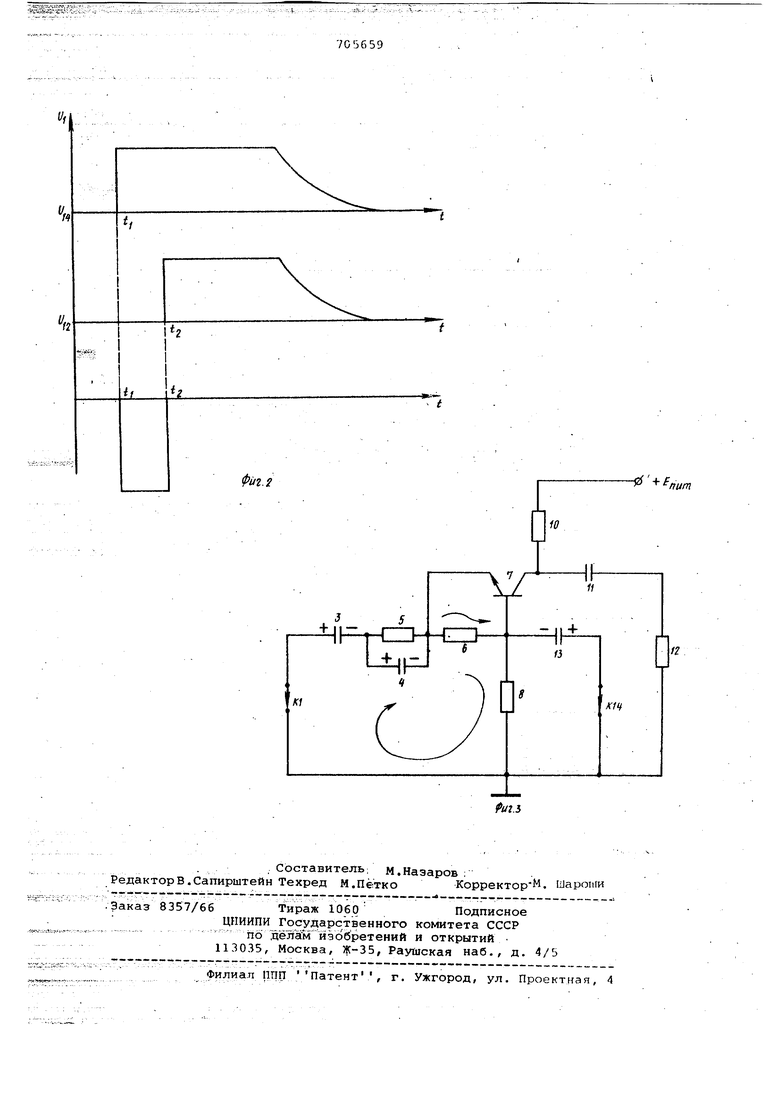

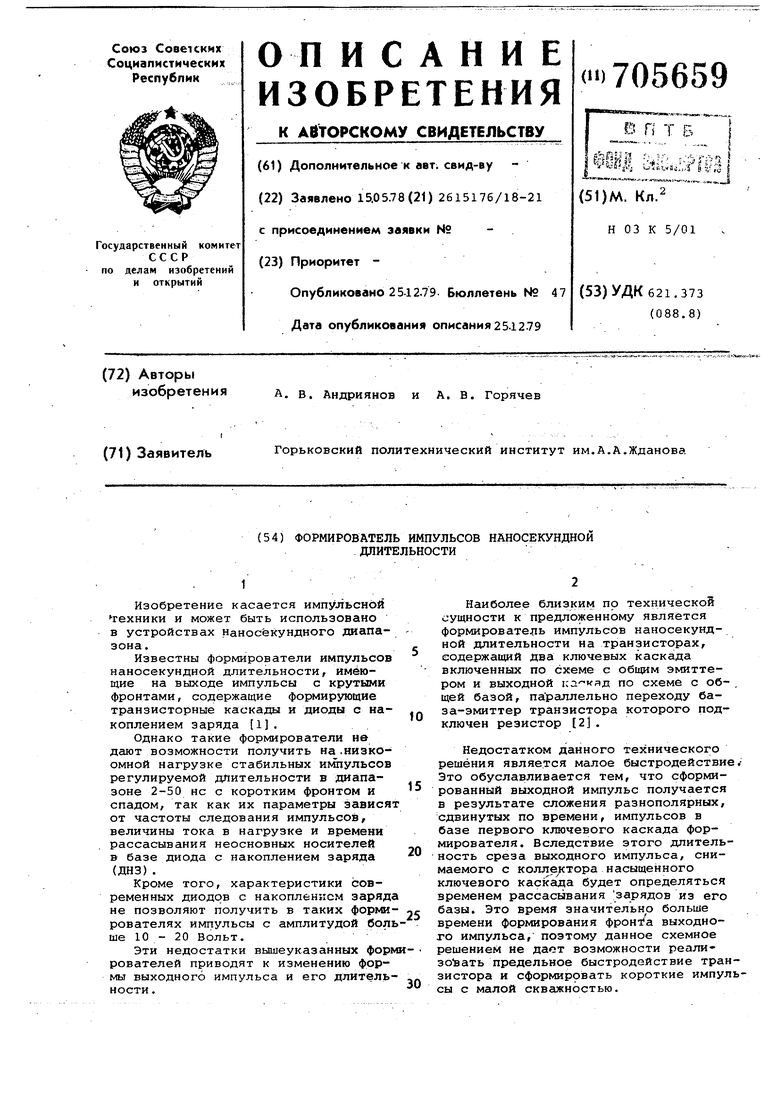

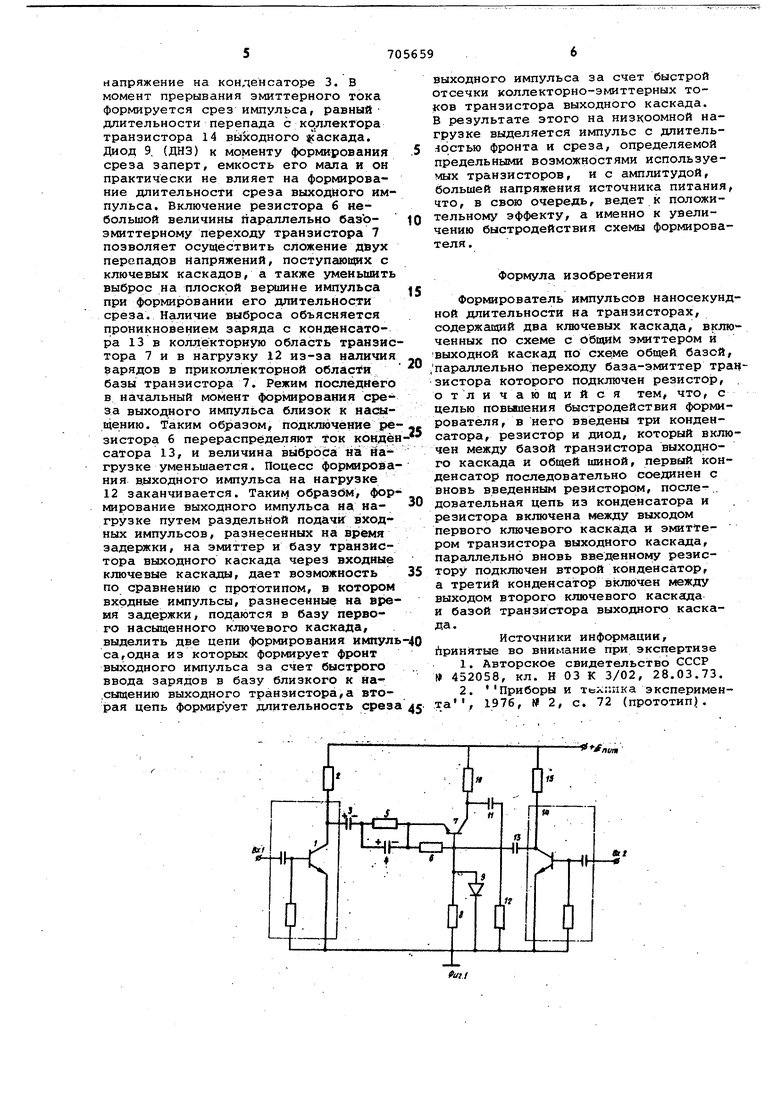

Изобретение касается импульсной техники и может быть использовано в устройствах наносёкундного диапазона . Известны формирователи импульсов наносекундной длительности, Имеющие на выходе импульсы с крутыми фронтами, содержащие формирующие транзисторные каскады и диоды с накоплением заряда 1. Однако такие формирователи не дают возможности получить на .низкоомной нагрузке стабильных иШ1ульсов регулируемой длительности в диапазоне 2-50 НС с коротким фронтом и спадом, так как их параметры завися от частоты следования импульсов, величины тока в нагрузке и времени рассасывания неосновных носителей в базе диода с накоплением заряда (ДНЗ) . Кроме того, характеристики современных диодов с накоплением заряд не позволяют получить в таких форми рователях импульсы с амплитудой бол ше 10 - 20 Вольт. Эти недостатки вышеуказанных фор рователей приводят к изменению формы выходного импульса и его длитель ности . Наиболее близким по технической сущности к предложенному является формирователь импульсов наносекундной длительности на транзисторах, содержащий два ключевых каскада включенных по схеме с общим эмиттером и выходной по схеме с об- . щей базой, параллельно переходу база-эмиттер транзистора которого подключен резистор 2. Недостатком данного технического решения является малое быстродействие , Это обуславливается тем, что сформированный выходной импульс получается в результате сложения разнополярных, сдвинутых по времени, импульсов в базе первого ключевого каскада формирователя. Вследствие этого .цлительность среза выходного импульса, снимаемого с коллектора насыщенного ключевого каскада будет определяться временем рассасывания зарядов из его базы. Это время значительно больше времени формирования фронта выходного импульса, поэтому данное схемное решением не даст возможности реализовать предельное быстродействие транзистора и сформировать короткие импульсы с малой скважностью. цель изобретения - повышение быст родействия формирователя,. Для этого в формирователь импульсов наносекунднотй длительности на транзисторах, содержащий два ключевых каскада, включенных по схеме с общим эмиттером и выходной касакад по схеме с общей базой, параллельно переходу база-эмиттер транзистора которого подключен резистор, введены три конденсатора, резистор и диод, который включен между базой транзистора выходного каскада и общей шиной первый конденсатор последовательно соединен с вновь введенным резисторо последовательная цепь из конденсатора резистора включена между выходом первого ключевого каскада и эмиттер транзистора выходного каскада,парал лёльно вновь введенному резистору по Ключей второй конденсатор, а третий конденсатор включен между выходомвторсэгр ключевого каскада и базой транзистора выходного каскада. На фиг. 1 приведена принципиальная электрическая схема формировате ля наносекундных импульсов; на фиг. :2 - временные диаграммы работы устройства; на фиг. 3 - эквивалентная схема процессаформирования длитель ности среза выходного импульса. . ; , . ; Формирователь содержит ключевой каскад, состоящий из транзистора 1, включенного по схеме с общим эмиттером, входного конденсатора и рези тора, соединяющего базу транзистора 1 с землей. Коллектор транзистора 1ключевого каскада через резистор 2подключен к источнику питания, а через разделительно-ускоряющую цепь состоящую из конденсатора 3; кон: денсатора 4 и параллельноему включенного резистора 5 и резистор 6 к базе транзистора 7 выходного каскада, причем база этого транзистора через резистор 8 и параллельный ему диод 9 соединена с землей. Эмит тер транзистора 7 подключен к общей точке соединения конденсатора 4, резистора 5 и резистора б. Коллекто транзистора 7 и через резистор 10 подключен к источнику питания, а че ре разделительный конденсатор 11 к нагрузке 12. Кроме того, база транзистора 7 через разделительный конденсатор 13 подключена к коллектору транзистора 14 второго ключевого ка , собранного по схеме с общим миттерйм, в котором база транзисто ра через резистор соединена с землей, а через разделительный конденсатор - со входом устройства. Резис тор 15 соединяет коллектор транзистора 14 ключевого каскада с источником Питания. Формирователь работает следующим оВпазом. В исходном состоянии транзисторы 1 и .14 ключевых каскадов и транзистор 7 выходного каскада закрыты. Кон-дёнсатор 3, 11, 13 заряжены до напряжения близкого к напряжению источника питания (полярность указана на фиг. 1). Наличие диода 9 позволяет сократить время заряда конденсатора 13 от источника питания () через резистор 15, диод 9 и конденсатор 3 от источника питаниу чер.еэ резистоы 2,5, 6.и диод 9. В момент вре- , мени t (см. фиг. 2) на базу транзистора 1 ключевого каскада поступает положительный импульс с крутым фронтом. Транзистор 1 быстро открывается и входит в насыщение, при этом конденсатор 3, заряженный до напряжения несколько меньшего напряжения пи:Та1Ния в указанной полярности, подключается к эмиттерно-базовому переходу транзистора 7 через конденсатор 4, резистор 6 и диод 9. В качестве диода 9 применен диод с накоплением заряда (ДНЗ). Его сопротивление при этом близко к нулю. Ускоряющая цепь, состоящая из резистора 5, конденсатора 4 и диода 9, позволяет предельно быстро ввести заряды в базу транзистора 7 и включить его. При этом транзистор 7 оказывается в режиме, близком к насыщению, Конденса-L. торы 3, 11 оказываются последовательно включенными с резистором нагрузки 12, через каскад на транзисторе 1, конденсатор 4, резистор 6, транзистор 7. На резисторе нагрузки 12 йри этом фЬрмируется импульс несколько меньший 2Е пит отрицательной полярности. В момент времени t (см. фиг. 2) на базу транзистора 14 ключевого каскада .поступает положительный импульс, с крутым фронтом, в результате чего транзистор 14 ключевого каскада быстро входит в режим насыщения. С выхода данного каскада отрицательный импульс через разделительный конденсатор 13 поступает на базу открытого транзистора 7 и закрывает его, что, в - свою очередь, приводит к процессу формирования длительности среза выходного импульса на нагрузке..Эквивалентная схема процесса формирования длительности среза приведена на фиг. 3, где приняты следующие обозначения: К1, К14 .- короткозамкнутые ключевые к аскады иа транзисторах. Остальные обозначения соответствуют обозначениям на фиг. 1. При подключении конденсатора 13 к открытому транзистору 7 происходит отсечка эмиттврного и коллекторного токов дaннoJчэ транзистора, а следовательно и быстрый вывод и рекомбинация зарядов в базе транзистора 7 токами обратного напряжения, так как напряжение на конденсаторе 13 больше, чем. напряжение на конденсаторе 3. В момент прерывания эмиттерного тока формируется срез импульса, равный длительности перепада с ксзллектора транзистора 14 выходного аскада. Диод 9. (ДНЗ) к моменту формирования среза заперт, емкость его мала и он практически не влияет на формирование длительности среза вьлходного импульса. Включение резистора б небольшой величины параллельно базоэмиттерному переходу транзистора 7 позволяет осуществить сложение д&ух перепадов напряжений, поступающих с ключевых каскадов, а также уменьшить выброс на плоской вершине импульса при формировании его длительности среза. Наличие выброса объясняется проникновением заряда с конденсатора 13 в коллекторную область транзис тора 7 и в нагрузку 12 из-за наличия варядов в приколлекторной области базы транзистора 7. Режим последнего в начальный момент формирования среза выходного импульса близок к насыщению. Таким образом, подключение ре зистора 6 перераспределяют Ток конде сатора 13, и величина вь брЬсв; на йагрузке уменьшается. Поцесс формирова ния выходного импульса на нагрузке 12 заканчивается. Таким образбм, фор мирование выходного импульса на нагрузке путем раздельной подачи: входных импульсов, разнесенных на время задержки, на эмиттер и базу транзистора выходного каскада через входные ключевые каскады, дает возможность по сравнению с прототипом, в котором входные импульсы, разнесенные на вре ия задержки, подаются в базу первого насыщенного ключевого каскада, выделить две цепи формирования импул са,одна из которых формирует фронт выходного импульса за счет быстрого ввода зарядов в базу близкого к на.сыщению выходного транзистора,а вторая цепь формирует длительность срез

л выходного импульса за счет быстрой отсечки коллекторно-эмиттерных токов транзистора выходного каскада. В результате этого на низкоомной нагрузке выделяется импульс с длительностью фронта и среза, определяемой предельными возможностями используемых транзисторов, и с амплитудой, большей напряжения источника питания, что, в свою очередь, ведет к положительному эффекту, а именно к увеличению быстродействия схемы формирователя . Формула изобретения Формирователь импульсов наносекундной длительности на транзисторах, содержащий два ключевых каскаада, включенных по схеме с общим эмиттером и ВЫХОДНОЙ каскад по схеме общей базой, парсшлельно переходу база-эмиттер трачзистора которого подключен резистор, отличающийся тем, что, с целью повышения быстродействия формирователя, в него введены три конденсатора, резистор и диод, который включен между базой транзистора выходного каскада и общей шиной, первый конденсатор последовательно соединен с вновь введенным резистором, после-,, довательная цепь из конденсатора и резистора включена между выходом первого ключевого каскада и эмитТером транзистора выходного каскада, параллельно вновь введенному резистору подключен второй конденсатор, а третий конденсатор вволочен между выходом второго ключевого каскада и базой транзистора выходного каскада. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 452058, кл. Н 03 К 3/02, 28.03.73. 2.Приборы и TteXiniKa эксперимен1976, № 2, с. 72 (прототипJ.

ч.

2

hLk.

Авторы

Даты

1979-12-25—Публикация

1978-05-15—Подача