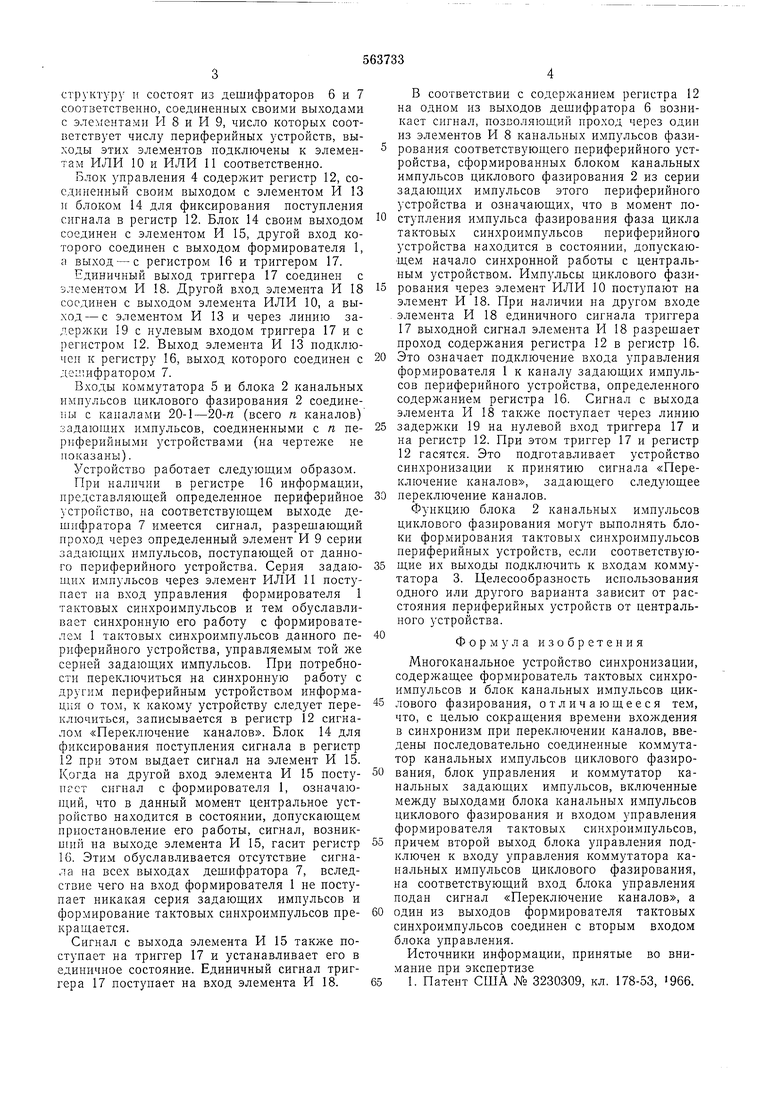

структуру и состоят из дешифраторов 6 и 7 соответственно, соединенных своими выходами с элементами PI 8 и И 9, число которых соответствует числу периферийных устройств, выходы этих элементов подключены к элементам ИЛИ 10 п ИЛИ 11 соответственно. Блок управления 4 содержит регистр 12, соединенный своим выходом с элементом И 13 и блоком 14 для фиксирования поступления сигнала в регистр 12. Блок 14 своим выходом соединен с элементом И 15, другой вход которого соединен с выходом формирователя 1, а выход - с регистром 16 и триггером 17. Единичный выход триггера 17 соединен с элементом И 18. Другой вход элемента И 18 соединен с выходом элемента ИЛИ 10, а выход- с элементом И 13 и через линию задержки 19 с нулевым входом триггера 17 и с регистром 12. Выход элемента И 13 подключен к регистру 16, выход которого соединен с депшфратором 7. Входы коммутатора 5 и блока 2 канальных импульсов циклового фазирования 2 соединены с каналами 20-1-20-п (всего п каналов) задающих имнульсов, соединенными с п нериферийными устройствами (на чертеже не показаны). Устройство работает следуюш.им образом. При наличии в регистре 16 информации, представляющей определенное периферийное устройство, на соответствующем выходе дешифратора 7 имеется сигнал, разрешающий проход через определенный элемент И 9 серии задающих импульсов, поступающей от данного периферийного устройства. Серия задаюuj,HX импульсов через элемент ИЛИ И поступает на вход управления формирователя 1 тактовых синхроимпульсов и тем обуславливает синхронную его работу с формирователем 1 тактовых сипхроимпульсов данного периферийного устройства, управляемым той же серией задающих импульсов. При потребности переключиться на синхронную работу с другим периферийным устройством информация о том, к какому устройству следует переключиться, записывается в регистр 12 сигналом «Переключение каналов. Блок 14 для фиксирования поступления сигнала в регистр 12 при этом выдает сигнал на элемент И 15. Когда на другой вход элемента И 15 поступест сигнал с формирователя 1, означающий, что в данный момент центральное устройство находится в состоянии, допускающем приостановление его работы, сигнал, возникший на выходе элемента И 15, гасит регистр 16. Этим обуславливается отсутствие сигнала на всех выходах дещифратора 7, вследствие чего на вход формирователя 1 не поступает никакая серия задающих импульсов и формирование тактовых синхроимпульсов прекращается. Сигнал с выхода элемента И 15 также поступает на триггер 17 и устанавливает его в единичное состояние. Единичный сигнал триггера 17 поступает на вход элемента И 18. В соответствии с содержанием регистра 12 на одном из выходов дещифратора 6 возникает сигнал, позволяющий проход через один из элементов И 8 канальных импульсов фазирования соответствующего периферийного устройства, сформированных блоком канальных импульсов циклового фазирования 2 из серии задающих импульсов этого периферийного устройства и означающих, что в момент поступления импульса фазирования фаза цикла тактовых синхроимпульсов периферийного устройства находится в состоянии, допускающем начало синхронной работы с центральным устройством. Импульсы циклового фазирования через элемент ИЛИ 10 поступают па элемент И 18. При наличии на другом входе элемента И 18 единичного сигнала триггера 17 выходной сигнал элемента П 18 разрешает проход содержания регистра 12 в регистр 16. Это означает подключение входа управления формирователя 1 к каналу задающих импульсов периферийного устройства, определенного содержапнем регистра 16. Сигнал с выхода элемента И 18 также поступает через линию задержки 19 на нулевой вход триггера 17 и на регистр 12. При этом триггер 17 и регистр 12 гасятся. Это подготавливает устройство синхронизации к принятию сигнала «Переключение каналов, задающего следующее нереключение каналов. Функцию блока 2 канальных импульсов циклового фазирования могут выполнять блоки формирования тактовых синхроимпульсов периферийных устройств, если соответствующие их выходы подключить к входам коммутатора 3. Целесообразность использования одного или другого варианта зависит от расстояния периферийных устройств от центрального устройства. Формула изобретения Многоканальное устройство синхронизации, содержащее формирователь тактовых синхроимпульсов и блок канальных импульсов циклового фазирования, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм при переключении каналов, введены последовательно соединенные коммутатор канальных импульсов циклового фазирования, блок управления и коммутатор канальных задающих импульсов, включенные между выходами блока канальных импульсов циклового фазирования и входом управлепия формирователя тактовых синхроимпульсов, причем второй выход блока управления подключен к входу управления коммутатора канальных импульсов циклового фазирования, на соответствующий вход блока управления подан сигнал «Переключение каналов, а один из выходов формирователя тактовых синхроимпульсов соединен с вторым входом блока управления. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3230309, кл. 178-53, 966.

20-f

11

ffcfleff fvveHiJe .roHOfie/ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации многоканальной системы радиосвязи | 1990 |

|

SU1739502A1 |

| Устройство передачи и приема сигналов телеинформации | 1978 |

|

SU698032A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| ВЕДОМСТВЕННАЯ СИСТЕМА ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА | 2016 |

|

RU2650191C1 |

| Устройство для измерения достоверности цифровой магнитной записи | 1987 |

|

SU1430987A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

Авторы

Даты

1977-06-30—Публикация

1970-02-17—Подача