00

-д

о 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU758550A1 |

| Устройство синхронизации многоканальной системы радиосвязи | 1990 |

|

SU1739502A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1976 |

|

SU650245A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство синхронизации сигналов времени | 1984 |

|

SU1167577A1 |

Изобретение относится к радиотехнике и технике связи и может быть использовано в многоканальных синхронно-адресных системах связи с временным разделением каналов, в которых обмен информацией .между несколькими .приемопередающими станциями осуществляется на. одной частоте в неперекрывающихся интервалах времени. Цель изобретения - повышение точности многосвязной синхронизации при задержках распространения синхросигналов,соизмеримых с длительностью канального интервала. Устройство содержит согла- сованный фильтр 1, блок 2 тактовой синхронизации, первый элемент И 3, блок 4 фазирования, блок 5 канальной синхронизации, блок 6 определения занятых каналов, блок 7 определения задержки, второй элемент И 8, блок 9 определения опережения, распределитель 10, генератор сетки частот. Повышение точности многосвязной синхронизации достигается за счет управления параметрами (фазовыми соотношениями моментов передачи синхросигналов) группового сигнала. Изменение их (если это необходимо) приводит к компрессии группового сигнала. В этом случае частота канальных сигналов синхронизации в меньшей степени зависит от взаимного расположения передатчиков в пространстве, значительно сокращается расстройка входного и опорного сигналов и, следовательно, увеличивается скорость подстройки у каждого из устройств синхронизации. 3 а. п. ф-лы. 10 ил. ; со с

фцг.1

Изобретение относится к радиотехнике и технике связи и может быть использовано в многоканальных синхронно-адресных системах связи с временным разделением каналов, в которых обмен информацией между несколькими приемопередающими станциями осуществляется на одной частоте в неперекрывающихся интервалах времени.

Цель изобретения - повышение точности многосвязной синхронизации при задержках распространения синхросигналов с длительностью канального интервала.

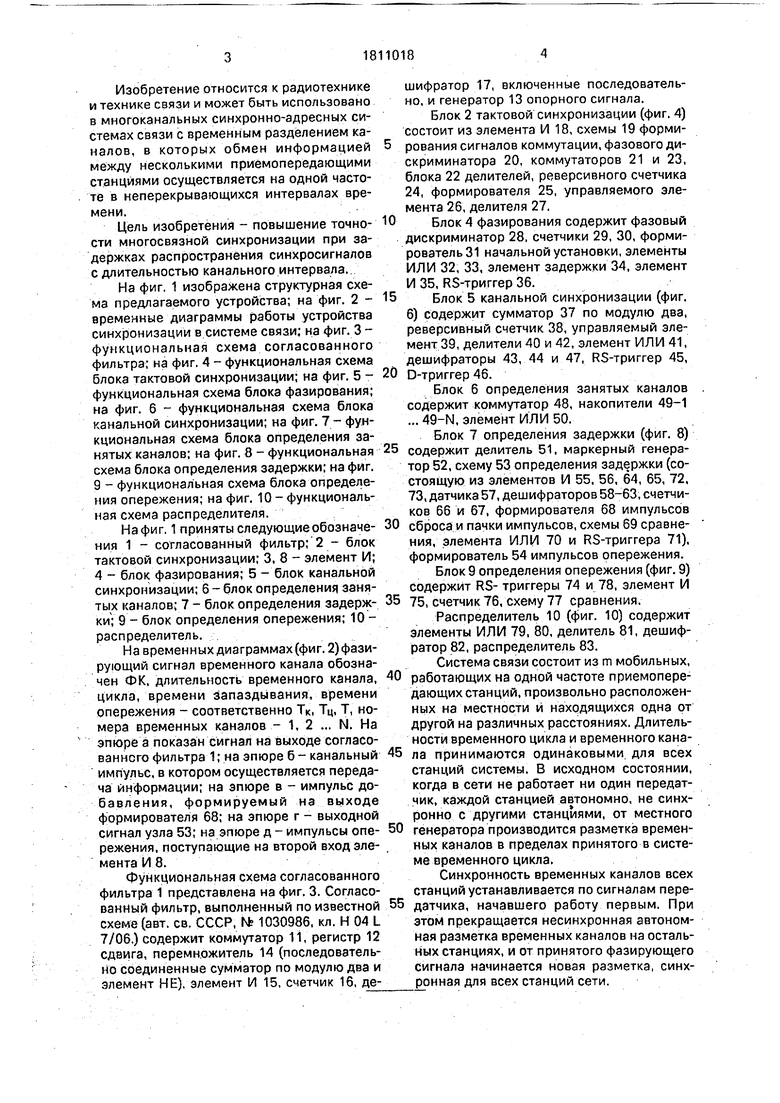

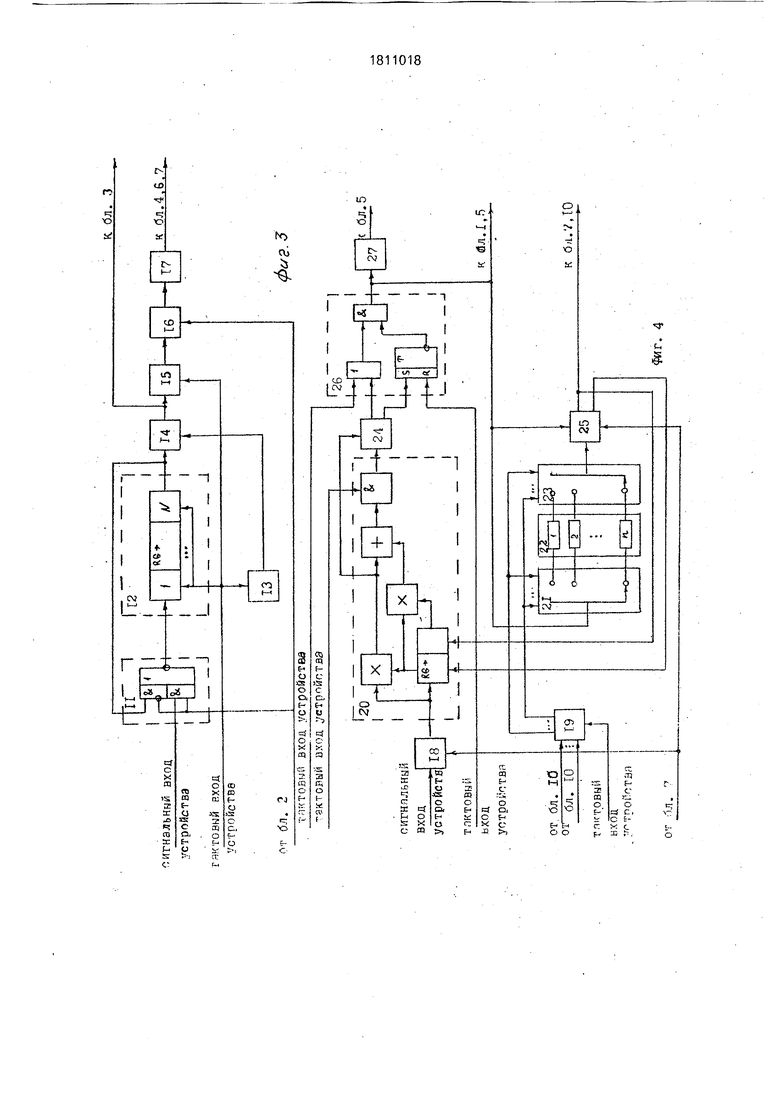

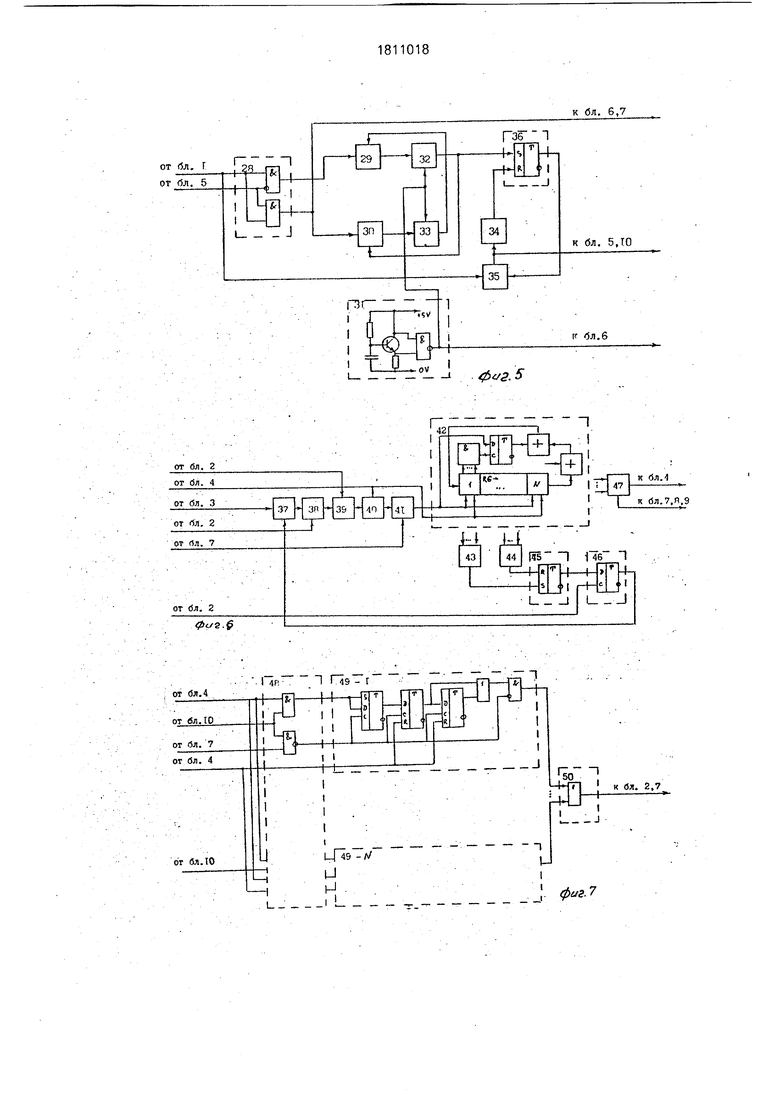

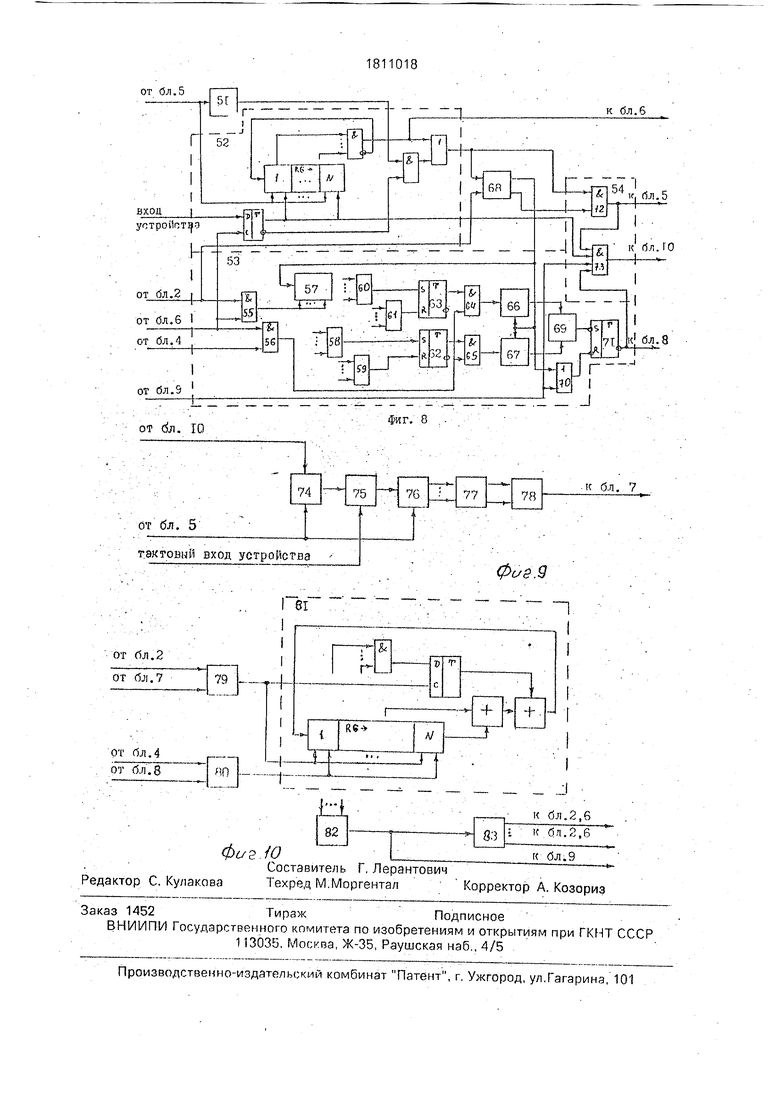

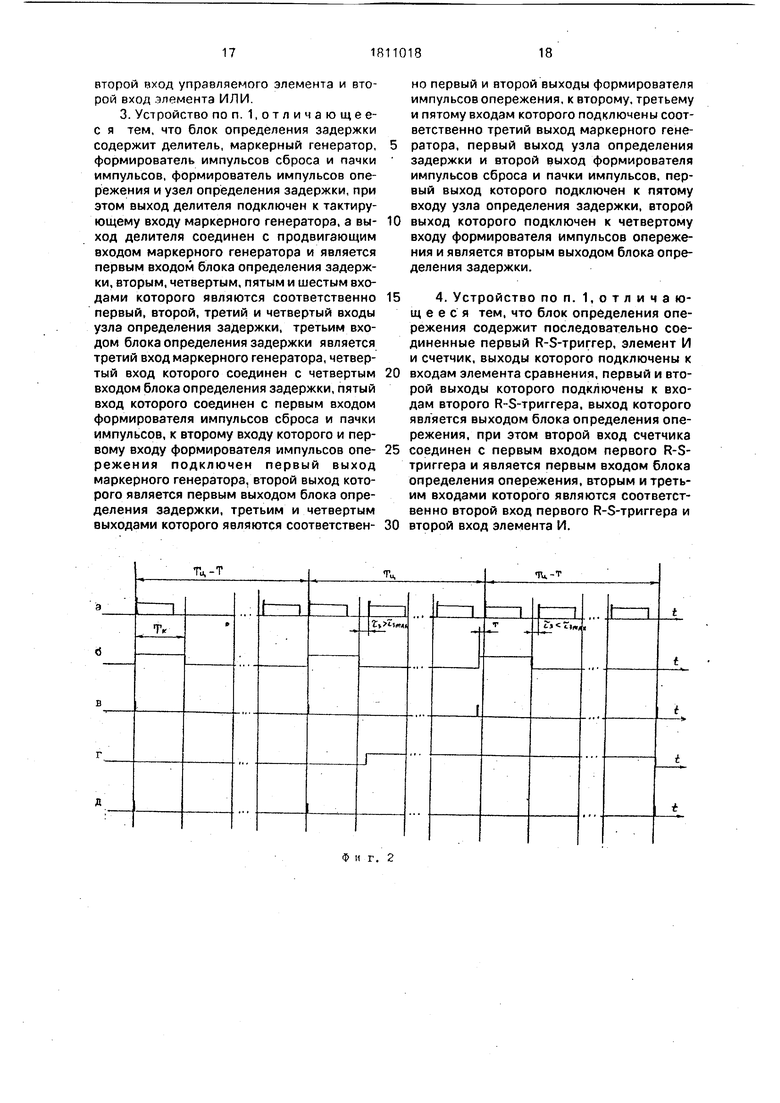

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства синхронизации в системе связи; на фиг. 3 - функциональная схема согласованного фильтра; на фиг. 4 - функциональная схема блока тактовой синхронизации; на фиг. 5 - функциональная схема блока фазирования; на фиг. 6 - функциональная схема блока канальной синхронизации; на фиг. 7 - функциональная схема блока определения занятых каналов; на фиг. 8 - функциональная схема блока определения задержки; на фиг. 9 - функциональная схема блока определения опережения; на фиг. 10 - функциональная схема распределителя.

На фиг. 1 приняты следующие обозначения 1 - согласованный фильтр; 2 - блок тактовой синхронизации; 3, 8 - элемент И; 4 - блок фазирования; 5 - блок канальной синхронизации; 6 - блок определения занятых каналов; 7 - блок определения задержки; 9 - блок определения опережения; 10 - распределитель. .

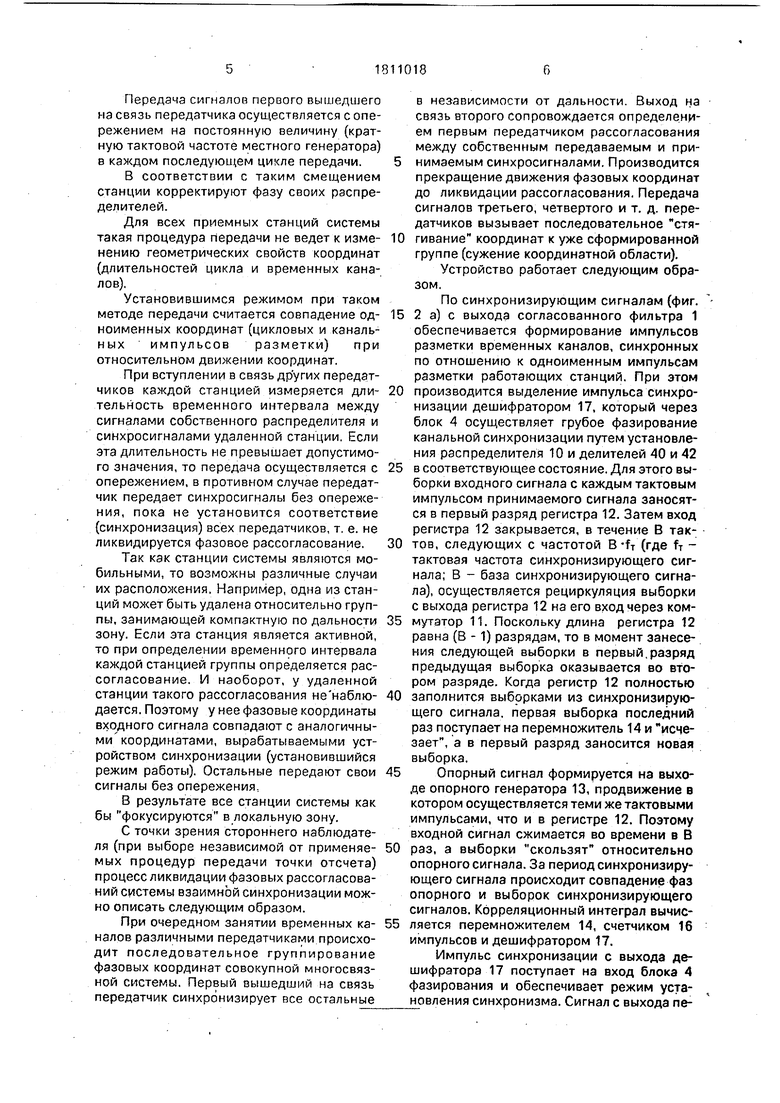

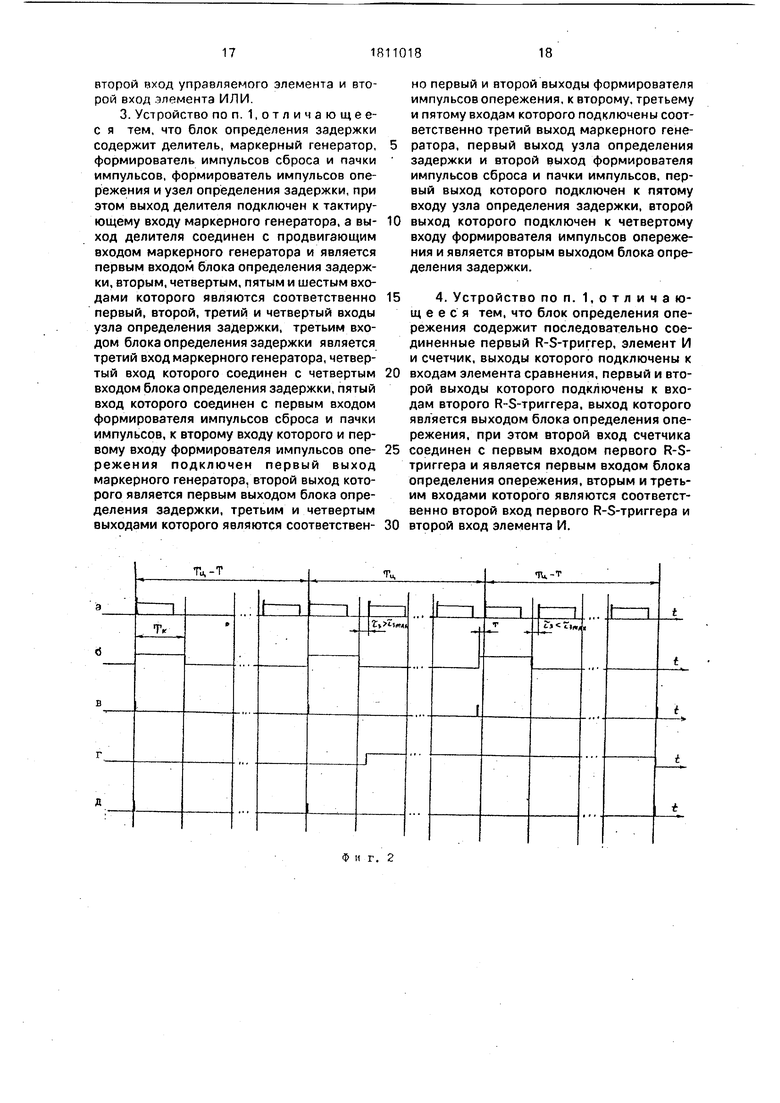

На временных диаграммах (фиг. 2) фазирующий сигнал временного канала обозначен ФК, длительность временного канала, цикла, времени запаздывания, времени опережения - соответственно Тк, Тц, Т, номера временных каналов -1,2 ... N. На эпюре а показан сигнал на выходе согласованного фильтра 1; на эпюре б - канальный импульс, в котором осуществляется передача информации; на эпюре в - импульс добавления, формируемый на выходе формирователя 68; на эпюре г - выходной сигнал узла 53; на эпюре д - импульсы опережения, поступающие на второй вход элемента И 8.

функциональная схема согласованного фильтра 1 представлена на фиг. 3. Согласованный фильтр, выполненный по известной схеме (авт. св. СССР, № 1030986, кл. Н 04 L 7/06.) содержит коммутатор 11, регистр 12 сдвига, перемножитель 14 (последовательно соединенные сумматор по модулю два и элемент НЕ), элемент И 15, счетчик 16, дешифратор 17, включенные последовательно, и генератор 13 опорного сигнала.

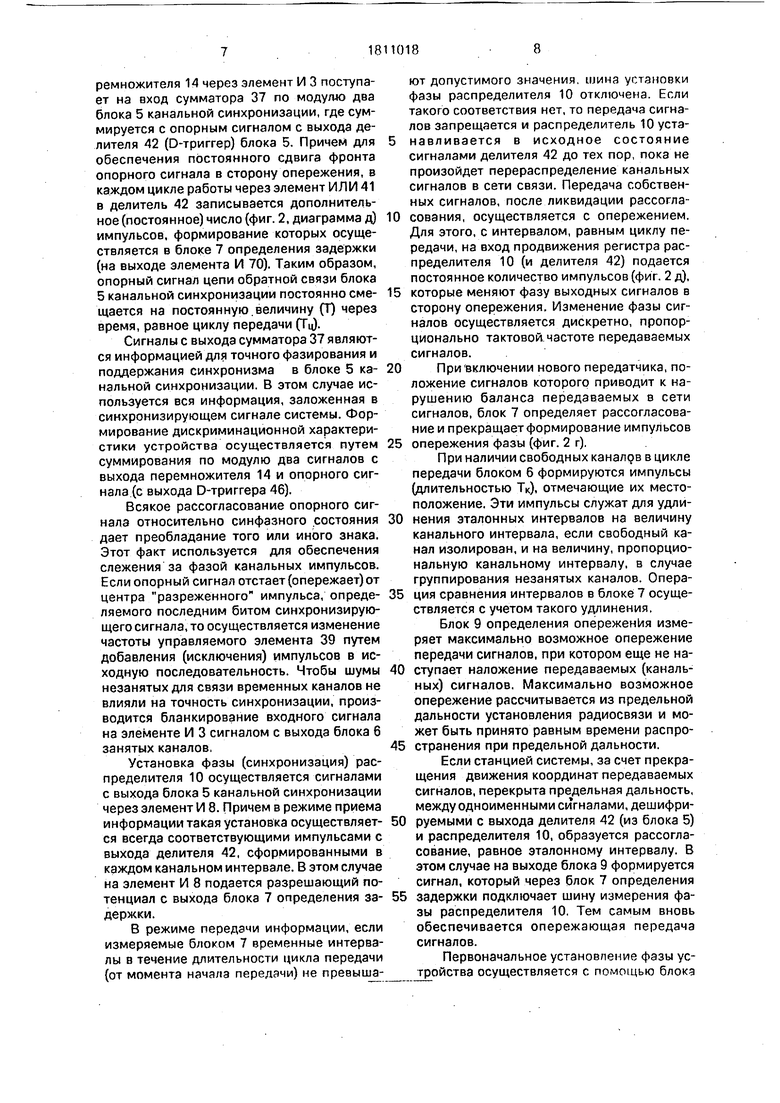

Блок 2 тактовой синхронизации (фиг. 4) состоит из элемента И 18, схемы 19 формирования сигналов коммутации, фазового дискриминатора 20, коммутаторов 21 и 23, блока 22 делителей, реверсивного счетчика 24, формирователя 25, управляемого элемента 26, делителя 27.

0 Блок 4 фазирования содержит фазовый дискриминатор 28, счетчики 29, 30, формирователь 31 начальной установки, элементы ИЛИ 32, 33, элемент задержки 34, элемент И 35, RS-триггер 36.

5 Блок 5 канальной синхронизации (фиг. 6) содержит сумматор 37 по модулю два, реверсивный счетчик 38, управляемый элемент 39, делители 40 и 42, элемент ИЛИ 41, дешифраторы 43, 44 и 47, RS-триггер 45,

0 D-триггер 46.

Блок 6 определения занятых каналов содержит коммутатор 48, накопители 49-1 ... 49-N, элемент ИЛИ 50.

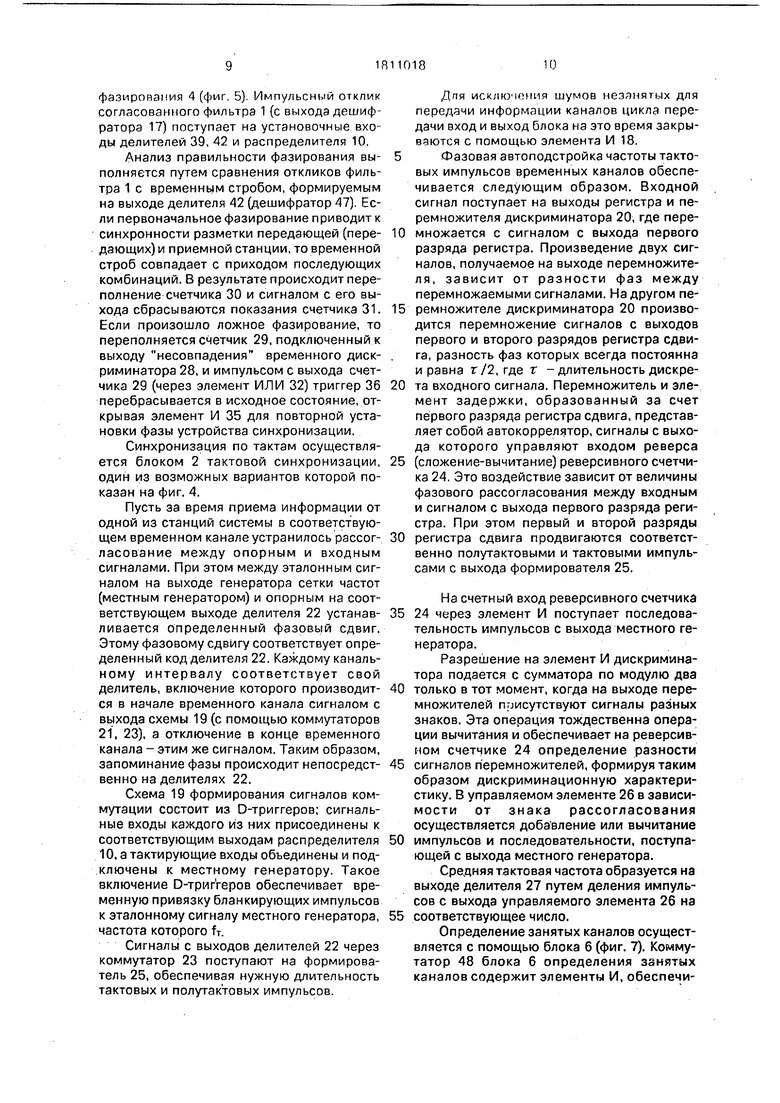

Блок 7 определения задержки (фиг. 8)

5 содержит делитель 51, маркерный генератор 52, схему 53 определения задержки (состоящую из элементов И 55, 56, 64, 65, 72, 73, датчика 57, дешифраторов 58-63, счетчиков 66 и 67, формирователя 68 импульсов

0 сброса и пачки импульсов, схемы 69 сравнения, элемента ИЛИ 70 и RS-триггера 71), формирователь 54 импульсов опережения. Блок 9 определения опережения (фиг. 9) Содержит RS- триггеры 74 и 78, элемент И

5 75, счетчик 76, схему 77 сравнения.

Распределитель 10 (фиг. 10) содержит элементы ИЛИ 79, 80, делитель 81, дешифратор 82, распределитель 83.

Система связи состоит из m мобильных,

0 работающих на одной частоте приемопередающих станций, произвольно расположенных на местности и находящихся одна от другой на различных расстояниях. Длительности временного цикла и временного кана5 ла принимаются одинаковыми, для всех станций системы. В исходном состоянии, когда в сети не работает ни один передатчик, каждой станцией автономно, не синхронно с другими станциями, от местного

0 генератора производится разметка временных каналов в пределах принятого в системе временного цикла.

Синхронность временных каналов всех станций устанавливается по сигналам пере5 датчика, начавшего работу первым. При этом прекращается несинхронная автономная разметка временных каналов на остальных станциях, и от принятого фазирующего сигнала начинается новая разметка, синхронная для всех станций сети.

Передача сигналов первого вышедшего на связь передатчика осуществляется с опережением на постоянную величину (кратную тактовой частоте местного генератора) в каждом последующем цикле передачи.

В соответствии с таким смещением станции корректируют фазу своих распределителей.

Для всех приемных станций системы такая процедура передачи не ведет к изменению геометрических свойств координат (длительностей цикла и временных каналов).

Установившимся режимом при таком методе передачи считается совпадение одноименных координат (цикловых и каналь- ных импульсов разметки) при относительном движении координат.

При вступлении в связь других передатчиков каждой станцией измеряется длительность временного интервала между сигналами собственного распределителя и синхросигналами удаленной станции. Если эта длительность не превышает допустимого значения, то передача осуществляется с опережением, в противном случае передатчик передает синхросигналы без опережения, пока не установится соответствие (синхронизация) всех передатчиков, т. е. не ликвидируется фазовое рассогласование.

Так как станции системы являются мобильными, то возможны различные случаи их расположения. Например, одна из станций может быть удалена относител ьно группы, занимающей компактную по дальности зону. Если эта станция является активной, то при определении временного интервала каждой станцией группы определяется рассогласование. И наоборот, у удаленной станции такого рассогласования не наблю- дается. Поэтому у нее фазовые координаты входного сигнала совпадают с аналогичными координатами, вырабатываемыми устройством синхронизации (установившийся режим работы). Остальные передают свои сигналы без опережения,

В результате все станции системы как бы фокусируются в локальную зону.

С точки зрения стороннего наблюдателя (при выборе независимой от применяемых процедур передачи точки отсчета) процесс ликвидации фазовых рассогласований системы взаимной синхронизации можно описать следующим образом.

При очередном занятии временных каналов различными передатчиками происходит последовательное группирование фазовых координат совокупной многосвязной системы. Первый вышедший на связь передатчик синхронизирует все остальные

в независимости от дальности. Выход на связь второго сопровождается определением первым передатчиком рассогласования между собственным передаваемым и при- нимземым синхросигналами. Производится прекращение движения фазовых координат до ликвидации рассогласования. Передача сигналов третьего, четвертого и т. д. передатчиков вызывает последовательное стя0 гивание координат к уже сформированной группе (сужение координатной области).

Устройство работает следующим образом.

По синхронизирующим сигналам (фиг.

5 2 а) с выхода согласованного фильтра 1 обеспечивается формирование импульсов разметки временных каналов, синхронных по отношению к одноименным импульсам разметки работающих станций. При этом

0 производится выделение импульса синхронизации дешифратором 17, который через блок 4 осуществляет грубое фазирование канальной синхронизации путем установления распределителя 10 и делителей 40 и 42

5 в соответствующее состояние. Для этого выборки входного сигнала с каждым тактовым импульсом принимаемого сигнала заносятся в первый разряд регистра 12. Затем вход регистра 12 закрывается, в течение В так0 тов, следующих с частотой В-fr (где fT - тактовая частота синхронизирующего сигнала; В - база синхронизирующего сигнала), осуществляется рециркуляция выборки с выхода регистра 12 на его вход через ком5 мутатор 11. Поскольку длина регистра 12 равна (В -1) разрядам, то в момент занесения следующей выборки в первый .разряд предыдущая выборка оказывается во втором разряде. Когда регистр 12 полностью

0 заполнится выборками из синхронизирующего сигнала, первая выборка последний раз поступает на перемножитель 14 и исчезает, а в первый разряд заносится новая выборка.

5 Опорный сигнал формируется на выходе опорного генератора 13, продвижение в котором осуществляется теми же тактовыми импульсами, что и в регистре 12. Поэтому входной сигнал сжимается во времени в В

0 раз, а выборки скользят относительно опорного сигнала. За период синхронизирующего сигнала происходит совпадение фаз опорного и выборок синхронизирующего сигналов. Корреляционный интеграл вычис5 ляется перемножителем 14, счетчиком 16 импульсов и дешифратором 17.

Импульс синхронизации с выхода дешифратора 17 поступает на вход блока 4 фазирования и обеспечивает режим установления синхронизма. Сигнал с выхода перемножителя 14 через элемент И 3 поступает на вход сумматора 37 по модулю два блока 5 канальной синхронизации, где суммируется с опорным сигналом с выхода делителя 42 (D-триггер) блока 5. Причем для обеспечения постоянного сдвига фронта опорного сигнала в сторону опережения, в каждом цикле работы через элемент ИЛИ 41 в делитель 42 записывается дополнительное (постоянное) число (фиг. 2, диаграмма д) импульсов, формирование которых осуществляется в блоке 7 определения задержки (на выходе элемента И 70). Таким образом, опорный сигнал цепи обратной связи блока 5 канальной синхронизации постоянно смещается на постоянную.величину (Т) через время, равное циклу передачи (Гц).

Сигналы с выхода сумматора 37 являются информацией для точного фазирования и поддержания синхронизма в блоке 5 канальной синхронизации. В этом случае используется вся информация, заложенная в синхронизирующем сигнале системы. Формирование дискриминационной характеристики устройства осуществляется путем суммирования по модулю два сигналов с выхода перемножителя 14 и опорного сигнала (с выхода D-триггера 46).

Всякое рассогласование опорного сигнала относительно синфазного состояния дает преобладание того или иного знака. Этот факт используется для обеспечения слежения за фазой канальных импульсов. Если опорный сигнал отстает (опережает) от центра разреженного импульса, определяемого последним битом синхронизирующего сигнала, то осуществляется изменение частоты управляемого элемента 39 путем добавления (исключения) импульсов в исходную последовательность. Чтобы шумы незанятых для связи временных каналов не влияли на точность синхронизации, производится бланкирование входного сигнала на элементе И 3 сигналом с выхода блока 6 занятых каналов.

Установка фазы (синхронизация) распределителя 10 осуществляется сигналами с выхода блока 5 канальной синхронизации через элемент И 8. Причем в режиме приема информации такая установка осуществляется всегда соответствующими импульсами с выхода делителя 42, сформированными в каждом канальном интервале. В этом случае на элемент И 8 подается разрешающий потенциал с выхода блока 7 определения задержки.

В режиме передачи информации, если измеряемые блоком 7 временные интервалы в течение длительности цикла передачи (от момента начала передачи) не превышают допустимого значения, шина установки фазы распределителя 10 отключена. Если такого соответствия нет, то передача сигналов запрещается и распределитель 10 устанавливается в исходное состояние сигналами делителя 42 до тех пор, пока не произойдет перераспределение канальных сигналов в сети связи. Передача собственных сигналов, после ликвидации рассогла0 сования, осуществляется с опережением. Для этого, с интервалом, равным циклу передачи, на вход продвижения регистра распределителя 10 (и делителя 42) подается постоянное количество импульсов (фиг. 2 д),

5 которые меняют фазу выходных сигналов в сторону опережения. Изменение фазы сигналов осуществляется дискретно, пропорционально тактовой частоте передаваемых сигналов.

0 При включении нового передатчика, положение сигналов которого приводит к нарушению баланса передаваемых в сети сигналов, блок 7 определяет рассогласование и прекращает формирование импульсов

5 опережения фазы (фиг. 2 г).

При наличии свободных каналрв в цикле передачи блоком 6 формируются импульсы (длительностью Тк), отмечающие их местоположение. Эти импульсы служат для удли0 нения эталонных интервалов на величину канального интервала, если свободный канал изолирован, и на величину, пропорциональную канальному интервалу, в случае группирования незанятых каналов. Опера- 5 ция сравнения интервалов в блоке 7 осуществляется с учетом такого удлинения,

Блок 9 определения опережения измеряет максимально возможное опережение передачи сигналов, при котором еще не на0 ступает наложение передаваемых (канальных) сигналов. Максимально возможное опережение рассчитывается из предельной дальности установления радиосвязи и может быть принято равным времени распро5 странения при предельной дальности.

Если станцией системы, за счет прекращения движения координат передаваемых сигналов, перекрыта предельная дальность, между одноименными сигналами, дешифри0 руемыми с выхода делителя 42 (из блока 5) и распределителя 10, образуется рассогласование, равное эталонному интервалу. В этом случае на выходе блока 9 формируется сигнал, который через блок 7 определения

5 задержки подключает шину измерения фазы распределителя 10. Тем самым вновь обеспечивается опережающая передача сигналов.

Первоначальное установление фазы устройства осуществляется с помощью блока

фазировэиия 4 (фиг. 5). Импульсный отклик согласованного фильтра 1 (с выхода дешифратора 17) поступает на установочные входы делителей 39, 42 и распределителя 10.

Анализ правильности фазирования выполняется путем сравнения откликов фильтра 1 с временным стробом, формируемым на выходе делителя 42 (дешифратор 47). Если первоначальное фазирование приводит к синхронности разметки передающей (передающих) и приемной станции,то временной строб совпадает с приходом последующих комбинаций. В результате происходит переполнение счетчика 30 и сигналом с его выхода сбрасываются показания счетчика 31. Если произошло ложное фазирование, то переполняется счетчик 29, подключенный к выходу несовпадения временного дискриминатора 28, и импульсом с выхода счетчика 29 (через элемент ИЛИ 32) триггер 36 перебрасывается в исходное состояние, открывая элемент И 35 для повторной установки фазы устройства синхронизации.

Синхронизация по тактам осуществляется блоком 2 тактовой синхронизации, один из возможных вариантов которой показан на фиг. 4,

Пусть за время приема информации от одной из станций системы в соответствующем временном канале устранилось рассогласование между опорным и входным сигналами. При этом между эталонным сигналом на выходе генератора сетки частот (местным генератором) и опорным на соответствующем выходе делителя 22 устанавливается определенный фазовый сдвиг. Этому фазовому сдвигу соответствует определенный код делителя 22. Каждому канальному интервалу соответствует свой делитель, включение которого производится в начале временного канала сигналом с выхода схемы 19 (с помощью коммутаторов 21, 23), а отключение в конце временного канала - этим же сигналом. Таким образом, запоминание фазы происходит непосредственно на делителях 22.

Схема 19 формирования сигналов коммутации состоит из D-триггеров; сигнальные входы каждого из них присоединены к соответствующим выходам распределителя 10, а тактирующие входы объединены и подключены к местному генератору. Такое включение D-триг геров обеспечивает временную привязку бланкирующих импульсов к эталонному сигналу местного генератора, частота которого fT.

Сигналы с выходов делителей 22 через коммутатор 23 поступают на формирователь 25, обеспечивая нужную длительность тактовых и полутак товых импульсов.

Для исключения шумов незанятых для передачи информации каналов цикла передачи вход и выход блока на это время закрываются с помощью элемента И 18. Фазовая автоподстройка частоты тактовых импульсов временных каналов обеспечивается следующим образом. Входной сигнал поступает на выходы регистра и перемножителя дискриминатора 20, где перемножается с сигналом с выхода первого разряда регистра. Произведение двух сигналов, получаемое на выходе перемножителя, зависит от разности фаз между перемножаемыми сигналами. На другом перемножителе дискриминатора 20 производится перемножение сигналов с выходов первого и второго разрядов регистра сдвига, разность фаз которых всегда постоянна и равна г/2, где т - длительность дискрета входного сигнала. Перемножитель и элемент задержки, образованный за счет первого разряда регистра сдвига, представляет собой авто коррелятор, сигналы с выхода которого управляют входом реверса

(сложение-вычитание) реверсивного счетчика 24. Это воздействие зависит от величины фазового рассогласования между входным и сигналом с выхода первого разряда регистра. При этом первый и второй разряды

регистра сдвига продвигаются соответственно полутактовыми и тактовыми импульсами с выхода формирователя 25.

На счетный вход реверсивного счетчика

24 через элемент И поступает последовательность импульсов с выхода местного генератора.

Разрешение на элемент И дискриминатора подается с сумматора по модулю два

только в тот момент, когда на выходе перемножителей присутствуют сигналы разных знаков. Эта операция тождественна операции вычитания и обеспечивает на реверсивном счетчике 24 определение разности

сигналов перемножителей, формируя таким образом дискриминационную характеристику. В управляемом элементе 26 в зависимости от знака рассогласования осуществляется добавление или вычитание

импульсов и последовательности, поступающей с выхода местного генератора.

Средняя тактовая частота образуется на выходе делителя 27 путем деления импульсов с выхода управляемого элемента 26 на

соответствующее число.

Определение занятых каналов осуществляется с помощью блока 6 (фиг. 7). Коммутатор 48 блока 6 определения занятых каналов содержит элементы И, обеспечивающие запись информации в первые разряды накопителей, а также логическую схему на элементе И, осуществляющую обнуление разрядов регистров накопителей (кроме первого разряда). Накопители 49 выполнены в виде регистров сдвига с развитой системой установки и дешифрации состояния.

Перевод блока 6 в исходное состояние осуществляется импульсом начальной уста- новки, формируемым в блоке 4 фазирования (cxewta 31 начальной установки), и пЬ сигналу (фиг. 2, б), обеспечивающему передачу информации в выбранном канале цикла (от другого устройства). В результате воздействия этих сигналов регистры (или регистр) устанавливаются в нулевое состояние. Ана- лиз занятости временных каналов производится по текущим значениям состояния кода разрядов накопительных регистров 49 (кроме первого разряда). Продвижение информации в накопительных регистрах осуществляется импульсами, отмечающими соответствующий канал цикла передачи. Канал считается свободным, если состояние кода равно 000..0, в остальных случаях канал считается занятым. Изменение состояния накопительного регистра 49 осуществляется как путем накопления импульсов синхронизации (с выхода дешифра- тора 17), так и в результате прерывания (установки разрядов регистра в нулевое состояние).

При накоплении информации в регистре по .выделенному сигналу фазирующей комбинации в его первый разряд записывается единичное значение. После накопления К-1 (где К - количество разрядов регистра накопителя 49) сигналов фазирующей комбинации, следующих в соответству- ющем канале цикла передачи, на выходе элемента И, подключённого к разрядам регистра накопителя 49, формируется сигнал, отмечающий занятый канал. Текущее состояние всех каналов суммируется на элементе ИЛИ 50.... .

Блок 5 канальной синхронизации (фиг. 6) имеет следующие особенности.

Для организации постоянного смещения опорного сигнала (установившийся ре- жим работы) управляемый делитель выполнен в виде двух делителей 40 и 42, разделенных элементом ИЛИ 41. На делителе 40 осуществляется деление входной последовательности импульсов до частоты, равной частоте передачи сигналов в каналах связи, а на управляемом делителе 42 - до канальной частоты (TK). Через элемент ИЛИ 41 производится добавление через цикл передачи постоянного количества импульсов

фиг. 2, д). При этом выходные сигналы делиеля 42 смещаются в сторону опережения относительно их положения в предыдущем цикле работы.

Для улучшения динамики работы устройства опорный сигнал, формируемый на выходе RS-триггера 45, замещается полтактовыми импульсами (с выхода блока 2 актовой синхронизации). Такое замещение осуществляется на D-триггере 46. При этом возможные смещения, которые отслеживает следящая система, за счет введения перекрестной связи с выхода блока 2, всегда равно или кратно длительности элементарного символа входного сигнала. Дискриминационная характеристика в этом случае имеет прямоугольную форму. Кроме того, в схеме вместо сигналов местного генератора, традиционно используемых в замкнутых системах канальной синхронизации для слежения за канальными сигналами, используется последовательность усредненной частоты с выхода управляемого элемента 26 блока 2 тактовой синхронизации. Эта последовательность поступает на вход управляемого делителя 40 блока 5 канальной синхронизации, обеспечивая, в свою очередь, усреднение канальных частот. Использование усредненной частоты для слежения за канальными сигналами повышает точность и помехоустойчивость канального фазирования системы взаимной синхронизации. Для той же цели производится анализ незанятых для связи временных каналов блоком 6, который блокирует вход канальной синхронизации в случае обнаружения незанятых каналов.

Блок 7 определения задержки (фиг. 8) работает следующим образом. Заявка на передачу информации (в виде положительного потенциала) (фиг. 2, б) поступает на второй вход устройства и замещается на импульс, отмечающий начало ближайшего свободного канала (на D-триггере маркерного генератора 52). С этого момента маркерный генератор 52,. продвигаемый импульсами, отмечающими начало каждого временного канала, формирует последовательность импульсов, длительность которых равна длительности канального интервала, а период - длительности цикла передачи. Этот сигнал используется для установки в нулевое состояние соответствующего накопителя 49 блока 6, а также для изменения фазы выходных сигналов распределителя 10 и опорного сигнала делителя 42 в режиме передачи информации. В этом режиме один из входов для двухвходового элемента И (из блока 52) блокирован и на вход элемента И

73 через элемент ИЛИ (из блока 52) поступает последовательность импульсов, отмечающих закрепленный канал передачи информации. На другой вход элемента И 72 в это время поступают сигналы (фиг. 2, в) с выхода формирователя 68 в виде пачки импульсов. Количество последних выбирается исходя из возможной величины измерения фазы опорного сигнала делителя 42.

При формировании сигналов, обеспечивающих опережающую передачу информации (выходных сигналов распределителя) 10), на вход элемента И 73 воздействуют потенциалы D-триггеров из блока 52 и RS- триггера 72. Эти воздействия служат для обеспечения прохождения импульсов с выхода элемента И 72 на выход элемента И 73. Первый из них определяется наличием заявки на передачу информации. Второй образуется схемой 53 определения задержки. При этом измеряется длительность временных интервалов между соседними синхросигналами путем сравнения кодов счетчиков 66 и 67.

Производится заполнение счетчиков 66 и 67 импульсами синхронизации (с выхода временного дискриминатора из блока 4), следующими в течение интервала, равного циклу передачи. Заполнение производится при помощи датчика 57 интервалов времени, дешифраторов 58, 59, 62 и 60, 61, 63 и временного дискриминатора на элементах И64и65.

Импульсы с выхода формирователя 68 устанавливают датчик 57 интервалов времени в состояние, С которого начинается изме- рение временных интервалов. Дешифратором, выполненным на элементах 57, 59, 62, формируется момент окончания (последнего би та) последующего синхросигнала, а дешифратором 60, 61, 63 фиксируется второй интервал, дополнительно включающий отрезок времени возможных запаздываний синхросигналов. Если такое запаздывание существует хотя бы у одного из проходящих синхросигналов, то на выходе совпадения временного дискриминатора (выход элемента И 65) импульс не формируется и значение числа, записанное за цикл (или несколько циклов) работы в счетчик 67, будет меньше числа, записанного в счетчик 63. В этом случае на выходе RS-триггера 71 образуется сигнал, запрещающий формирование сигналов опережения на выходе элемента И 73 (фиг. 2, г).

Если запаздываний синхросигналов нет, показания счетчиков 66, 67 будут одинаковы, т. е. запрещение формирования не образуется. Удлинение эталонного интервала, вызванное наличием свободного временного канала в цикле передачи,

обеспечивается прерыванием следования продвигающихся импульсов датчика 57 (элементом И 55), поступающих с выхода блока 2 тактовой синхронизации. 5Если заявка на передачу информации отсутствует, то на вход двухвходовогО элемента И (из блока 51) поступает потенциал, который обеспечивает формирование опорного сигнала (с выхода делителя 42) с

0 необходимым опережением. При этом на вход элемента И 72 с делителя 51 поступает последовательность импульсов с периодом Гц, образованная путем деления канальных импульсов разметки. В период следования

5 сигналов делителя 52 на выходе элемента И 72 формируются импульсы (фиг. 2, д). которые поступают на вход делителя 42 (из блока 5).

Блок 9 определения опережения пред0 ставляет собой пороговый измеритель интервалов времени.

Импульсы, определяющие начало каждого временного канала, с распределителя 10 и делителя 42, воздействуя на RS-триггер

5 74, образуют на его выходе сигнал рассогласования Т (фиг. 2, а). Полученный сигнал на элементе И 75 преобразуется в пачку импульсов, количество импульсов в которой пропорционально рассогласованию. Для

0 этого на выходе элемента И 75 кроме сигнала, определяющего рассогласование, подаются высокочастотные .импульсы с генератора сетки частот 11, Количество им- пуЛьсов в пачке затем преобразуется в код

5 (числа А), записанный в счетчик 76. На схеме сравнения 77 число А сравнивается с числом В, сформированным на постоянном запоминающем устройстве.

Если А В, то на соответствующем выQ ходе схемы 77 формируется импульс, поддерживающий RS-триггер 78 в состоянии, при котором запрещается формирование сигналов опережения на выходах распределителя 10. через блок 53.

5 Если А - В, то RS-триггер 78 меняет состояние и блокирует выход схемы 53 определения задержки.

На выходах распределителя 10 в этом случае формируются сигналы, изменяющие

0 свою фазу (на постоянную величину) через цикл передачи.

По сравнению с прототипом повышение точности многосвязной синхронизации достигается за счет управления параметрами

5 (фазовыми соотношениями моментов передачи синхросигналов) группового.сигнала. Изменение их (если это необходимо) приводит к компрессии группового сигнала. В этом случае частота канальных сигналов синхронизации в меньшей степени зависит

от взаимного расположения передатчиков в пространстве, значительно сокращается расстройка входного и опорного сигналов и, следовательно, увеличивается скорость подстройки у каждого из устройств синхро- низации.

Повышение точности синхронизации устройствами обеспечивается за счет введения в них блока определения занятых каналов, блока определения задержки, блока определения опережения и двух элементов И.

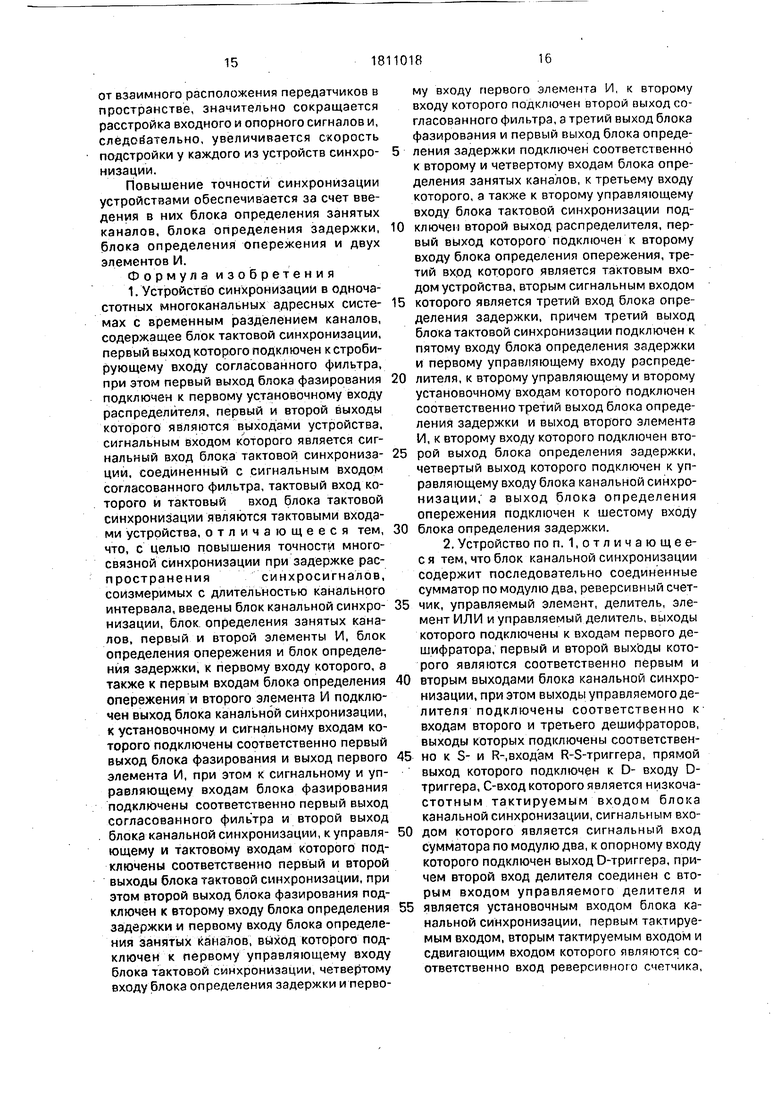

Формула изобретения 1. Устройство синхронизации в одноча- стотных многоканальных адресных систе- мах с временным разделением каналов, содержащее блок тактовой синхронизации, первый выход которого подключен к строби- рующему входу согласованного фильтра, при этом первый выход блока фазирования подключен к первому установочному входу распределителя, первый и второй выходы которого являются выходами устройства, сигнальным входом которого является сигнальный вход блока тактовой синхрониза- ции, соединенный с сигнальным входом согласованного фильтра, тактовый вход которого и тактовый вход блока тактовой синхронизации являются тактовыми входами устройства, отличающееся тем, что, с целью повышения точности многосвязной синхронизации при задержке распространениясинхросигналов, соизмеримых с длительностью канального интервала, введены блок канальной синхро- низации, блок, определения занятых каналов, первый и второй элементы И, блок определения опережения и блок определения задержки, к первому входу которого, а также к первым входам блока определения опережения и второго элемента И подключен выход блока канальной синхронизации, к установочному и сигнальному входам которого подключены соответственно первый выход блока фазирования и выход первого элемента И, при этом к сигнальному и управляющему входам блока фазирования подключены соответственно первый выход согласованного фильтра и второй выход блока канальной синхронизации, куправля- ющему и тактовому входам которого подключены соответственно первый и второй выходы блока тактовой синхронизации, при этом второй выход блока фазирования подключен к второму входу блока определения задержки и первому входу блока определения занятых каналов, выход которого подключен к первому управляющему входу блока тактовой синхронизации, четвертому входу блока определения задержки и первому входу первого элемента И, к второму входу которого подключен второй выход согласованного фильтра, а третий выход блока фазирования и первый выход блока определения задержки подключен соответственно к второму и четвертому входам блока определения занятых каналов, к третьему входу которого, а также к второму управляющему входу блока тактовой синхронизации подключен второй выход распределителя, первый выход которого подключен к второму входу блока определения опережения, третий вход которого является тактовым входом устройства, вторым сигнальным входом которого является третий вход блока определения задержки, причем третий выход блока тактовой синхронизации подключен к пятому входу блока определения задержки и первому управляющему входу распределителя, к второму управляющему и второму установочному входам которого подключен соответственно третий выход блока определения задержки и выход второго элемента И, к второму входу которого подключен второй выход блока определения задержки, четвертый выход которого подключен к управляющему входу блока канальной синхронизации; а выход блока определения опережения подключен к шестому входу блока определения задержки.

второй вход управляемого элемента и второй вход элемента ИЛИ.

но первый и второй выходы формирователя импульсов опережения, к второму, третьему и пятому входам которого подключены соответственно третий выход маркерного генератора, первый выход узла определения задержки и второй выход формирователя импульсов сброса и пачки импульсов, первый выход которого подключен к пятому входу узла определения задержки, второй выход которого подключен к четвертому входу формирователя импульсов опережения и является вторым выходом блока определения задержки.

входам элемента сравнения, первый и второй выходы которого подключены к входам второго R-S-триггера. выход которого является выходом блока определения опережения, при этом второй вход счетчика

соединен с первым входом первого R-S- триггера и является первым входом блока определения опережения, вторым и третьим входами которого являются соответственно второй вход первого R-S-триггера и

второй вход элемента И.

TV-T

Фиг. 2

актовый вход .устройства

тлктовыи

ьход устройства

ВХОД|

то oil о т ал I

от б л.

Пго

&

t Ол.5

к йл.1,5

Фиг. 4

к 6л. 6,7

от бл.5

5Г

вход

уотроПот

от (5л.2

от бл.6 I от бл.4

от бл.З

от бл. 10

от бл. 5

тактовый вход устройства

81

Jк бл.6

А Г4 к, йл.5 У2|

к бл.ГО

7Т

ic1 бл. 8

Фиг. 8 ..0

П.

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-04-23—Публикация

1989-12-25—Подача