Изобретение относится к электросвязи и может быть использовано в приемных устройствах синхронизации по циклам систем передачи дискретных сообщений.

Известно устройство для синхронизации по циклам по а.с. СССР №1085006, кл. Н04L 7/08, опубл. 07.04.84, Бюл. №13, содержащее, как и предлагаемое устройство, опознаватель синхросигнала, регистр сдвига, элемент ИЛИ, первый, второй и третий элемент И, а также формирователь цикловых импульсов, сигнальный вход, тактовый вход и выход. Тактовый вход формирователя цикловых импульсов объединен с тактовым входом регистра сдвига и тактовым входом опознавателя синхросигнала и является тактовым входом устройства, а информационный вход устройства подключен к сигнальному входу опознавателя синхросигнала, а выход формирователя цикловых импульсов, являющийся выходом устройства, совместно подключен ко второму входу третьего элемента И, а также ко второму входу триггера, выход которого подключен ко второму входу первого элемента И. Кроме того, известное устройство содержит дешифратор заданного состояния и дополнительный регистр сдвига. При этом выход формирователя цикловых импульсов также совместно подключен к тактовому входу дополнительного регистра сдвига. Дополнительный выход регистра сдвига подключен к входу дешифратора заданного состояния, выход которого совместно подключен к первому входу триггера и первому входу второго элемента И, а выход третьего элемента И соединен с сигнальным входом дополнительного регистра сдвига, выходы которого подключены ко второй группе входов второго элемента И. Кроме того, выход опознавателя синхросигнала также объединен с первым входом элемента И, а также с первым входом элемента ИЛИ, выход которого соединен с сигнальным входом регистра сдвига, основной выход которого соединен с первым входом первого элемента И, выход которого соединен со вторым входом элемента ИЛИ, а выход второго элемента И подключен к входу сброса формирователя цикловых импульсов. Недостатком известного устройства является низкое быстродействие при высокой вероятности ошибочного приема синхрогрупп, определяемое временем восстановления циклового синхронизма, вызванное фиксированностью циклов испытания по выходу устройства из синхронизма. Состояние выхода из синхронизма определяется, если количество подряд искаженных синхрогрупп достигнет определенного фиксированного числа, которое при плохом качестве канала может достигать больших величин. Фиксированное задание определенного количества циклов испытания по выходу устройства из синхронизма может привести при истинном сбое циклового синхросигнала к увеличению времени проверки по выходу из синхронизма, что в свою очередь приведет к увеличению времени восстановления синхронизма.

Наиболее близким к предлагаемому является устройство для цикловой синхронизации по патенту РФ №2284665, кл. Н04L 7/08, опубл. 27.09.2006, Бюл. №27, прототип, содержащий, как и предлагаемое устройство, опознаватель синхросигнала, сумматор, блок регистров сдвига, решающий узел, формирователь цикловых импульсов, счетчик циклов, третий блок сравнения, счетчик искаженных синхроимпульсов, счетчик общего числа синхроимпульсов, триггер, счетчик тактовых импульсов, первый элемент И, блок выбора порога, сигнальный вход, тактовый вход и выход. При этом опознаватель синхросигнала содержит регистр сдвига, обнаружитель ошибок в синхрогруппе и формирователь веса отклика на синхросигнал. Решающий узел содержит первый блок сравнения, блок памяти, блок вычитания, второй блок сравнения, счетчик сравнения, второй элемент И, третий элемент И, элемент ИЛИ. Причем сигнальный вход устройства соединен с сигнальным входом опознавателя синхросигнала. Сигнальным входом опознавателя синхросигнала является информационный вход регистра сдвига, выход которого подключен к входу обнаружителя ошибок в синхрогруппе. Тактовый вход опознавателя синхросигнала соединен с тактовыми входами регистра сдвига и формирователя веса отклика на синхросигнал. Первый выход обнаружителя ошибок в синхрогруппе подключен к входу формирователя веса отклика на синхросигнал. При этом второй выход обнаружителя ошибок в синхрогруппе является дополнительным выходом опознавателя синхросигнала и подключен к входу данных счетчика искаженных синхроимпульсов. Выход формирователя веса отклика на синхросигнал соединен с первым входом сумматора, выход которого совместно подключен к сигнальному входу блока регистров сдвига и к первому входу третьего блока сравнения. Основной выход блока регистров сдвига подключен ко второму входу сумматора, а дополнительный выход - к сигнальному входу решающего узла. При этом выход первого блока сравнения подключен к входу управления блока памяти, выход которого совместно подключен ко второму входу первого блока сравнения и первому входу блока вычитания. Второй вход блока вычитания объединен с входом данных блока памяти, первым входом первого блока сравнения и является сигнальным входом решающего узла. Выход блока вычитания подключен ко второму входу второго блока сравнения, выход которого соединен с входом сброса счетчика сравнения. Выход счетчика сравнения совместно подключен ко второму входу второго элемента И, а также к первому входу третьего элемента И. Выход второго элемента И, а также третьего элемента И подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к входу сброса блока памяти и является выходом решающего узла. При этом входом управления, первым и вторым дополнительными входами управления и тактовым входом решающего узла являются соответственно первый вход первого блока сравнения, первый вход второго элемента И, второй вход третьего элемента И, а также тактовый вход счетчика сравнения. Выход решающего узла совместно подключен к входам сброса формирователя цикловых импульсов, блока регистров сдвига, счетчика циклов и третьего блока сравнения. Вход управления, первый и второй дополнительные входы управления решающего узла соединены соответственно с выходом блока выбора порога, выходом третьего блока сравнения и с выходом устройства. Тактовый вход формирователя цикловых импульсов объединен с первым входом элемента И, тактовыми входами опознавателя синхросигнала, решающего узла, блока регистров сдвига, счетчика искаженных синхроимпульсов и счетчика тактовых импульсов. Выход счетчика искаженных синхроимпульсов соединен с адресным входом блока выбора порога. Выход формирователя цикловых импульсов совместно подключен к входу управления счетчика искаженных синхроимпульсов, счетному входу счетчика циклов и входу установки триггера, а вход сброса триггера соединен с выходом счетчика тактовых импульсов. Выход триггера подключен ко входу сброса счетчика тактовых импульсов и второму входу первого элемента И, выход которого соединен с тактовым входом счетчика общего числа синхроимпульсов. Выход счетчика общего числа синхроимпульсов соединен с входом сброса счетчика искаженных синхроимпульсов и входом управления блока выбора порога. При этом сигнальный вход опознавателя синхросигнала, тактовый вход формирователя цикловых импульсов и выход формирователя цикловых импульсов являются соответственно сигнальным входом, тактовым входом и выходом устройства. Кроме того, известное устройство содержит также блок выбора максимального веса отклика, второй блок выбора порога, блок выбора коэффициента счета. При этом выход счетчика искаженных синхроимпульсов также совместно соединен с адресными входами блока выбора максимального веса отклика, второго блока выбора порога и блока выбора коэффициента счета, а выход счетчика общего числа синхроимпульсов также совместно соединен с входами управления блока выбора максимального веса отклика, второго блока выбора порога и блока выбора коэффициента счета. Выход блока выбора максимального веса отклика соединен со вторым входом формирователя веса отклика на синхросигнал, третий вход которого соединен также со вторым выходом обнаружителя ошибок в синхрогруппе. Выход второго блока выбора порога соединен со вторым входом третьего блока сравнения, выход блока выбора коэффициента счета соединен с входом данных счетчика циклов, выход которого соединен с входом управления третьего блока сравнения. Недостатком известного устройства является низкое быстродействие при высокой вероятности ошибочного приема синхроимпульсов, определяемое временем восстановления циклового синхронизма, вызванное фиксированностью циклов испытания по выходу устройства из синхронизма. Состояние выхода из синхронизма определяется, если сумма накопления откликов опознавателя синхросигнала на позиции истинного синхросигнала за k циклов испытания будет ниже пороговой величины накопления откликов q. При этом количество циклов испытания k по выходу устройства из синхронизма и пороговая величина накопления q выбираются в зависимости от вероятности ошибочного приема синхроимпульсов. Однако фиксированное задание определенного количества циклов испытания k по выходу устройства из синхронизма может привести при истинном сбое циклового синхросигнала к увеличению времени проверки по выходу из синхронизма (при плохом качестве канала k может достигать больших величин), что в свою очередь приведет к увеличению времени восстановления синхронизма.

Особенностью передачи детерминированного циклового синхросигнала является периодичность его повторения на одних и тех же позициях цикла передачи группового сигнала. При этом опознаватель синхросигнала может распознать в принимаемом групповом сигнале не только истинные синхрогруппы, но и ложные, случайно сформированные на информационных позициях цикла. На выходе опознавателя синхросигнала в зависимости от числа неискаженных синхроимпульсов формируются отклики в виде весовых коэффициентов (при допустимом числе искаженных синхросимволов) и нулей (при превышении допустимого числа искаженных синхросимволов). Требуемая достоверность принятия решения решающим узлом достигается за счет накопления откликов опознавателя синхросигнала в блоке регистров сдвига. В режиме синхронизма при определении решающим узлом позиции циклового синхросигнала производится сброс блока регистров сдвига и фазирование формирователя цикловых импульсов. При обнаружении истинного синхросигнала фаза начальной установки формирователя цикловых импульсов не изменится и устройство для цикловой синхронизации останется в состоянии синхронизма. При плохом качестве канала связи возможен прием синхрогрупп с искаженными синхроимпульсами. При этом формируемые весовые коэффициенты на выходе опознавателя уменьшают свои значения. В блоке регистров сдвига в ячейках (разрядах) соответствующих позиции истинного синхросигнала будет наблюдаться уменьшение плотности накопления откликов опознавателя синхросигнала. При приеме синхрогруппы с количеством искаженных синхросимволов больше допустимого числа на выходе опознавателя синхросигнала формируется "нулевой" отклик и накопление синхроинформации в ячейках блока регистров сдвига, соответствующих истинным синхрогруппам, не осуществляется. При этом при истинном сбое циклового синхросигнала наблюдается более резкое уменьшение плотности накопления откликов опознавателя синхросигнала (в блоке регистров сдвига в ячейках, соответствующих позиции истинного синхросигнала) по сравнению со случаем приема синхрогрупп с искаженными синхроимпульсами. Распознание опознавателем синхросигнала кодовых групп на информационных позициях цикла приводит к накоплению откликов в ячейках блока регистров сдвига, соответствующих ложным синхрогруппам. При этом при регулярном повторении на некоторой информационной позиции цикла ложной синхрогруппы и случайном искажении истинной синхрогруппы может произойти установка формирователя цикловых импульсов в ложную фазу, т.е. может произойти сбой циклового синхронизма, хотя истинные синхрогруппы будут приходить на заданной позиции цикла. Повышение помехоустойчивости устройства достигается определением состояния выхода из циклового синхронизма. Состояние выхода из синхронизма определяется, если сумма накопления откликов опознавателя синхросигнала на позиции истинного синхросигнала за k циклов будет ниже пороговой величины накопления откликов q. При этом количество циклов испытания k по выходу устройства из синхронизма и пороговая величина накопления q выбираются в зависимости от вероятности ошибочного приема синхросимволов. При этом при плохом качестве канала число k может достигать больших значений. Поэтому фиксированное задание определенного количества циклов испытания k по выходу устройства из синхронизма приводит при истинном сбое циклового синхросигнала к задержке времени проверки по выходу устройства из синхронизма (до k циклов), хотя устройство может определить потерю синхронизма раньше. Так как восстановление синхронизма после его сбоя осуществляется при возникновении одновременно двух событий: определения решающим узлом новой позиции циклового синхросигнала и обнаружения потери циклового синхронизма, то увеличение времени определения выхода устройства из синхронизма приводит к увеличению времени восстановления синхронизма, что ухудшает качественные показатели систем передачи дискретных сообщений. Указанные факторы предъявляют повышенные требования к увеличению быстродействия устройства для синхронизации по циклам при высокой вероятности ошибочного приема синхроимпульсов.

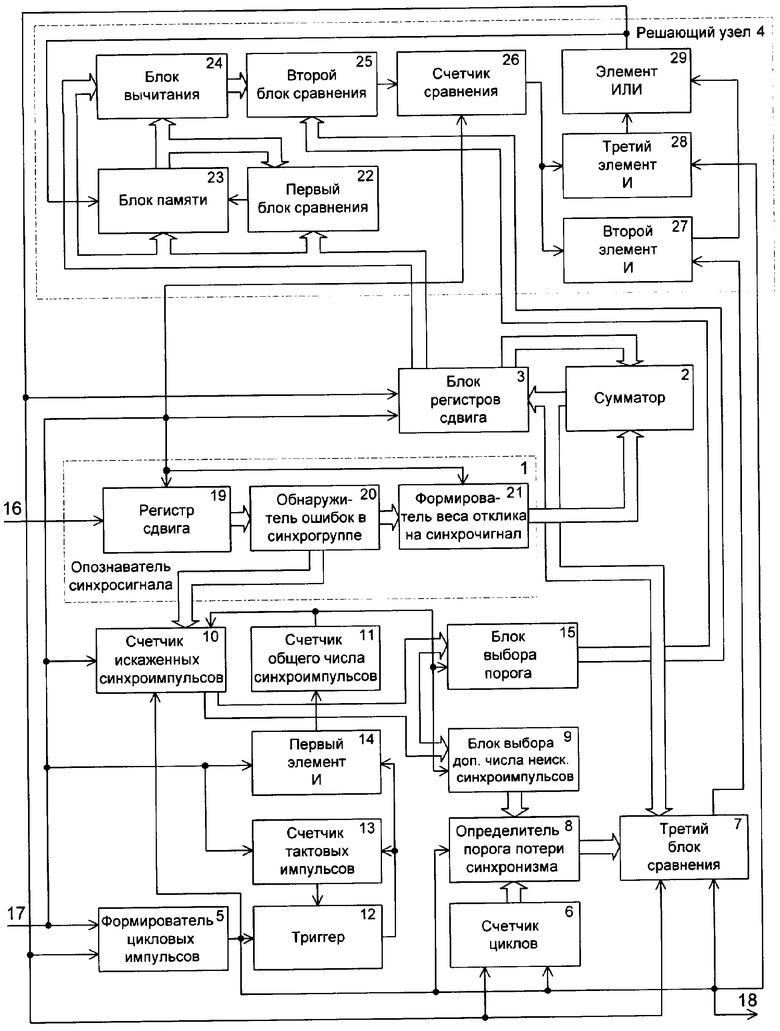

Устройство для цикловой синхронизации содержит опознаватель синхросигнала, сумматор, блок регистров сдвига, решающий узел, формирователь цикловых импульсов, счетчик циклов, третий блок сравнения, счетчик искаженных синхроимпульсов, счетчик общего числа синхроимпульсов, триггер, счетчик тактовых импульсов, первый элемент И, блок выбора порога, сигнальный вход, тактовый вход и выход. При этом опознаватель синхросигнала содержит регистр сдвига, обнаружитель ошибок в синхрогруппе и формирователь веса отклика на синхросигнал. Решающий узел содержит первый блок сравнения, блок памяти, блок вычитания, второй блок сравнения, счетчик сравнения, второй элемент И, третий элемент И, элемент ИЛИ. Причем сигнальный вход устройства соединен с сигнальным входом опознавателя синхросигнала. Сигнальным входом опознавателя синхросигнала является информационный вход регистра сдвига, выход которого подключен к входу обнаружителя ошибок в синхрогруппе. Тактовый вход опознавателя синхросигнала соединен с тактовыми входами регистра сдвига и формирователя веса отклика на синхросигнал. Первый выход обнаружителя ошибок в синхрогруппе подключен к входу формирователя веса отклика на синхросигнал. При этом второй выход обнаружителя ошибок в синхрогруппе является дополнительным выходом опознавателя синхросигнала и подключен к входу данных счетчика искаженных синхроимпульсов. Выход формирователя веса отклика на синхросигнал является основным выходом опознавателя синхросигнала и соединен с первым входом сумматора, выход которого совместно подключен к сигнальному входу блока регистров сдвига и к первому входу третьего блока сравнения. Основной выход блока регистров сдвига подключен ко второму входу сумматора, а дополнительный выход - к сигнальному входу решающего узла. При этом выход первого блока сравнения подключен к входу управления блока памяти, выход которого совместно подключен ко второму входу первого блока сравнения и первому входу блока вычитания. Второй вход блока вычитания объединен с входом данных блока памяти, первым входом первого блока сравнения и является сигнальным входом решающего узла. Выход блока вычитания подключен ко второму входу второго блока сравнения, выход которого соединен с входом сброса счетчика сравнения. Выход счетчика сравнения совместно подключен ко второму входу второго элемента И, а также к первому входу третьего элемента И. Выход второго элемента И, а также третьего элемента И подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к входу сброса блока памяти и является выходом решающего узла. При этом входом управления, первым и вторым дополнительными входами управления и тактовым входом решающего узла являются соответственно первый вход первого блока сравнения, первый вход второго элемента И, второй вход третьего элемента И, а также тактовый вход счетчика сравнения. Выход решающего узла совместно подключен к входам сброса формирователя цикловых импульсов, блока регистров сдвига, счетчика циклов и третьего блока сравнения. Вход управления, первый и второй дополнительные входы управления решающего узла соединены соответственно с выходом блока выбора порога, выходом третьего блока сравнения и с выходом устройства. Тактовый вход формирователя цикловых импульсов объединен с первым входом элемента И, тактовыми входами опознавателя синхросигнала, решающего узла, блока регистров сдвига, счетчика искаженных синхроимпульсов и счетчика тактовых импульсов. Выход счетчика искаженных синхроимпульсов соединен с адресным входом блока выбора порога. Выход формирователя цикловых импульсов совместно подключен к входу управления счетчика искаженных синхроимпульсов, счетному входу счетчика циклов и входу установки триггера, а вход сброса триггера соединен с выходом счетчика тактовых импульсов. Выход триггера подключен ко входу сброса счетчика тактовых импульсов и второму входу первого элемента И, выход которого соединен с тактовым входом счетчика общего числа синхроимпульсов. Выход счетчика общего числа синхроимпульсов соединен с входом сброса счетчика искаженных синхроимпульсов и входом управления блока выбора порога. При этом сигнальный вход опознавателя синхросигнала, тактовый вход формирователя цикловых импульсов и выход формирователя цикловых импульсов являются соответственно сигнальным входом, тактовым входом и выходом устройства.

Технический результат при осуществлении изобретения - повышение быстродействия устройства для цикловой синхронизации при высокой вероятности ошибочного приема синхроимпульсов достигается введением блока выбора допустимого числа неискаженных синхроимпульсов и определителя порога потери синхронизма. При этом выход счетчика искаженных синхроимпульсов подключен также к адресному входу блока выбора допустимого числа неискаженных синхроимпульсов, а выход формирователя цикловых импульсов совместно подключен также к входу управления определителя порога потери синхронизма и входу управления третьего блока сравнения. Выход счетчика общего числа синхроимпульсов подключен также к входу управления блока выбора допустимого числа неискаженных синхроимпульсов, выход которого подключен к первому входу определителя порога потери синхронизма, ко второму входу которого подключен выход счетчика циклов, а выход определителя порога потери синхронизма подключен ко второму входу третьего блока сравнения.

Благодаря введению блока выбора допустимого числа неискаженных синхроимпульсов и определителя порога потери синхронизма уменьшается время определения устройством для цикловой синхронизации состояния выхода из синхронизма, т.к. проверка по выходу устройства из состояния синхронизма осуществляется не через фиксированное число k циклов испытания, выбранное в зависимости от качества канала, а после каждого цикла испытания. При этом выход из состояния синхронизма будет определен, если число накопленных откликов на позиции истинного синхросигнала за очередной i-й цикл испытания будет меньше определенного порога потери синхронизма. Пороговое число потери синхронизма формируется в определителе порога потери синхронизма в зависимости от качества канала связи. При этом в определитель порога потери синхронизма из блока выбора допустимого числа неискаженных синхроимпульсов подается допустимое число неискаженных синхроимпульсов, которое выбирается в зависимости от измеренной вероятности ошибочного приема синхроимпульсов. При этом при истинном сбое циклового синхронизма в ячейках блока регистров сдвига, соответствующих позиции истинного синхросигнала, будет наблюдаться резкое уменьшение плотности накопления откликов опознавателя синхросигнала, что приведет к более быстрому определению выхода из синхронизма (потребуется меньшее число циклов испытания, чем k), что в свою очередь приведет к уменьшению времени восстановления синхронизма.

Проведенный заявителем анализ уровня техники, включающий поиск по патентным и научно-техническим источникам информации, и выявление источников, содержащих сведения об аналогах заявленного изобретения, позволили установить, что заявитель не обнаружил аналог, характеризующийся признаками, тождественными всем существенным признакам заявленного изобретения. Выбор из перечня выявленных аналогов прототипа, как наиболее близкого по совокупности существенных признаков аналога, позволило выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном устройстве, изложенных в формуле изобретения. Следовательно, заявленное изобретение соответствует критерию "новизна".

Для проверки соответствия заявленного изобретение критерию "изобретательский уровень" заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного устройства. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, определенного заявителем. Не выявлено влияние преобразований, предусматриваемых существенными признаками заявленного изобретения, на достижение технического результата. В частности, заявленным изобретением не предусматриваются следующие преобразования: дополнение известного средства какой-либо известной частью, присоединяемой к нему по известным правилам, для достижения технического результата, в отношении которого установлено влияние именно таких дополнений; замену какой-либо части известного средства другой известной частью для достижения технического результата, в отношении которого установлено влияние именно такой замены; исключение какой-либо части средства с одновременным исключением обусловленной ее наличием функции и достижением при этом обычного для такого исключения результата; увеличение однотипных элементов для усиления технического результата, обусловленного наличием в средстве именно таких элементов; выполнение известного средства или его части из известного материала для достижения технического результата, обусловленного известными свойствами материала; создание средства, состоящего из известных частей, выбор которых и связь между которыми осуществлены на основании известных правил, рекомендаций и достигаемый при этом технический результат обусловлен только известными свойствами частей этого объекта и связей между ними; изменение количественных признаков или взаимосвязи признаков, если известен факт влияния каждого из них на технический результат и новые значения признаков или их взаимосвязь могли быть получены из известных зависимостей. Следовательно, заявленное изобретение соответствует критерию "изобретательский уровень".

Изобретение поясняется чертежом, на котором представлена структурная схема устройства для цикловой синхронизации. Сведения, подтверждающие возможность осуществления изобретения с получением вышеуказанного технического результата, заключаются в следующем.

Устройство для цикловой синхронизации содержит опознаватель 1 синхросигнала, сумматор 2, блок 3 регистров сдвига, решающий узел 4, формирователь 5 цикловых импульсов, счетчик 6 циклов, блок 7 сравнения, определитель 8 порога потери синхронизма, блок 9 выбора допустимого числа неискаженных синхроимпульсов, счетчик 10 искаженных синхроимпульсов, счетчик 11 общего числа синхроимпульсов, триггер 12, счетчик 13 тактовых импульсов, элемент 14 И, блок 15 выбора порога, вход 16 сигнальный, вход 17 тактовый и выход 18 устройства. Опознаватель 1 синхросигнала содержит регистр 19 сдвига, обнаружитель 20 ошибок в синхрогруппе, формирователь 21 веса отклика на синхросигнал. Решающий узел 4 содержит блок 22 сравнения, блок 23 памяти, блок 24 вычитания, блок 25 сравнения, счетчик 26 сравнения, элемент 27 И, элемент 28 И, элемент 29 ИЛИ. При этом вход 16 сигнальный соединен с сигнальным входом опознавателя 1 синхросигнала. Сигнальным входом опознавателя 1 синхросигнала является информационный вход регистра 19 сдвига, выход которого подключен к входу обнаружителя 20 ошибок в синхрогруппе. Тактовый вход опознавателя 1 синхросигнала соединен с тактовыми входами регистра 19 сдвига и формирователя 21 веса отклика на синхросигнал. Первый выход обнаружителя 20 ошибок в синхрогруппе подключен к входу формирователя 21 веса отклика на синхросигнал. Второй выход обнаружителя 20 ошибок в синхрогруппе является дополнительным выходом опознавателя синхросигнала и подключен к входу данных счетчика 10 искаженных синхроимпульсов. Выход формирователя 21 веса отклика на синхросигнал является основным выходом опознавателя синхросигнала и соединен с первым входом сумматора 2, выход которого подключен совместно к сигнальному входу блока 3 регистров сдвига и первому входу блока 7 сравнения. Основной выход блока 3 регистров сдвига подключен ко второму входу сумматора 2, а дополнительный выход - к сигнальному входу решающего узла 4. При этом выход блока 22 сравнения подключен к входу управления блока 23 памяти, выход которого подключен ко второму входу блока 22 сравнения и первому входу блока 24 вычитания. Второй вход блока 24 вычитания объединен с входом данных блока 23 памяти, первым входом блока 22 сравнения и является сигнальным входом решающего узла 4. Выход блока вычитания 24 подключен ко второму входу блока 25 сравнения, выход которого соединен с входом сброса счетчика 26 сравнения. Выход счетчика 26 сравнения совместно подключен ко второму входу элемента 27 И, а также к первому входу элемента 28 И. Выход элемента 27 И, а также элемента 28 И подключены соответственно к первому и второму входам элемента 29 ИЛИ, выход которого подключен к входу сброса блока 23 памяти и является выходом решающего узла 4. При этом входом управления, тактовым входом, а также первым и вторым дополнительными входами управления решающего узла 4 являются соответственно первый вход блока 25 сравнения, тактовый вход счетчика 26 сравнения, первый вход элемента 27 И, второй вход элемента 28 И. Выход решающего узла 4 подключен к входам сброса блока 3 регистра сдвига, формирователя 5 цикловых импульсов, счетчика 6 циклов и блока 7 сравнения. Тактовый вход формирователя 5 цикловых импульсов объединен с первым входом элемента 14 И, тактовым входом опознавателя 1 синхросигнала, решающего узла 4, блока 3 регистров сдвига, счетчика 10 искаженных синхроимпульсов и счетчика 13 тактовых импульсов. Вход управления, первый и второй дополнительные входы управления решающего узла 4 соединены соответственно с выходом блока 15 выбора порога, выходом блока 7 сравнения и с выходом устройства. Выход счетчика 10 искаженных синхроимпульсов совместно соединен с адресными входами блока 15 выбора порога и блока 9 выбора допустимого числа неискаженных синхроимпульсов. Выход счетчика 11 общего числа синхроимпульсов совместно соединен с входом сброса счетчика 10 искаженных синхроимпульсов и входами управления блока 15 выбора порога и блока 9 выбора допустимого числа неискаженных синхроимпульсов. Выход формирователя 5 цикловых импульсов совместно подключен к входу управления счетчика 10 искаженных синхроимпульсов, входу управления триггера 12, к входу управления определителя 8 порога потери синхронизма, к счетному входу счетчика 6 циклов и входу управления блока 7 сравнения. Вход сброса триггера 12 соединен с выходом счетчика 13 тактовых импульсов. Выход триггера 12 совместно подключен к входу сброса счетчика 13 тактовых импульсов и второму входу элемента 14, выход которого соединен с тактовым входом счетчика 11 общего числа синхроимпульсов. Выход блока 9 выбора допустимого числа неискаженных синхроимпульсов соединен с первым входом определителя 8 порога потери синхронизма, второй вход которого соединен с выходом счетчика 6 циклов, а выход определителя 8 порога потери синхронизма соединен со вторым входом блока 7 сравнения. При этом сигнальный вход опознавателя 1, тактовый вход формирователя 5 цикловых импульсов и выход формирователя 5 цикловых импульсов является соответственно сигнальным входом 16, тактовым входом 17 и выходом 18 устройства.

Устройство для цикловой синхронизации работает следующим образом. На сигнальный вход опознавателя 1 синхросигнала поступает групповой цифровой сигнал, содержащий детерминированные группы синхросигнала, повторяющиеся с частотой следования циклов. На информационных позициях группового сигнала кодовые группы информационных символов, идентичные синхрогруппе, формируются случайно. В течение каждого тактового интервала в регистр 19 сдвига записывается один символ принимаемого сигнала, причем с приходом очередного символа предыдущий продвигается в следующую ячейку регистра сдвига. Таким образом, за m тактовых интервалов (где m - число символов в синхрогруппе) в регистр записывается m-символьная кодовая комбинация. При этом в течение каждого тактового интервала производится сравнение структуры каждой принимаемой последовательности из m символов с "копией" синхрогруппы, записанной в обнаружителе 20 ошибок в синхрогруппе, а результат сравнения в обнаружителе 20 преобразуется в s-разрядное (где s=[log2m]+1, здесь [ ] - целая часть числа) двоичное число безошибочно обнаруженных синхросимволов в синхрогруппе mнеиск и двоичное число обнаруженных ошибок в синхрогруппе mош. При этом число mнеиск формируется на первом выходе обнаружителя 20 ошибок в синхрогруппе и поступает на вход данных формирователя 21 веса отклика на синхросигнал. Число mош формируется на втором выходе обнаружителя 20 ошибок в синхрогруппе и поступает на дополнительный выход опознавателя 1 синхросигнала. Обнаружитель 20 ошибок в синхрогруппе может быть реализован, как описано в патенте РФ №2284665, кл. Н04L 7/08, опубл. 27.09.2006, Бюл. №27, фиг.2.

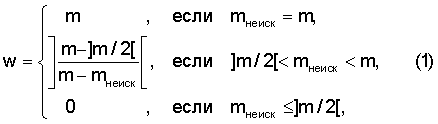

В формирователе 21 веса отклика на синхросигнал в зависимости от величины безошибочно обнаруженных синхросимволов в синхрогруппе mнеиск формируется отклик w (в виде двоичного числа). Формирователь 21 веса отклика на синхросигнал может быть выполнен в виде регистра с параллельным входом, а параллельный выход регистра подключен к адресному входу запоминающего устройства (например, реализованного с помощью постоянного запоминающего устройства на микросхеме К573РФ13), в элементы памяти которого записаны значения весовых коэффициентов, рассчитанные в зависимости от величины неискаженных синхросимволов mнеиск по следующему правилу:

где m - длина синхрогруппы; mнеиск - количество неискаженных синхросимволов; ]•[ - целая часть числа. Выборка веса w отклика на синхросигнал с запоминающего устройства осуществляется при поступлении на тактовый вход формирователя 21 веса отклика на синхросигнал (являющегося входом управления считыванием  запоминающего устройства) переднего фронта сигнала тактовой синхронизации.

запоминающего устройства) переднего фронта сигнала тактовой синхронизации.

Отклик w с основного выхода формирователя 21 веса отклика на синхросигнал поступает на первый вход сумматора 2. Сумматор 2 представляет собой параллельный комбинационный сумматор, у которого s-разрядный вход первого слагаемого (младшие разряды n-разрядного входа) и n-разрядных входов второго слагаемого являются соответственно первым и вторым входом сумматора, при этом другие (n-s) разрядные входы первого слагаемого подключены к источнику "нулевого" уровня.

Блок 3 регистров сдвига включает в себя n N-разрядных (n=[log2N·m]+1, N - число позиций в одном цикле) регистров сдвига. При этом объединенные тактовые входы и объединенные входы сброса регистров сдвига являются соответственно тактовым входом и входом сброса блока 3 регистров сдвига, а сигнальные входы, выходы последних разрядов и выходы первых разрядов всех регистров сдвига являются соответственно сигнальным входом, основным выходом и дополнительным выходом бока 3 регистров сдвига. Таким образом, отклик опознавателя 1 синхросигнала, имеющий место в i-м тактовом интервале, складывается в сумматоре 2 с результатом предыдущего счета откликов на i-й позиции цикла, поступающим с основного выхода блока 3 регистров сдвига. Новый результат счета откликов, больший на w прежнего, записывается в виде n-разрядного двоичного числа в соответствующие первые ячейки (разряды) регистров сдвига блока 3 регистров сдвига. При этом двоичное число, записанное до этого в первые ячейки блока 3 регистров сдвига, а также все остальные числа, хранящиеся в последующих однотипных ячейках, параллельно сдвигаются на один разряд, и с выхода блока 3 регистров сдвига на второй вход сумматора 2 поступает результат счета откликов - на (i+1)-м тактовом интервале. Если отклик опознавателя синхросигнала на (i+1)-м тактовом интервале отсутствует, то прежний результат счета откликов на (i+1)-й позиции цикла переписывается в первые ячейки блока 3 регистров сдвига, а остальные числа, хранящиеся в однотипных ячейках блока 3 регистров сдвига, сдвигаются на один разряд и т.д. Блок 3 регистров сдвига обеспечивает запоминание результатов счета откликов на каждой позиции цикла в течение длительности цикла. При этом величина n определяет емкость памяти результатов счета. Одновременно результаты счета откликов на каждой из позиций цикла с дополнительного выхода блока 3 регистров сдвига последовательно поступают на сигнальный вход решающего узла 4. В решающем узле 4, например в i-м тактовом интервале, входное двоичное число в параллельном коде, представляющее текущий результат счета откликов на i-й позиции цикла, одновременно подается на первый вход блока 22 сравнения, вход данных блока 23 памяти и второй вход блока 24 вычитания. В блоке 22 сравнения входное число сравнивается с двоичным числом, хранящимся в блоке 23 памяти и, если оно превышает число блока 23 памяти, то на выходе блока 22 сравнения формируется импульс, который, поступая на вход управления блока 23 памяти, обеспечивает стирание прежнего и запись нового (входного) числа. После этого на входах блока 22 сравнения оказываются равные двоичные числа. Если же входное число равно или меньше числа, хранящегося в блоке 23 памяти, то содержимое последнего не изменяется. Таким образом, в блок 23 памяти переписывается наибольший текущий результат счета откликов на какой либо позиции цикла, который далее сравнивается с результатами счета на последующих позициях цикла. Получающаяся разность (между числом блока 23 памяти и входным числом) на выходе блока 24 вычитания в виде двоичного числа в параллельном коде сравнивается в блоке 25 сравнения с пороговым числом d, поступающим на первый его вход (являющийся входом управления решающего узла 4) с выхода блока 15 выбора порога. При этом, если число с выхода блока 24 вычитания меньше порогового числа d, то с выхода второго блока 25 сравнения на вход сброса счетчика 26 сравнения подается "единичный" (запрещающий) потенциал, который устанавливает и удерживает его в "нулевом" состоянии. Когда в i-м тактовом интервале число с выхода блока 24 вычитания равно или больше числа d, с выхода второго блока 25 сравнения поступает "нулевой" (разрешающий) потенциал, и счетчик 26 сравнения производит счет одного тактового импульса, поступающего на его тактовый вход, являющийся тактовым входом решающего узла 4. Если наибольшее двоичное число, записанное в блок 23 памяти, будет превышать каждое из N-1 последующих чисел, поступающих друг за другом с дополнительного выхода блока 3 регистров сдвига, на величину, равную или большую порогового числа d, то счетчик 26 сравнения произведет счет следующих подряд N тактовых импульсов. После чего на его выходе формируется "единичный" импульсный сигнал, который поступает на второй вход элемента 27 И, а также на первый вход элемента 28 И. Прохождение "единичного" импульсного сигнала с выхода счетчика 26 сравнения на выход элемента 27 И осуществляется при поступлении "единичного" импульсного сигнала на первый вход элемента 27 И с выхода блока 7 сравнения. Прохождение "единичного" импульсного сигнала с выхода счетчика 26 сравнения на выход элемента 28 И осуществляется при поступлении сигнала цикловой синхронизации с выхода формирователя 5 цикловых импульсов на второй вход элемента 28 И. Элемент 29 ИЛИ обеспечивает прохождение "единичного" импульсного сигнала на выход решающего узла 4 или с выхода элемента 27 И, или с выхода элемента 28 И. Сигнал на выходе решающего узла 4 является сигналом синхронизации (фазирования) устройства. При этом в первом случае сигнал синхронизации на выходе решающего узла 4 формируется при потере состояния синхронизма. Во втором случае выходной сигнал синхронизации формируется в синхронном режиме работы.

Сигнал синхронизации с выхода решающего узла 4 поступает на входы сброса блока 23 памяти, блока 3 регистров сдвига и формирователя 5 цикловых импульсов, счетчика 6 циклов и блока 7 сравнения. В результате блок 23 памяти и блок 3 регистров сдвига, счетчик 6 циклов и триггер блока 7 сбрасываются в "нуль". После чего с выхода блока 25 сравнения начинает поступать запрещающий "единичный" потенциал и счетчик 26 сравнения также сбрасывается в "нуль". Выходным сигналом синхронизации решающего узла 4 производится фазирование формирователя 5 цикловых импульсов таким образом, что на выход 18 устройства начинают поступать регулярно следующие цикловые импульсы, по времени совпадающие с откликами опознавателя 1 синхросигнала на истинные синхрогруппы. Далее процесс поиска временного положения циклового синхросигнала в двоичном потоке группового сигнала начинается заново. При этом следующий сигнал синхронизации решающего узла 4 будет сформирован при условии обнаружения синхросигнала после потери состояния синхронизма ("единичный" импульс на выходе элемента 27 И) или в синхронном состоянии ("единичный" импульс на выходе элемента 28 И). В первом случае сигнал синхронизации решающего узла 4 изменит фазу начальной установки формирователя 5 цикловых импульсов. Во втором случае фаза начальной установки формирователя 5 цикловых импульсов не изменится. Блоки 22 и 25 сравнения могут быть выполнены, например, в виде n-разрядного компаратора двоичных кодов, формирующего признак "больше", "меньше" при соответствующем знаке разницы значений входных операндов, а также признак их равенства, подаваемых на первый вход Р и второй вход Q блоков. При этом выходами первого и второго блока сравнения являются выход P>Q компаратора. Блок 23 памяти может быть выполнен в виде n-разрядного регистра с параллельным входом. При этом входом данных, входом управления, входом сброса и выходом блока 23 памяти является соответственно вход данных, тактовый вход, вход сброса и выход данных n-разрядного регистра. Блок 24 вычитания может быть выполнен в виде полного n-разрядного параллельного сумматора. Разрядность сумматора обеспечивается последовательным соединением выхода переноса сумматора младших разрядов с входом переноса сумматора старших разрядов. Для выполнения сумматором операции вычитания число с блока 23 памяти, поступающее на первый вход блока вычитания, подвергается инверсии, а число, поступающее с дополнительного выхода блока 3 регистров сдвига на второй вход блока вычитания, инверсии не подвергается (например, может быть реализован, как описано в патенте РФ №2284665, кл. Н04L 7/08, опубл. 27.09.2006, Бюл. №27, фиг.2, элементы DD6, DD1.3-DD1). Счетчик 26 сравнения и формирователь 5 цикловых импульсов могут быть выполнены в виде последовательно соединенных двоично-десятичного синхронного счетчика и дешифратора. При этом входы сброса счетчика 26 сравнения и формирователя 5 цикловых импульсов являются входами сброса двоично-десятичного счетчика. Соответственно тактовые входы счетчика 26 сравнения и формирователя 5 цикловых импульсов являются тактовыми входами двоично-десятичного счетчика. Выходами счетчика 26 сравнения и формирователя 5 цикловых импульсов является выход дешифратора, определяющий состояние двоично-десятичных счетчиков. При этом фазирование формирователя 5 цикловых импульсов может осуществляться путем установки в "нуль" счетчика.

Сбой состояния синхронизма устройством для цикловой синхронизации определяется с помощью счетчика 6 циклов, блока 7 сравнения, определителя 8 порога потери синхронизма и блока 9 выбора допустимого числа неискаженных синхроимпульсов. Сбой состояния синхронизма будет определен с помощью блока 7 сравнения, если число накопленных откликов в сумматоре 2 на позиции истинного синхросигнала за очередной цикл наблюдения L будет меньше порогового числа q (порога потери синхронизма), сформированного в определителе 8 порога потери синхронизма. Пороговое число q формируется в зависимости от качества канала связи. При этом на первый вход определителя 8 порога потери синхронизма с выхода блока 9 выбора допустимого числа неискаженных синхроимпульсов подается выбранное допустимое число неискаженных синхроимпульсов mдоп неиск. На второй вход определителя 8 порога потери синхронизма с выхода счетчика 6 циклов подается двоичное число текущего цикла поиска синхросигнала L. С выхода определителя 8 порога потери синхронизма пороговое число q подается на второй вход блока сравнения, а на его первый вход с выхода сумматора 2 подается число накопленных откликов на позиции истинного синхросигнала.

Счетчик 6 циклов представляет собой двоично-десятичный синхронный счетчик импульсов, на счетный вход которого с выхода формирователя 5 цикловых импульсов подаются импульсы цикловой синхронизации, а на вход сброса счетчика 6 с выхода решающего узла 4 подается сигнал синхронизации.

Блок 7 сравнения состоит из сравнивающего устройства и запоминающего устройства. В сравнивающем устройстве производится операция сравнения числа Р, поступающего на первый вход блока 7 сравнения с числом Q, поступающим на второй вход блока 7. Результат сравнения с выхода сравнивающего устройства кратковременно запоминается в запоминающем устройстве при поступлении сигнала управления на вход управления блока 7 сравнения. При P<Q в запоминающее устройство записывается сигнал логической "единицы". При P≥Q в запоминающее устройство записывается сигнал логического "нуля". В первом случае (P<Q) в блоке 7 сравнения определяется срыв состояния синхронизма устройства для цикловой синхронизации, а во втором (P≥Q) срыв состояния синхронизма отсутствует. Сброс запоминающего устройства в нулевое состояние осуществляется при поступлении на вход сброса блока 7 сравнения сигнала синхронизации с выхода решающего узла 4. Блок 7 сравнения может быть реализован, как описано в патенте РФ №2284665, кл. Н04L 7/08, опубл. 27.09.2006, Бюл. №27, фиг.4, при этом у сравнивающего устройства используется только один выход P<Q.

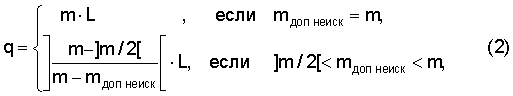

Определитель 8 порога потери синхронизма представляет собой запоминающее устройство. При этом на первый вход определителя 8 порога потери синхронизма подается допустимое число неискаженных синхроимпульсов mдоп неиск, которое подается на младшие разряды адресного входа запоминающего устройства, а к старшим разрядам (являющиеся вторым входом определителя 8 порога потери синхронизма) адресного входа подается двоичное число текущего цикла поиска L. К входу управления считыванием  запоминающего устройства подается сигнал цикловой синхронизации. В элементы памяти запоминающего устройства записаны значения порога потери синхронизма q, рассчитанные в зависимости от величины допустимого числа неискаженных синхросимволов mдоп неиск и числа текущего цикла поиска синхросигнала L по следующему правилу:

запоминающего устройства подается сигнал цикловой синхронизации. В элементы памяти запоминающего устройства записаны значения порога потери синхронизма q, рассчитанные в зависимости от величины допустимого числа неискаженных синхросимволов mдоп неиск и числа текущего цикла поиска синхросигнала L по следующему правилу:

где ]•[ - целая часть числа.

Выборка значения порога потери синхронизма q с запоминающего устройства осуществляется при поступлении на вход управления считыванием  запоминающего устройства сигнала цикловой синхронизации. Запоминающее устройство, например, может быть реализованного с помощью постоянного запоминающего устройства на микросхеме К573РФ13.

запоминающего устройства сигнала цикловой синхронизации. Запоминающее устройство, например, может быть реализованного с помощью постоянного запоминающего устройства на микросхеме К573РФ13.

Процесс формирования пороговых чисел d для решающего узла 4 и допустимого числа неискаженных синхроимпульсов mдоп неиск в синхрогруппе для определителя 8 порога потери синхронизма производится следующим образом. На s-разрядный вход данных счетчика 10 искаженных синхроимпульсов поступает двоичное число mош, равное числу ошибок в синхрогруппе. Счетчик 10 искаженных синхроимпульсов вычисляет суммарное число ошибок в синхрогруппах, а счетчик 11 общее число синхроимпульсов, переданных за определенный промежуток времени Y. Сигнал цикловой синхронизации с выхода формирователя 5 цикловых импульсов устанавливает триггер 12 в "единичное" состояние, а "единичный" сигнал (сигнал разрешения) с выхода триггера 12 поступает на входы сброса счетчика 13 тактовых импульсов и второй вход элемента 14 И. При этом счетчик 13 тактовых импульсов переводится в режим "счета" и разрешается прохождение тактовых импульсов с выхода элемента 14 И на тактовый вход счетчика 11 общего числа синхроимпульсов. Счетчик 13 обеспечивает прохождение через элемент 14 И за один цикл определенного количества тактовых импульсов, равного количеству импульсов в синхрогруппе m, после чего осуществляет сброс триггера 12 в "нуль". Счетчик 13 тактовых импульсов сигналом логического "нуля" с выхода триггера 12 сбрасывается в "нуль" и переводится в режим "остановка". Подсчитывая число Х искаженных синхроимпульсов в течение времени счета довольно большого числа цикловых синхроимпульсов Y, можно периодически определять вероятность (частость) ошибочного приема синхроимпульсов по формуле Pош=X/Y, т.е. производить текущую оценку степени искажения принимаемого цифрового сигнала. Счетчики 11 и 13 могут быть выполнены также как и формирователь 5 цикловых импульсов в виде последовательно соединенных двоично-десятичного синхронного счетчика и дешифратора. Обнуление обоих счетчиков - синхронное. При этом дешифратор счетчика 13 тактовых импульсов настроен на опознание состояния двоично-десятичного счетчика, равного количеству импульсов в синхрогруппе m, a дешифратор счетчика 11 общего числа синхроимпульсов настроен на опознание состояния двоично-десятичного счетчика, равного количеству импульсов наблюдения Y. Триггер 12 может быть выполнен в виде RS-триггера. При этом вход S подсоединен к выходу формирователя 5 цикловых импульсов, а вход R - к выходу счетчика 13 тактовых импульсов. Емкость счетчика 11 общего числа синхроимпульсов выбирается равной величине Y, поэтому после отсчета каждых Y синхроимпульсов на его выходе формируется единичный импульс, с помощью которого в блок 15 выбора порога и в блок 9 выбора допустимого числа ошибок в синхрогруппе, вместо хранившегося в них двоичного числа, переписывается содержимое счетчика 10 искаженных синхроимпульсов. После чего счетчик 10 искаженных синхроимпульсов сбрасывается в "нуль" и процесс анализа качества принимаемого сигнала в течение следования последующих Y синхроимпульсов повторяется.

Счетчик 10 искаженных синхроимпульсов состоит из суммирующего устройства и запоминающего устройства. При этом на вход данных счетчика 10 искаженных синхроимпульсов, являющегося входом суммирующего устройства, подается число ошибочно принятых синхроимпульсов mош со второго выхода обнаружителя 20 ошибок в синхрогруппах. Это число суммируется с числом ошибок в синхрогруппах, накопленных за предыдущий период наблюдения. На вход управления счетчика 10 искаженных синхроимпульсов с выхода формирователя 5 цикловых импульсов поступают цикловые импульсы. Это обеспечивает подсчет счетчиком 10 только искаженных синхроимпульсов X, принадлежащих истинным синхрогруппам. Счетчик 10 искаженных синхроимпульсов может быть реализован, например, как описано в описании изобретения к патенту РФ №2239953, кл. Н04L 7/08, опубл. 26.11.2004, Бюл. №31, фиг.4.

Блок 15 выбора порога и блок 9 выбора допустимого числа неискаженных синхроимпульсов в синхрогруппе в зависимости от значения записанных в них двоичного числа Х производят выбор соответственно определенного порогового числа d и допустимого числа неискаженных синхроимпульсов mдоп неиск. Выбранные числа d и mдопнеиск с выходов блоков 15 и 9 в параллельном коде подаются соответственно на вход управления решающего узла 4 и первый вход определителя 8 порога потери синхронизма. Блок 15 выбора порога и блок 9 выбора допустимого числа неискаженных синхроимпульсов могут быть выполнены в виде постоянных запоминающих устройств, в элементы памяти которых записаны результаты расчетов пороговых чисел d и допустимого числа неискаженных синхроимпульсов mдоп неиск в зависимости от вероятности ошибочного приема синхроимпульсов (см. Кальников В.В., Ташлинский А.Г. Методики нахождения внутренних параметров систем цикловой синхронизации с параллельным и рециркулярным поиском. - Ульяновск: УФВУС, 2002, 35 с. - Деп. в ЦВНИ МО РФ 23.09.02. №Б4898, опубл. СРДР, сер. Б, вып.61, 2002). При этом величина измеренной вероятности ошибочного приема синхроимпульсов Рош с выхода счетчика 10 искаженных синхроимпульсов подается на адресные входы запоминающих устройств блоков 15 и 9. Вывод чисел d и mдоп неиск с блоков 15 и 9 осуществляется при поступлении на входы управления считывания  запоминающих устройств сигнала окончания измерения вероятности ошибочного приема синхроимпульсов Рош с выхода счетчика 11 общего числа синхроимпульсов. Таким образом, в течение времени счета Y в решающий узел 4 подается пороговое число d, а в определитель 8 порога потери синхронизма - допустимое число неискаженных синхроимпульсов mдоп неиск в синхрогруппе, которые могут принимать в каждом конкретном случае одно из h дискретных значений (градаций) в зависимости от качества принимаемого сигнала. Необходимое число градаций h порогового числа d, а также допустимого числа неискаженных синхроимпульсов mдоп неиск в синхрогруппе выбирается из расчета поддержания вероятности обнаружения ложного синхросигнала в требуемых пределах при различных изменениях величины Рош. При этом законы формирования конкретных значений порогового числа dr блоком 15 выбора порога, допустимого числа неискаженных синхроимпульсов mдоп неиск r блоком 9 выбора допустимого числа ошибок в синхрогруппе можно записать в виде:

запоминающих устройств сигнала окончания измерения вероятности ошибочного приема синхроимпульсов Рош с выхода счетчика 11 общего числа синхроимпульсов. Таким образом, в течение времени счета Y в решающий узел 4 подается пороговое число d, а в определитель 8 порога потери синхронизма - допустимое число неискаженных синхроимпульсов mдоп неиск в синхрогруппе, которые могут принимать в каждом конкретном случае одно из h дискретных значений (градаций) в зависимости от качества принимаемого сигнала. Необходимое число градаций h порогового числа d, а также допустимого числа неискаженных синхроимпульсов mдоп неиск в синхрогруппе выбирается из расчета поддержания вероятности обнаружения ложного синхросигнала в требуемых пределах при различных изменениях величины Рош. При этом законы формирования конкретных значений порогового числа dr блоком 15 выбора порога, допустимого числа неискаженных синхроимпульсов mдоп неиск r блоком 9 выбора допустимого числа ошибок в синхрогруппе можно записать в виде:

dr=F1(Ar≤Pош<Br),

mдоп неиск r=F2(Ar≤Pош<Br),

где F1, F2 - заранее выбранные правила соответственно для блока 15 выбора порога и блока 9 выбора допустимого числа неискаженных синхроимпульсов, по которым величина Pош=X/Y, принимающей значение в пределах r-го интервала (r может изменяться от 1 до h) измерений, приводится в соответствие вполне определенному значению порогового числа dr, а также допустимого числа неискаженных синхроимпульсов mош неиск r; Аr и Br - соответственно нижняя и верхняя границы величины Рош для r-го интервала.

Благодаря введению блока выбора допустимого числа неискаженных синхроимпульсов и определителя порога потери синхронизма уменьшается время определения устройством для цикловой синхронизации состояния выхода из синхронизма, т.к. проверка по выходу устройства из состояния синхронизма осуществляется не через фиксированное число k циклов испытания, выбранное в зависимости от качества канала, а после каждого цикла испытания. При этом выход из состояния синхронизма будет определен, если число накопленных откликов на позиции истинного синхросигнала за очередной i-й цикл испытания будет не менее определенного порога потери синхронизма. При этом при истинном сбое циклового синхронизма в блоке регистров сдвига в ячейках, соответствующих позиции истинного синхросигнала, будет наблюдаться резкое уменьшение плотности накопления откликов опознавателя синхросигнала, что приведет к более быстрому определению выхода из синхронизма (потребуется меньшее число циклов испытания, чем k), что в свою очередь приведет к уменьшению времени восстановления синхронизма. Пороговое число потери синхронизма формируется в определителе порога потери синхронизма в зависимости от качества канала связи. При этом в определитель порога потери синхронизма из блока выбора допустимого числа неискаженных синхроимпульсов подается допустимое число неискаженных синхроимпульсов, которое выбирается в зависимости от измеренной вероятности ошибочного приема синхроимпульсов.

Требуемое быстродействие устройства для синхронизации по циклам (при высокой вероятности ошибочного приема синхроимпульсов), которое определяется временем восстановления циклового синхронизма, достигается тем, что восстановление синхронизма после его сбоя и фазирование устройства под новую позицию циклового синхросигнала осуществляется при возникновении одновременно двух событий: определения решающим узлом 4 новой позиции циклового синхросигнала и обнаружения сбоя (потери) циклового синхронизма с помощью определителя 8 порога потери синхронизма и блока 9 выбора допустимого числа неискаженных синхроимпульсов, а также счетчика 6 циклов и блока 7 сравнения. При этом проверка по выходу из состояния синхронизма в блоке 7 сравнения осуществляется после каждого цикла испытания и определяется, если число накопленных откликов на позиции истинного синхросигнала за очередной i-й цикл испытания будет меньше порога потери синхронизма, установленного с помощью определителя 8 порога потери синхронизма. Тем самым при высокой вероятности ошибочного приема синхроимпульсов достигается минимальное время восстановления синхронизма, при котором еще обеспечивается требуемая помехоустойчивость. При этом требуемая помехоустойчивость устройства обеспечивается выбором закона формирования весового коэффициента w для формирователя 21 веса отклика на синхросигнал, пороговых чисел dr и qr, для блока 15 выбора порога и определителя 8 порога, а также допустимого числа неискаженных синхроимпульсов mош неиск r для блока 9 выбора допустимого числа неискаженных синхроимпульсов по соответствующим измеренным значениям величины Рош, попадающим в пределы какого-либо r-го интервала с границами Аr и Вr, по принципу: чем больше величина Рош, тем большим должно быть пороговое число dr и допустимое число неискаженных синхроимпульсов mош неиск r. Значения весового коэффициента w и порогового числа qr определяются по правилам, определяемым формулами (1) и (2). Величина Y, определяющая коэффициент счета счетчика 9 общего числа синхроимпульсов, должна выбираться, с одной стороны, достаточно большой для того, чтобы обеспечить требуемую точность оценки вероятности ошибки Рош одиночного символа, с другой стороны - достаточно малой, чтобы обеспечить измерение величины Рош в пределах между двумя сбоями синхронизма по циклам и слежение за изменениями условий связи. Если считать, что сбои синхронизма по циклам происходят относительно редко, т.е. через интервалы времен, намного превышающие время счета Y цикловых синхроимпульсов, то на практике величина Y может выбираться как:

где B1 - верхняя граница величины Рош в пределах первого интервала измерений, который соответствует наименьшему пороговому числу d1; [ ] - означает округление до цело числа.

Вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного устройства следующей совокупности условий:

- средство, воплощающее заявленное устройство при его осуществлении, предназначено для использования в приемных устройствах синхронизации по циклам систем передачи дискретных сообщений;

- для заявленного устройства в том виде, как оно охарактеризовано в формуле изобретения, подтверждена возможность его осуществления с помощью описанных в заявке или известных до даты приоритета средств и методов;

- средство, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата.

Таким образом, заявленное изобретение соответствует критерию "промышленная применимость".

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Устройство для синхронизации по циклам | 1983 |

|

SU1172052A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

Изобретение относится к электросвязи и может быть использовано в приемных устройствах синхронизации по циклам систем передачи дискретных сообщений. Технический результат - повышение быстродействия устройства для цикловой синхронизации при высокой вероятности ошибочного приема синхроимпульсов. Устройство содержит опознаватель синхросигнала, сумматор, блок регистров сдвига, решающий узел, формирователь цикловых импульсов, счетчик циклов, блок сравнения, определитель порога потери синхронизма, блок выбора допустимого числа неискаженных синхроимпульсов, счетчик искаженных синхроимпульсов, счетчик общего числа синхроимпульсов, триггер, счетчик тактовых импульсов, элемент И, блок выбора порога, вход сигнальный, вход тактовый и выход устройства. Опознаватель синхросигнала содержит регистр сдвига, обнаружитель ошибок в синхрогруппе, формирователь веса отклика на синхросигнал. Решающий узел содержит первый блок сравнения, блок памяти, блок вычитания, второй блок сравнения, счетчик сравнения, второй элемент И, третий элемент И, элемент ИЛИ. Технический результат достигается введением блока выбора допустимого числа неискаженных синхроимпульсов и определителя порога потери синхронизма, при этом уменьшается время определения состояния выхода из синхронизма, т.к. проверка по выходу устройства из состояния синхронизма осуществляется не через фиксированное число циклов испытания, выбранное в зависимости от качества канала, а после каждого цикла испытания. При этом выход из состояния синхронизма определяется, когда число накопленных откликов на позиции истинного синхросигнала за очередной цикл испытания будет меньше порога потери синхронизма. При этом при истинном сбое синхронизма в ячейках, соответствующих позиции истинного синхросигнала, наблюдается резкое уменьшение плотности накопления откликов опознавателя синхросигнала, что позволяет быстрее определять состояние выхода системы из синхронизма, что в свою очередь позволяет сокращать время восстановления синхронизма. 1 ил.

Устройство для цикловой синхронизации, содержащее опознаватель синхросигнала, состоящий из регистра сдвига, обнаружителя ошибок в синхрогруппе и формирователя веса отклика на синхросигнал, при этом сигнальный вход опознавателя синхросигнала подключен к информационному входу регистра сдвига, выход которого подключен к входу обнаружителя ошибок в синхрогруппе, второй выход которого подключен к дополнительному выходу опознавателя, а первый выход обнаружителя ошибок в синхрогруппе подключен к входу данных формирователя веса отклика на синхросигнал, тактовый вход которого соединен с тактовым входом регистра сдвига и является тактовым входом опознавателя синхросигнала, а выход формирователя веса отклика на синхросигнал является основным выходом опознавателя синхросигнала, который соединен с первым входом сумматора, выход которого подключен совместно к первому входу третьего блока сравнения и сигнальному входу блока регистров сдвига, основной выход которого соединен со вторым входом сумматора, а дополнительный выход блока регистров сдвига подключен к сигнальному входу решающего узла, при этом выход решающего узла подключен к входам сброса формирователя цикловых импульсов, счетчика циклов, третьего блока сравнения и блока регистров сдвига, тактовый вход которого объединен с тактовыми входами опознавателя синхросигнала, решающего узла, счетчика искаженных синхроимпульсов, первого элемента И, счетчика тактовых импульсов и формирователя цикловых импульсов, а вход управления решающего узла соединен с выходом блока выбора порога, при этом вход данных счетчика искаженных синхроимпульсов подключен к дополнительному выходу опознавателя синхросигнала, а выход счетчика искаженных синхроимпульсов соединен с адресным входом блока выбора порога, а также счетчик общего числа синхроимпульсов, выход которого совместно соединен с входом сброса счетчика искаженных синхроимпульсов, а также с входом управления блока выбора порога, причем выход формирователя цикловых импульсов совместно подключен к входу управления счетчика искаженных синхроимпульсов, счетному входу счетчика циклов, входу управления третьего блока сравнения, входу установки триггера и второму входу управления решающего узла, к первому входу управления которого подключен выход третьего блока сравнения, причем выход счетчика тактовых импульсов подключен к входу сброса триггера, а выход триггера подключен совместно к входу сброса счетчика тактовых импульсов и второму входу первого элемента И, выход которого соединен с тактовым входом счетчика общего числа синхроимпульсов, причем сигнальный вход опознавателя синхросигнала, тактовых вход и выход формирователя цикловых импульсов являются соответственно сигнальным входом, тактовым входом и выходом устройства, отличающееся тем, что в него введены блок выбора допустимого числа неискаженных синхроимпульсов и определитель порога потери синхронизма, при этом выход счетчика искаженных синхроимпульсов подключен также к адресному входу блока выбора допустимого числа неискаженных синхроимпульсов, выход формирователя цикловых импульсов подключен также к входу управления определителя порога потери синхронизма, а выход счетчика общего числа синхроимпульсов подключен также к входу управления блока выбора допустимого числа неискаженных синхроимпульсов, выход которого подключен к первому входу определителя порога потери синхронизма, ко второму входу которого подключен выход счетчика циклов, а выход определителя порога потери синхронизма подключен ко второму входу третьего блока сравнения.

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Способ цикловой синхронизации и система для его осуществления | 1987 |

|

SU1711342A1 |

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2298879C1 |

| US 5778010, A, 07.07.1998 | |||

| Устройство для крепления ножа землеройной машины | 1977 |

|

SU735717A1 |

Авторы

Даты

2009-02-27—Публикация

2007-05-28—Подача