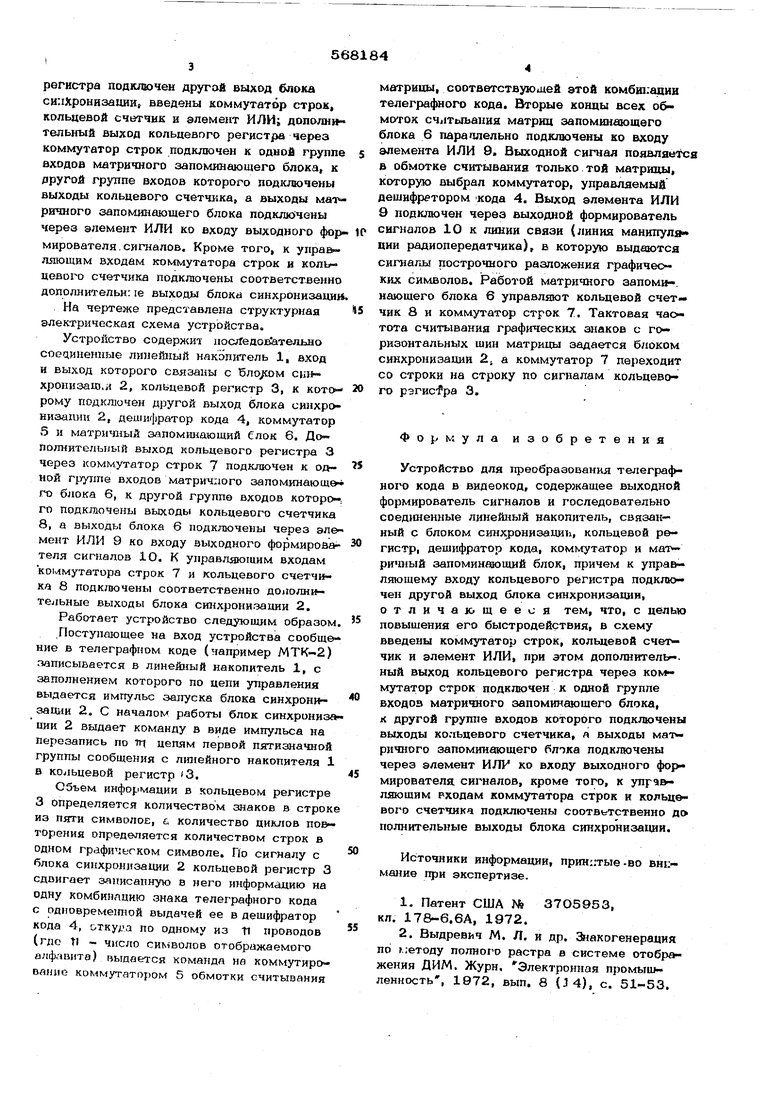

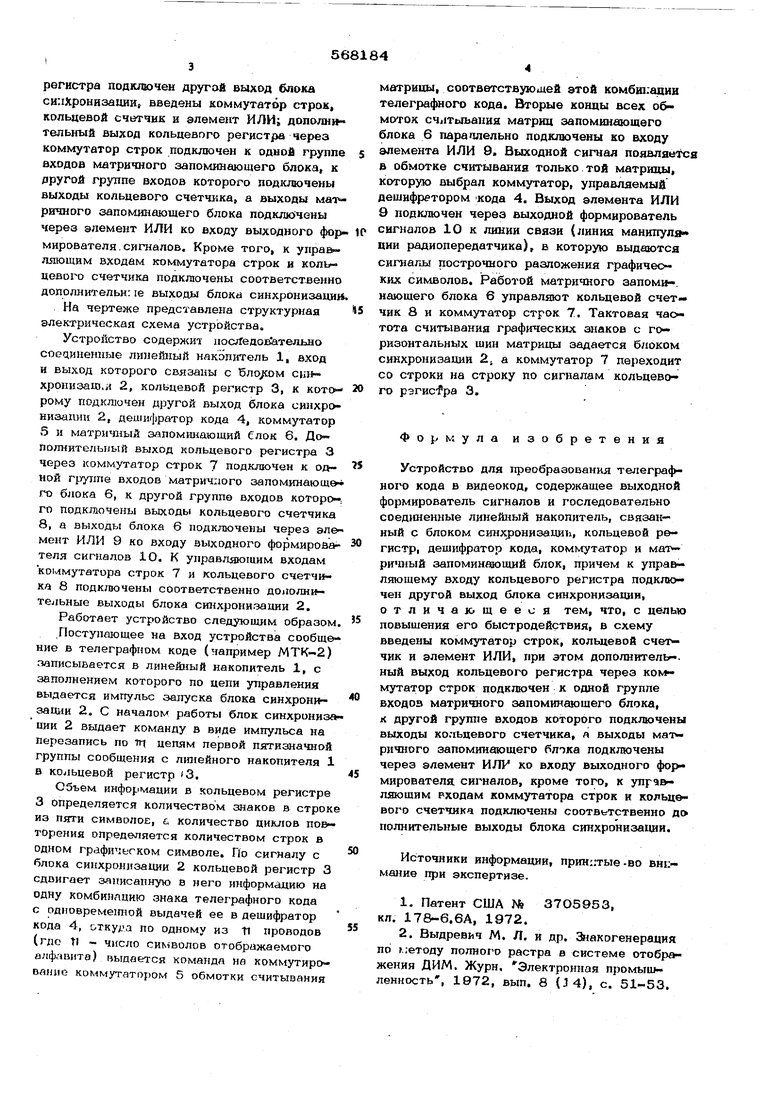

регистра подключен другой выход блока синхронизации, введены коммутатор строк, кольцевой счетчик и элемент ИЛИ; дополн тельный выход кольцевого регистра через коммутатор строк подключен к одной группе входов матричного запоминающего блока, к другой группе входов которого подключены выходы кольцевого счетчика, а выходы мат рвгчного запоминающего блока подкгаьчены через элемент ИЛИ ко входу выходного формирователя. сигналов. Кроме того, к управляющим входам коммутатора строк и кольцевого счетчика подключены соответственно допрлнительн: le выходы блока синхронизации На чертеже представлена структурная электрическая схема устройства. Устройство содержит посЛедо1гательно соединенные лилейный накопитель 1, вход и выход которого связаны с бло/ом сш хронизащ.и 2, кольцевой регистр 3, к которому подключен другой выход блока синхрси низанин 2, дешифратор кода 4, коммутатор 5 и матричный запом1шающий блок 6. Дополнительный выход кольцевого регистра 3 через коммутатор строк 7 подключен к одной группе входав матричного запоминающе го блока 6, к другой группе входов которого подключены выходы кольцевого счетчика 8, а выходы блока 6 подключены через эле мент ИЛИ 9 ко входу выходного формирователя сигналов 10. К управляющим входам коммутатора строк 7 и кольцевого счетчика 8 подключены соответственно цолопнательные выходы блока синхронизации 2. Работает устройство следующим образом Поступающее на вход устройства сообщение в телеграфном коде (например МТК-2) ааписывается в линейный накопитель 1, с заполнением которого по цепи управления выдается импульс запуска блока синхронизации 2. С началом работы блок синхрониз пии 2 выдает команду в виде импульса на перезапись по щ цепям первой пятизначной группы сообщения с линейного накопителя 1 в кольцевой регистр 3. Объем информации в кольцевом регистре 3 определяется количеством знаков в строке из пяти символов, с количество циклов пов торения определяется количеством строк в одном графическом символе. По сигналу с блока синхронизации 2 кольцевой регистр 3 сдвигает записапную в него информацию на одну комбинацию знака телеграфного кода с рдновреметюй выдачей ее в дешифратор кода 4, откула по одному из Т1 проводов (где Т1 - число символов отображаемого алфавита) выдается команда на коммутирование коммутатором 5 обмотки считывания атрицы, соответствующей этой ком6ш:адии елеграфного кода. Вторые концы всех о&оток считывания матриц запоминающего лока 6 парагшельно подключены ко входу лемента ИЛИ 9. Выходной сигнал появляется обмотке считывания только той матрицы, оторую выбрал коммутатор, управляемый ешифратором Кода 4. Выход элемента ИЛИ подключен через выходной формирователь игналов 10 к линии связи (линия манипул ии радиопередатчика), в которую выдаются ипшлы построчного разложения графических символов. Работой матричного аапом -. аюшего блока 6 управляют кольцевой счет- ик 8 и коммутатор строк 7. Тактовая чаоота считывания графических знаков с горизонтальных шин матрицы задается блоком инхронизации 2, а коммутатор 7 переходит о строки на строку по сигналам кольцевого p3rHcfpa 3. Формула изобретения Устройство для 1феобразования телеграфного кода в видеокод, содержащее выходной формирователь сигналов и госледовательно соедшенные линей11ый накопитель, связанный с блоком синхронизации, кольцевой регистр дешифратор кода, коммутатор и матричный запоминающий блок, причем к управляющему входу кольцевого регистра подклк чен другой выход блока синхронизации, отличающееся тем, что, с целью повышения его быстродействия, в схему введены коммутатор строк, кольцевой счет чик и элемент ИЛИ, при этом дополнител1г-. иый выход кольцевого регистра через коммутатор строк подключен к одной группе входов матричного запоминающего блока, к другой группе входов которого подключены выходы кольцевого счетчика, я выходы матричного запоминающего подключены через элемент ИЛИ ко входу выходного формирователя сигналов, кроме того, к управляющим входам коммутатора строк и кольце вого счетчика подключены соотвьтственно до полнительные выходы блока синхронизации. Источники информации, -во внкмание при экспертизе. 1.Патент США N 37О5953, кл. 178-6.6А, 1972. 2.Выдревич М. Л. и др. З акогенерация по г;етоду полного растра в системе отображения ДИМ. Жури. Электронная промышленность, 1972, вып. 8 (J4), с. 51-53.

sOi

5

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1427412A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2012149C1 |

| Устройство для ввода информации | 1978 |

|

SU742918A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1472942A1 |

| Устройство для сопряжения телеграфных каналов с электронной вычислительной машиной | 1982 |

|

SU1067494A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

Авторы

Даты

1977-08-05—Публикация

1975-12-01—Подача